нагрузочной способностью усилителя мощности.

В предлагаемом устройстве смена информации на любом из выходов элемента памяти пре.цы,аущей группы произойдет

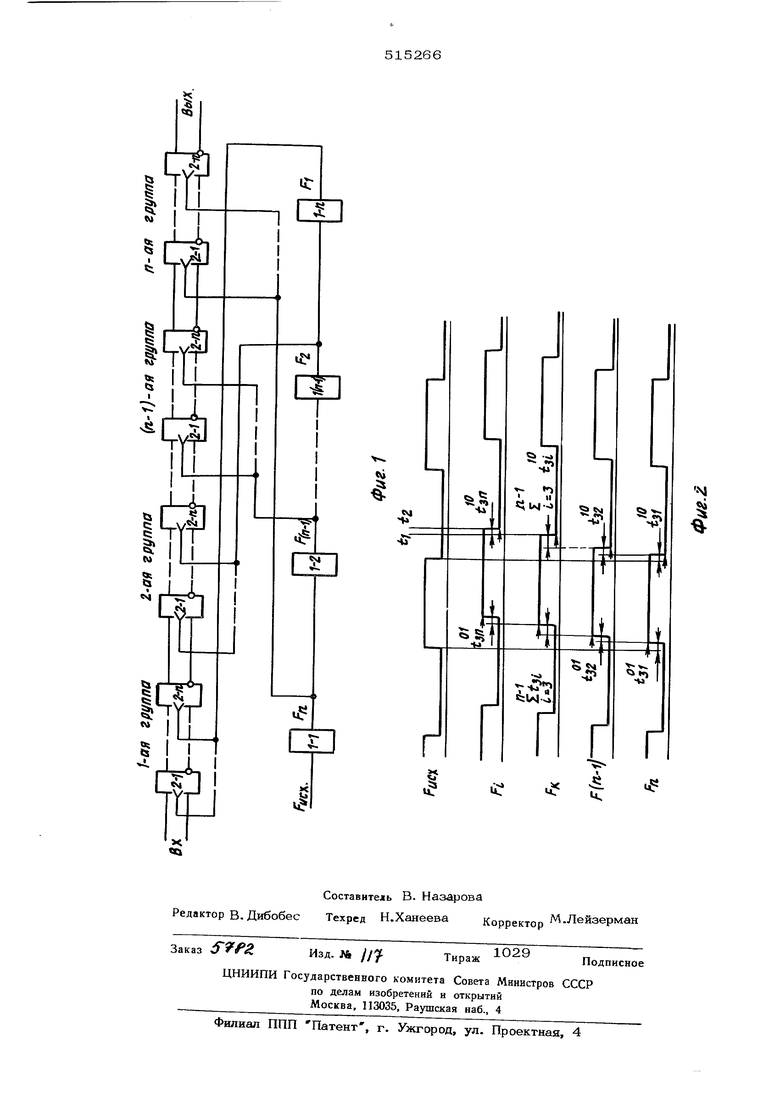

обязательно в момент времени, когда на синхронизирующих входах элементов памяти последующих групп имеется потенциал, соответствзтопшй уровню логического нуля что исключает ложную запись информации с пре.цы,аущих групп элементов памяти на последующие, т. е. обеспечивает устойчивое функционирование однотактных элементов памяти. Это поясняется временной диаграммой, приведенной на фиг. 2, где

F. 1 F . F FV, - сигналы на выходах t k и-f n

соответствующих усилителей мощности;

.01 01

а- 5 31 величины за,цержек положителных фронтов тактовых импульсов, синхро- низирующихf -ую и -ую группы

элементов памяти;

,10 ,10

Г ои ; s иы за,цержек от рицательных фронтов тактовых импульсов, синхронизирующихft -ую и I- ую

группы элементов памяти.

Смена информации на выходах t -ой группы элементов памяти начинается в момент времени „, смена уровня

тактового импульса вП -ой последовательности, синхронизирующей последующую группу элементов памяти, произойдет в момент времениL ; промежуток

времениt - t опрепеляется временем переключечияt -го усилителя

мощности.

Если у усилителей мощности не оговорены значения минимальных времен переключения, т. е, можно считать, что это время стремится к нулю, то устойчивость работы предлагаемого устройства не нару- щается- Следовательно, данное устройство позволяет обеспечить устойчивое функционирование однотактных элементов памяти и исключить из измеряемых параметров значения минимальных времен переключения как усилителей мощности, так и элементов памяти, что приводит к увеличению процента выхода годных элементов и уменьщению их стоимости.

Формула изобретения

Устройство преобразования входного сигнала для синхронизации однотактных устройств с разбитыми на группы элементами памяти, имеющих потенциальную систему связей и последовательно соединенные усилители мощности, отличающееся тем, что, с целью увеличения надежности, выход первого усилителя мощности по.цклкяен к синхронизирующим входам последней группы элементов памяти, выход второго усилителя мощности подключен к синхронизирующим входам предпоследней группы, а выход последнего усилителя мощности подсоединен к синхронизирующим входам первой группы элементов памяти.

N

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации однотактных дискретных устройств | 1976 |

|

SU736364A1 |

| Логический коммутатор | 1977 |

|

SU652553A1 |

| Устройство для моделирования оптимальной системы управления | 1985 |

|

SU1288729A1 |

| УСТРОЙСТВО ДЛЯ СИТУАЦИОННОГО КОНТРОЛЯ И УПРАВЛЕНИЯ | 1992 |

|

RU2041494C1 |

| Устройство для передачи и приема дискретных сообщений | 1983 |

|

SU1095220A1 |

| Генератор псевдослучайных кодов | 1980 |

|

SU951301A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| УСТРОЙСТВО АНАЛОГОВОГО ДАТЧИКА УГЛА ФАЗОВОГО СДВИГА МЕЖДУ НАПРЯЖЕНИЕМ И ТОКОМ | 2011 |

|

RU2492572C2 |

| Многоканальное устройство для обработки информации датчиков с частотным выходом | 1984 |

|

SU1196892A1 |

| Устройство для синхронизации памяти | 1988 |

|

SU1594516A1 |

Авторы

Даты

1976-05-25—Публикация

1972-09-12—Подача