Устройстио опгосптся к обллстп гнорпдпоп иычисльтелыюй техники.

Известны множнте.тьныс лстронства, используемые в AIJM, в которых сомножлтслн л |),1Ыат прсдста;;ле11Ь к jla/io напряженп, ГОКОВ, углов поворота и т. д. ij.

Однако такие уст)ппст1 а iiMCiOT линкую точность.

Этот недост;Г;ОК ст;,) -в )а:;рял.ль1х множительных устройствах. В );их многоразрядные числа представлены так 1;азызаемы}.л разрядными иекто)амн и разрядными латр;:цами, элементы которых модел:1руются некоторыми поотоянны.ми напряжениями 2.

Наибо.тее близким техническим решением к изобретению является множительное устрокетво, содержащее матрицу )ез11сторов, 1-саждый резистор которой одним зажимом соединен с одной из вертикальных и входом соответствующего операционного усилителя с резистором в цепи о&ратпой связи, а другим зажимом через унравляе.мый ключ - е соответствующей горизонтальной шиной, подключенной к входу устройства по опорному напряжению; управляющие входы ключей соединены с первым lHoгopaзpядпым входом устройства 3.

Такое устройство сложно в конструктивном отношении, так как для моделирования каждого разряда используются .однородные

сигналы (п частно., постоянные токи или напря/кепии). л.тя оГл)аботки требуются раздс, каца.;ы (при парал.тельноГ обработке ипфорл:аииц). Таким образом, ко;1я в каждом решающем

личестпо ооорудо

устройстве почти Л1п:ей;о

зависит от длииы

разрядной сетки. Це.ть изобрстеки

- упроп;с1п:о

Ko;iCTp Kluni множительного ycrpoiiCTna, н умножеjiHH многоразрядных чисел.

Для этого устройство СОДерЖ Г

выход)Ш1е

Иравл;1ел1:11е ключ;:, блок норма. зации и

блоки умножения, первый вход каждого из

которых соединен с выходом соответствующего опера-иониого } силителя, а второй вход - с вторым входо-; устройства. Выходы блоков умножения иодк.тючен) к входу блока нормализации, выходы которого связаны с выходами } стройства через 1 ыходные управляемые

ключи. Угфавляюии:е входы ключей подсоединены к входа.м стройства но опорному папряжению.

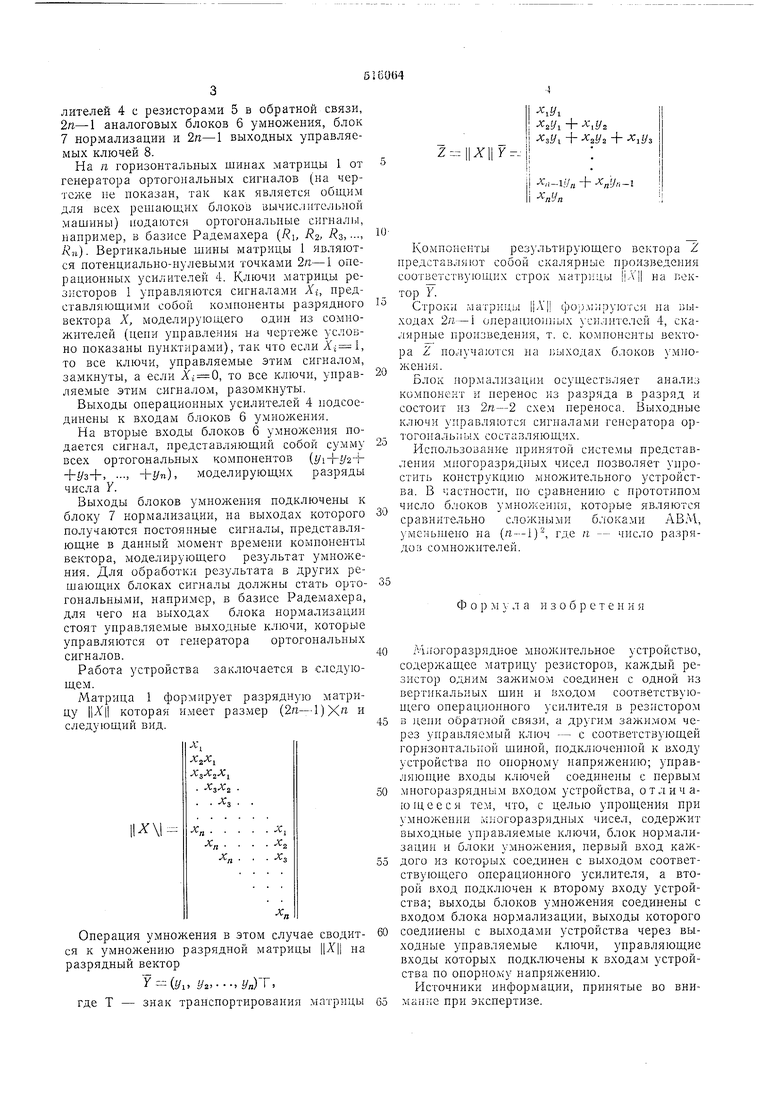

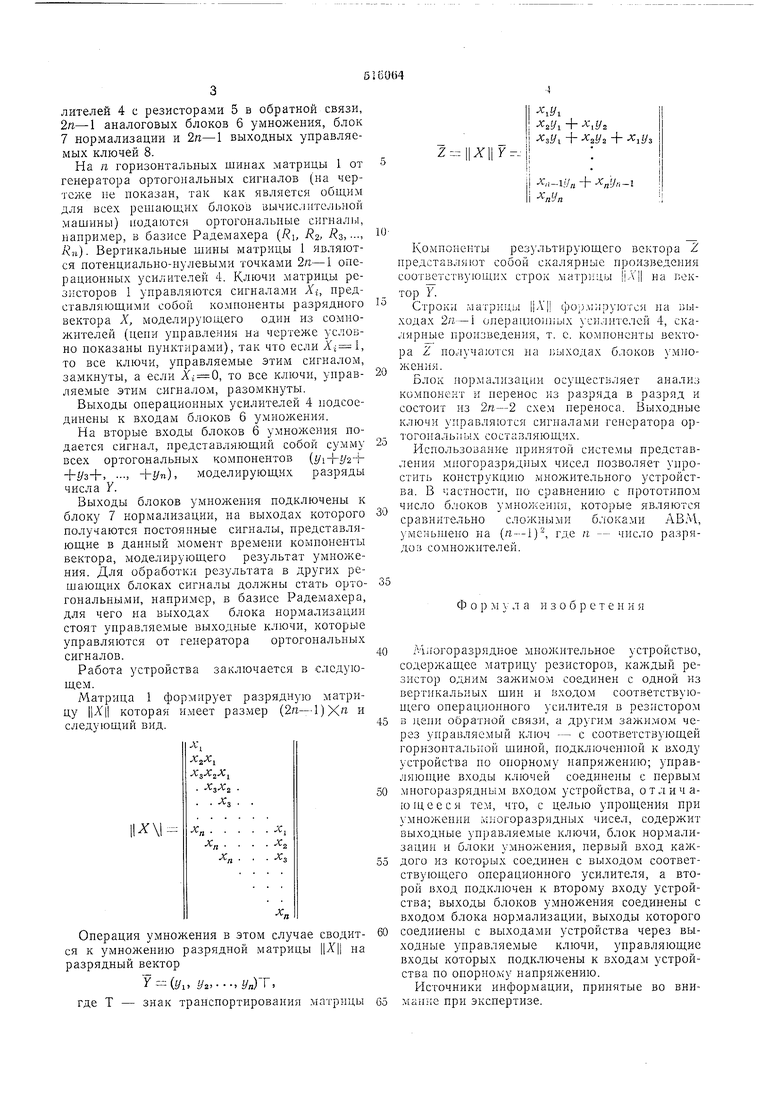

На чертеже приведена структурная ехема лшогоразрядного устройства, т. е. устройства,

реализующего операцию , где А , Y - /.-разрядные числа, изменяющиеся во вре.мени.

Устройство содержит матрицу 1 резисторов, состоящую из л- упр.вляемых ключей 2 и резисто)ов 3, а также 2/; -1 операционных ус ;лителей 4 с резисторами 5 в обратной связи, In-1 аналоговых блоков 6 умножения, блок 7 нормализации и 2/г-1 выходных управляемых ключей 8. На я горизонтальных шинах матрицы 1 от генератора ортогональных сигналов (на чертеже не показан, так как является общим для всех решающих блоков вычислительной машины) аодаются ортогональные сигналы, например, в базисе Радемахера (R, R, Кз, Rn) Вертикальные шины матрицы 1 являются потенциально-нулевыми точками 2/г-1 операционных усилителей 4. Ключи матрицы резисторов 1 управляются сигналами А ,, представляюш,ими собой компоненты разрядного вектора X, моделирующего один из сомножителей (цени управления па чертеже условно показаны пунктирами), так что если , то все ключи, управляемые этим сигналом, замкнуты, а если Ai 0, то все ключи, унравляемые этим сигналом, разомкнуты. Выходы операционных усилителей 4 подсоединены к входам блоков 6 умножения. На вторые входы блоков 6 умножения подается сигнал, представляющий собой сумму всех ортогональных комнонентов (г/1-г-.У2+ +УЗ+, -, +УП), моделирующих разряды числа Y. Выходы блоков умнол ения подключены к блоку 7 нормализации, на выходах которого получаются постоянные сигна„ты, представляющие в данный момент времени компоненты вектора, моделирующего результат умножения. Для обработки результата в других решающих блоках сигналы должны стать ортогональными, например, в базисе Радемахера, для чего на выходах блока нормализации стоят унравляемые выходные ключи, которые управляются от генератора ортогональных сигналов. Работа устройства заключается в следующем. Матрица 1 формирует разрядную матрицу X которая имеет размер (2п--1)Хг и следующий вид. Операция умножения в этом случае сводится к умножению разрядной матрицы X на разрядный вектор Y -(У, г/2,..., г/„)Т, где Т - знак транспортирования матрицы + л:,г/2 зУг + + Х,У, 2-|| 1|УX,,-li/, + .-l Компоненты результирующего вектора Z представляют собой скалярные произведения соот1;етст15ующих строк матрицы |л|| на пектор У. Строки матрицы ||л|| форлшруютси на выходах 2п-1 операпиоиных усилителей 4, скалярные произведения, т. е. компоненты вектора Z получаются на ;ыходах блоков умножения. Блок порл ализацни осуществляет анализ компонент и перенос из разряда в разряд и состоит из 2п-2 схем нереноса. Выходные ключи управляются сигналами генератора ортогоиаль;:ь х составляющих. Использование нринятой системы нредставления многоразрядных чисел нозволяет упростить конструкцию множительного устройства. В частности, по сравнению с нрототипом число блоков умножения, которые являются сравнительно сложными блоками АВМ, уменьшено на (п - 1) где п - чнсло разрядов сомножителей. Ф о р м у л а и 3 о б р е т е н и я Дигогоразрядное множнтельпое устройство, содержащее матрицу резисторов, каждый резистор одним зажнмом соединен с одной из вертикальных шии и входом соответствующего операционного усилителя в резистором в цепи обратной связи, а другим зажимом через управляемый ключ - с соответствующей горизонтальной шиной, нодключенной к входу устройства но онорному напряжению; управляюн1,ие входы ключей соединены с нервым многоразрядныл входом устройства, отличающееся тем, что, с целью унрощения при умножении многоразрядных чнсел, содержит выходные управляемые ключи, блок нормализации и блоки умножения, нервый вход каждого из которых соедннен с выходом соответствующего операционного усилителя, а второй вход подключен к второму входу устройства; выходы блоков умножения соединены с входом блока нормализации, выходы которого соединены с выходами устройства через выходные управляемые ключи, управляющие входы которых подключены к входам устройства по onopHOiMy напряжению. Источники информации, принятые во внимание при экспертизе.

1.Сучилин A. М. «Основы вычислительной техники, «Энергия, 1964.

2.Пухов Г. Е. Евдокимов В. Ф. «Об одном возможном принципе построения цифровых

. вычислительных машин ДАН СССР, т. 20б, JX9 2, 1973.

3. Авт. св. СССР До 395849, кл. G 06g 7/1Ь, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядное множительное устройство | 1974 |

|

SU524203A1 |

| Многоразрядный функциональный преобразователь | 1975 |

|

SU585506A1 |

| Многоразрядное множительное устройство | 1977 |

|

SU721837A1 |

| Многоразрядное суммирующее устройство | 1976 |

|

SU602967A1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1137479A1 |

| Генератор дискретных ортогональных функций | 1990 |

|

SU1756875A1 |

| Функциональный преобразователь | 1973 |

|

SU470820A1 |

| Многоканальное цифро-аналоговое множительное устройство | 1982 |

|

SU1049933A1 |

| Аналого-цифровое множительное устройство | 1980 |

|

SU883930A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО.:'.л t | 1973 |

|

SU395849A1 |

Хг

Xf

R, f

r

2-г.

I

/5 -е -/8

211-1 - 2п-1

Авторы

Даты

1976-05-30—Публикация

1974-12-31—Подача