(54) МНОГОРАЗРЯДНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

теля, а управляющие входы подключены ко второму многоразрядному входу устройства.

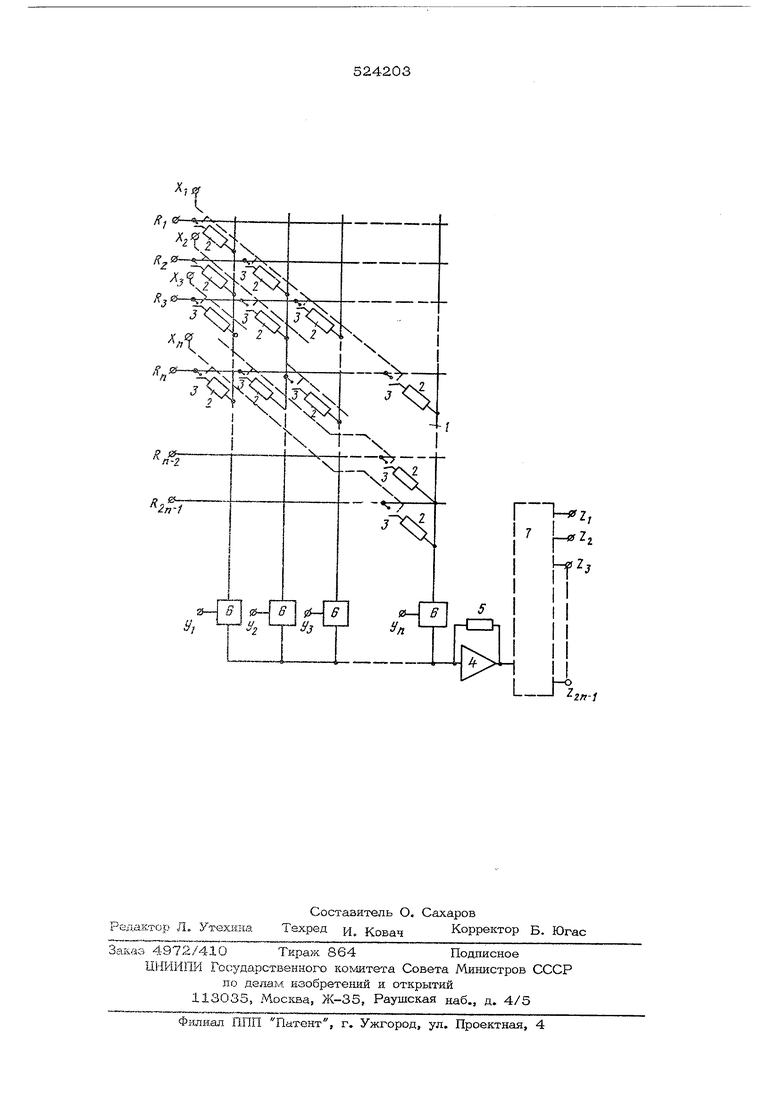

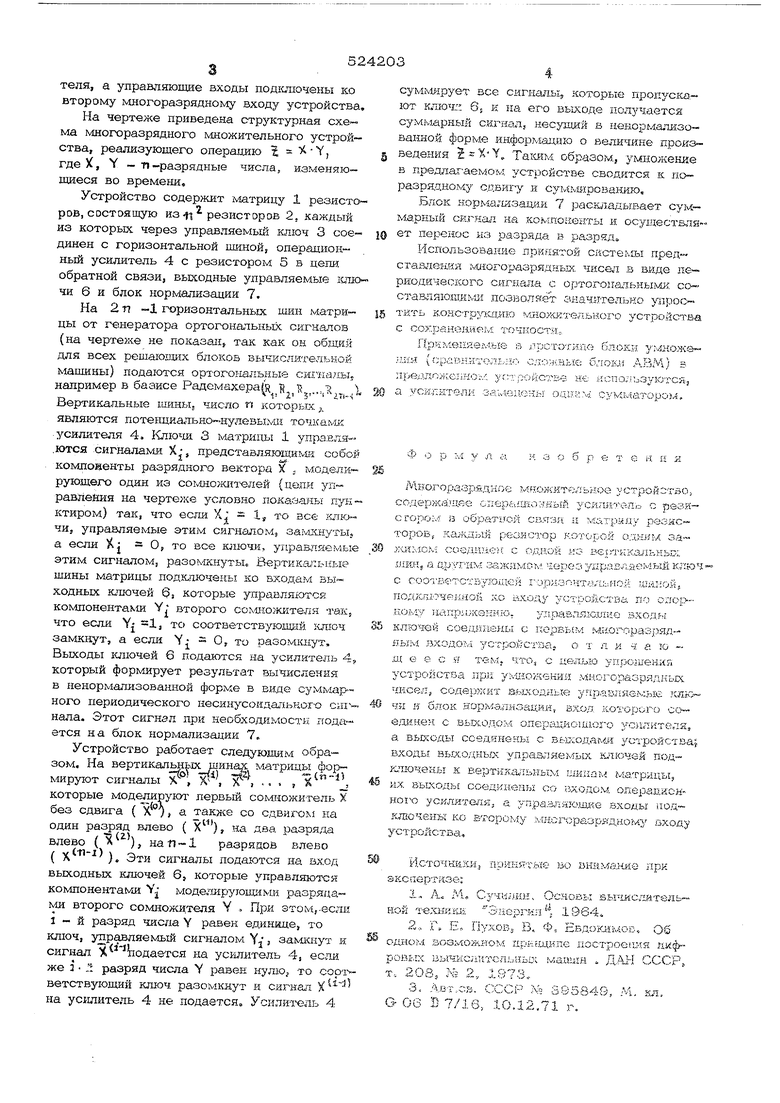

На чертеже приведена стрзктурная многоразрядного множительного устрой- ства, реализующего операцию 1 X Y, где X, Y - п-разрядные числа, изменяющиеся во времени.

Устройство содержит л атрицу 1 резисто ров, состоящую резисторов 2, каждый из которых через управляемый ключ 3 соединен с горизонтальной шиной, операционный усилитель 4 с резистором 5 в цепи обратной связи, выходные управляемые IOTJOчи 6 и блок нормализации 7.

На 2 п 1 1ч ризонтальных шин матрицы от генератора ортогональных скгн-апов (на чертеже не показан так как он общий для всех решаюышх блоков вычислительной машины) подаются ортогональные сигналы,, например в базисе Радемахера(.р..,, Вертикальные шины, число п которых ,. являются потенциально-нулевьичШ T04KavK: усилителя 4. Ключ 3 матрицы 1 управлл.ются сигналакш X, представляющим : собой компоненты разрядно1-х) вектора Х - модепирующего один из согушо/кит-елей (цели управлейия на чертеже условно показаны пунктиром) так, что X.J 1, то все- , управляемые этим сигналом, замкнуты. а если X.J О, то все ключи, управлявГч-аые этим сигналом, разомкнуты, Верткка;:ь п-ле шины матрицы подк,;аючеиы ко входам зы ходньш ключей Q, которые упраЕля4-этся компонентами Yr второго сок-ыгожителя так, что если YI 1, то соответствующий ключ замкнут, а есл11 У О, то разомкнут. Выходы ключей 6 подаются на усилитель 4 который формирует результат вычисления в ненормализованной форме в виде суммар-ного периодического несинусоидальког-о сш- нала. Этот сигнал при необходимости подается на блок нормализации 7,

Устройство работает следуюдшм образом. На вертикальньисшин матрицы формируют сигналы % °, Х , 1 , ... , которые моделируют первый сомножитель X без сдвига ( X ;, а также со сдвигом на один разряд влево ( ), на два разряда влево ( Х ), разрядов влево ( X ). Эти сигналы подаются на вход выходных ключей 6, которые управляются компонентами YJ моде/шрующими разрядами второго coшioждтeля V « При этом,.еслк 1 - и разряд числа Y равен единице, то ключ, управляемый сигналом Yj-, и сиг11ал X одается на усилитель 4, ес.ли же i разряд числа Y равен нулю, то copi- ветствующий ключ разомкнут и свгпап на ус шитель 4 не подается. Усилитель 4

cyMivOipyer все сигналы, которые пропускают ключ.:: 6, к на его вькоде получается суммарный сигнал, несущий в ненормал зо ванной форме информшхию о величине произведения Та, образом, умножение в гфедлаг-аемом устройстве сводится к поразрядному сдвигу и cy д fflpoвaнлю,

Блок корма.шзацй.и 7 расш;.адьгвает суммарный сигнал на кол-гиог-Т-енты и осуществляет перенос из разряда в разряд.

Использование прйяятой сйстек1Ы предсгавлекйя :-.дногоразрядных, чисел в виде ле риодического сигнала с ортого11алькы; хич ее-™ стааляююдм; позволяет значительно упростить K.o,4CTp;;,aai.Hso -ко кктельк(сго устройства с сохранением точкости,

Иргменяемые s лрстоткпо блоки умноже ;ш): (сргвнательно сложные б/гокл АВМ) з уг:тройсгве не йспо;)ьзуются, ,1-,-1.еиеньг оци;:ч сумыаторогл.

о р

Многоразряд1 ое м южктельное у строй- во, содержанее спер 1йно;- ный усялда-еп с резисгорО1-.« в обратоой связи ц матрняу резисторов, каждый резистор которой одним за.жимом соедкнен с одной из вер:гнка/1ькьи;: шш1, а другим ;зажнмот..- юреоунраБЛяомьлйключс соо1,ветствую.щей гориапчтал.;::яой i.a.iUjK. по;(КЛ1ОчекяоЁ хо входу уст&ойстза по опорному иапр::ихегдкю. улравлзюх кю ключей сое/ипекы с ггорвьЕм к когоразрядяым входом устройства, о т я и -,: а ю - щ е е с я тем. что, с целью упрсшениа устройства лрд1 у.1нокекия многоразрядных чксел содержит выходнью ynpaBJUieN hie ;спю чя я блок кормэлнзадйн, вход которого соединен с BbDc.OfiOM олерадиоиаого усилителя, а выходы сседяненьл с Быг:одар.4и ус1ройсава; входы вьжоднь.сх ynpas,riHeMbix к,чючей под™ к.1ючекы к вертикальным ишнам матрицы, их вьтхо/ы соедккеаь со входом операдйснного усклителя. а управляющие входы подключеин ко второму .чногоразряднок) входу

ИстоШйхИз принятые во вш1манйе при эксаертязе:

1, А Мо Суч(1;1ии, Основы вы шслйтель- ной i exKKai Энергия Н 1964

2. Г Е riyxoBj В, Ф, Евдокимов. Об одном возможном прйЁЩНпе достроецкя мкф-ровых Бьгчксантсльяьс; ыаииш ДМ-; СССР т. 2OSj № 2, 1973,

3, Авт,св, СССР Л5 S85S49, М. кл, G 06 В 7/16, 10.12,71 г.

:

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядное множительное устройство | 1974 |

|

SU516064A1 |

| Многоразрядный функциональный преобразователь | 1975 |

|

SU585506A1 |

| Многоразрядное суммирующее устройство | 1976 |

|

SU602967A1 |

| Многоразрядное множительное устройство | 1977 |

|

SU721837A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Устройство для решения систем алгебраических уравнений | 1977 |

|

SU714405A1 |

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

| НЕЛИНЕЙНЫЙ МНОГОРАЗРЯДНЫЙ СУММАТОР | 1971 |

|

SU419907A1 |

| Следящий функциональный преобразователь | 1976 |

|

SU634308A1 |

| УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1972 |

|

SU357565A1 |

HZ,

IИг„.,

Авторы

Даты

1976-08-05—Публикация

1974-12-31—Подача