1

Изобретение относится к устройствам автолгатики и измерительной техники и предназначено для использования в коммутаторах измерительных сигналов.

Известны коммутаторы, содержащие измерительные ключи, которые соединяют соответственно четные и нечетные измерительные входы с двумя выходами кол1мутаторов, счетчики каналов и групп каналов, соединенные носледовательно по счетным входам, денп1фраторы каналов н групп каналов, входы которых соединены с выходами соогветствующих счетчиков, а выходы соединены с матрицей включения выбранного канала в выб1)аниой группе, и задаюпдий генератор.

В известных коммутаторах возможность изменения числа полюсов коммутации отсутствует вообще или может производиться только непосредственно изготовителем по заказу потребителя.

Цель изобретения - автоматизация изменения числа нолюсов коммутации и тем самым - расширение функциональных возможностей коммутатора.

Это достигается тем, что в предлагаемом коммутаторе выходы дешифратора групп каналов соединены с ирограммным устройством, выход которого соединен с управляющим входом дешифратора каналов и входом первого элемента «И, второй вход которого соединен

с выходом задающего генератора, а выход - с входом элемента «ИЛИ, и входом инвертора, а выход инвертора соединен с унравляющим входом дополнительного ключа, который

включен между выходами коммутатора, входом второго элемента «И, второй вход которого соединен с выходом задающего генератора, а выход - со счетным входом триггера, н входом третьего элемента «И, второй вход

которого соединен с выходом триггера, а выход - с вторым входом элемента «ИЛИ, выход трнггера соединен с входом дешифратора каналов, а выход элемента «ИЛИ - с входом счетчика каналов.

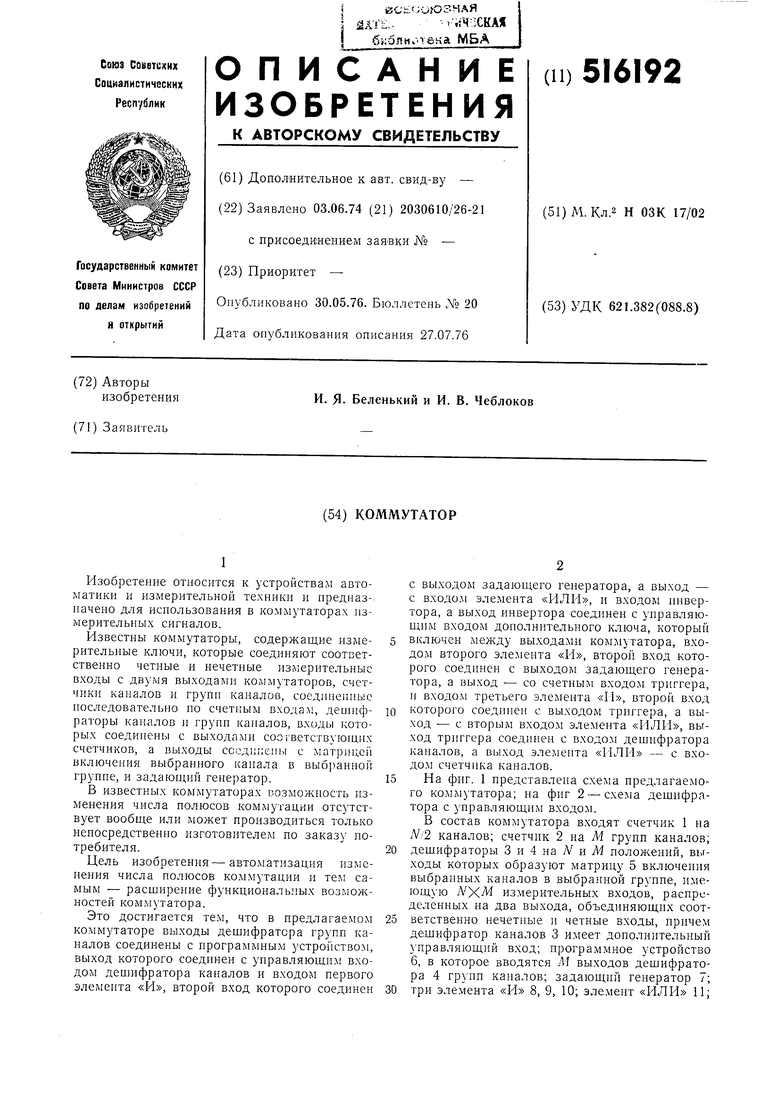

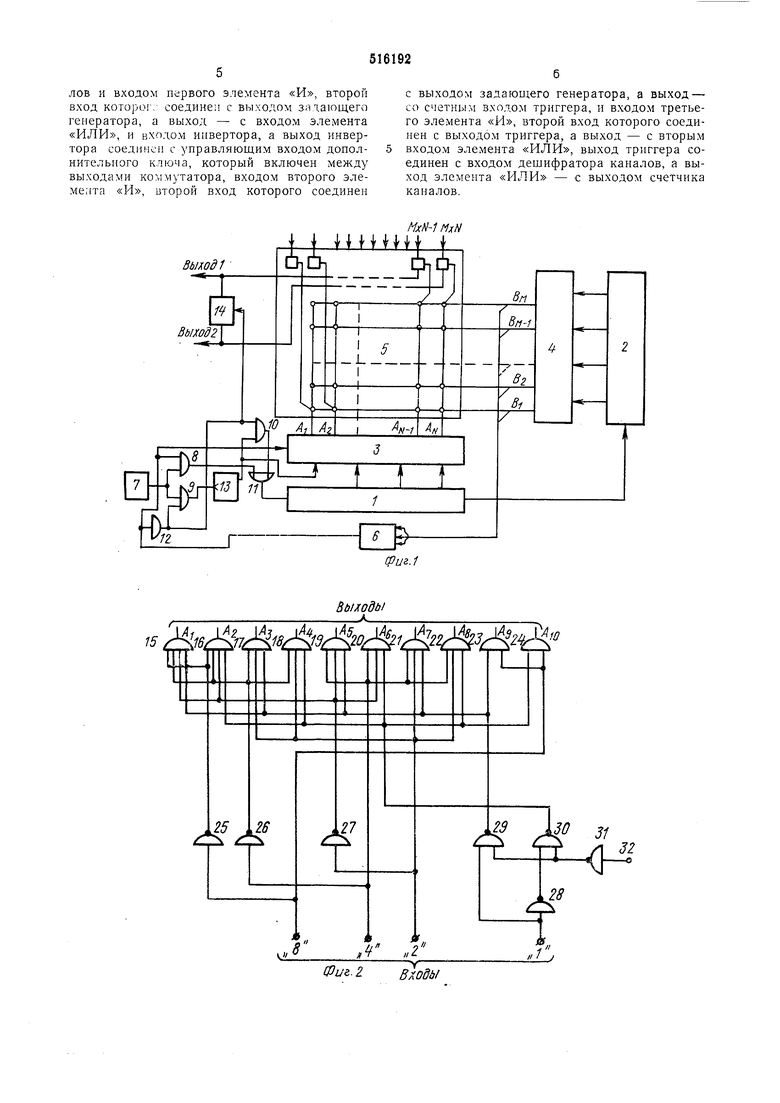

На фиг. 1 представлена схема предлагаемого коммутатора; на фиг 2 - схема дешифратора с унравляющим входо: 1.

В состав коммутатора входят счетчик 1 на jV;2 каналов; счетчик 2 на М групп каналов;

дешифраторы 3 и 4 на Л и М положений, выходы которых образуют матрицу 5 включения выбранных каналов в выбранной группе, имеющую Л/Х измерительных входов, распределенных на два выхода, объеднняющих соответственно нечетные и четные входы, иричем дещифратор каналов 3 имеет дополнительный правляющий вход; программное устройство 6, в которое вводятся М выходов дешифратора 4 каналов; задающий генератор 7;

три элемента «И 8, 9, 10; элемент «ИЛИ И;

инвертор 12; счетный триггер 13 и дополнительный ключ 14, аналогичный измерительНЫ1М ключам коммутатора и объединяющий два выхода матрицы 5, причем выход программного устройства 6 соединен с входом инвертора 12, управляющим входом дещифратора 3 и входом элемента «И 8, второй вход которого соединен с выходом задающего генератора 7, а его выход - с одним из входов элемента «ИЛИ 11, выход инвертора 12 соединен с управляющим входом дополнительного ключа 14, входом элемента «И 9, другой вход которого соединен с выходом задающего генератора 7, а его выход-со счетным входом триггера 13; выход инвертора соединен также с входом элемента «И 10, другой вход которого соединен с выходом триггера 13, а выход - с вторым элементом «ИЛИ И, выход триггера 13 соединен с входом дещифратора 3, а выход элемента «ИЛИ 11 - с входом счетчика каналов 1.

Если триггер 13, счетчики 1 и 2 находятся в исходном состоянии, то дещифраторы 3 и 4 выдают управляющие сигналы по первым выходам. Соответственно выбирается первый канал первой группы. Кроме того, управляющий сигнал дещифратора 4 поступает также в программное устройство 6. В том случае, если для первой группы каналов не программируется увеличение числа полюсов коммутации, управляющий сигнал на выходе устройства 6 соответствует «нулевому (низкому) логическому уровню. Ири этом элемент «И 8 закрыт, элементы «И 9 и «И 10 открыты от инвертора 12, который выдает также сигнал на заключение ключа 14, объединяющего выходы коммутатора; выход задающего генератора 7 подключен через элемент «И 9 на вход счетного триггера 13, а выход последнего подключен через элементы «И 10 и «ИЛИ 11 на вход счетчика 1. Импульсы генератора 7 считаются триггером 13 и счетчиком 1, при этом, дещифратор 3 поочередно выдает- управляющие сигналы на выбор всех каналов первой группы. При выдаче сигнала переноса па счетчик 2 дещифратор 4 переходит во второе положение. В случае, если для второй группы каналов увеличение числа полюсов коммутации также не запрограммировано, работа повторяется аналогичным образом для второй группы каналов.

В случае, если для второй группы каналов запрограммировано увеличение числа полюсов коммутации, программное устройство 6 выдает управляющий сигнал, соответствующий «единичному (высокому) логическому уровню. При этом открывается элемент «И 8, от инвертора 12 закрываются элементы «И 9 и 10, и генератор 7 через элементы «И 8 и «Р1ЛИ И подключается непосредственно на вход счетчика 1, размыкается ключ 14, разъединяя выходы коммутатора, а наличие сигнала на управляющем входе дещифратора 3 обеспечивает включение сразу двух выходов дещифратора - первого и второго.

Дещифратор с управляющим входом (фиг. 2) показан на примере дещифратора двоично-десятичного кода 8421. Дещифратор состоит из элементов 15-24, инверторов 25- 28 и отличается от известных наличием двух элементов «И-НЕ 29 и 30, которые по одному входу через инвертор 31 связаны с управляющим входом 32. Наличие на управляющем входе «нулевого (низкого) логического уровня через инвертор 31 открывает элементы 29-30, и дещифратор как обычно на каждую комбинацию двоично-десятичного кода 8421 отрабатывает по одному из выхо дов с первого по десятый.

Наличие же на управляющем входе «ед1 ничного (высокого) логического уровня через инвертор 31 закрывает элементы 29-30 и создает на их выходах также «единичный логический уровень. Это приводит к одновременному включению сразу двух выходов дещифратора (иечетного и четного) в зависимости от комбинации по входам «8, «4, «2, «1.

В связи с изложенным выще при выдаче

управляющего сигнала от программного устройства 6 происходит включение сразу двух выходов дещифратора - первого и второго. Таким образом, происходит включение сразу двух измерительных ключей коммутатора, соответствующих измерительному каналу с удвоенным числом полюсов коммутации. Так как каждый измерительный ключ может иметь несколько полюсов коммутации (например, один, два, три), то общее количество полюсов может составить соответственно два, четыре, щесть.

Далее в процессе счета подключается последующие выходы дещифратора 3, пока счетчик 1 не выдаст снгнала переноса и счетчикf

не перейдет в очередное положение.

Далее работа продолжается аналогичны. образом Б соответствии с программой.

Таким образом, в процессе опроса каналов обеспечивается автоматическое удвоение числа переключаемых полюсов в измерительных каналах прп условии уменьщения в два раза числа каналов данной группы.

Фор м у л а и 3 о б р е т е н и я

Коммутатор, содер}кащий измерительные ключи, которые соединяют соответственно четные и нечетные измерительные входы с двумя выходами коммутатора, счетчики каналов и групп каналов, соединенные последовательпо по счетным входам, дещифраторы каналов и групп каналов, входы которых соединены с выходами соответствующих счетчиков, а выходы соединены с матрицей включения выбранного канала в выбранной группе,

и задающий генератор, отличающийся тем, что, с целью автоматизации изменения числа полюсов коммутации, выходы дещифратора групп капалов соединены с програмным устройством, выход которого соединен

с управляющим входом дещифратора кана

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1977 |

|

SU705677A1 |

| Коммутатор | 1981 |

|

SU976499A1 |

| Коммутатор | 1981 |

|

SU974579A1 |

| Коммутатор | 1981 |

|

SU976500A1 |

| Коммутатор | 1981 |

|

SU1001470A1 |

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| Коммутатор | 1985 |

|

SU1272494A1 |

| Программируемый контроллер | 1989 |

|

SU1741100A1 |

| Коммутатор | 1985 |

|

SU1265990A2 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

Авторы

Даты

1976-05-30—Публикация

1974-06-03—Подача