1

Изобретение относится к вычислительной технике и может быть применено, например, в цифровых вычислительных машинах, в цифровых дифференцирующих машинах и в специализированных цифровых устройствах, построенных на интегральных схемах.

Известно дифференцирующее устройство, содержащее коммутаторы и блок управления. Известное устройство характеризуется невысоким быстродействием при вычислении производной любого порядка от функции, представленной многочленом, и имеет большой состав анпаратуры.

Целью изобретения является повышение быстродействия устройства и упрощение вычисления производиой любого порядка от функции, представленной многочленом, и упрощение устройства. Это достигается тем,что в описываемое устройство введены регистр операнда, регистр окончательного результата, блоки элементов «ИЛИ, формирователи, регистры коэффициентов и сумматоры, вход каждого из которых подключен к выходу соответствующего коммутатора, информационные входы которых соединены с выходами соответствующих блоков элементов «ИЛИ и регистра операнда, выходы каждого регистра коэффициентов и каждого формирователя подключены к управляющим входам соответствующих коммутаторов, управляюнще входы регистров коэффициентов, регистра окончательного результата, сумматоров, входы блоков элементов «ИЛИ и первые и вторые входы формирователей соединены с соответствующими выходами блока управления, третьи входы i-x формирователей соединены со вторыми выходами (1-1)-х формирователей, четвертые входы - подключены -к выходам i-x сумматоров, пятые входы - к выходу младшего разряда регистра операнда, вход регистра окончательного результата подключен к выходу я-го сумматора.

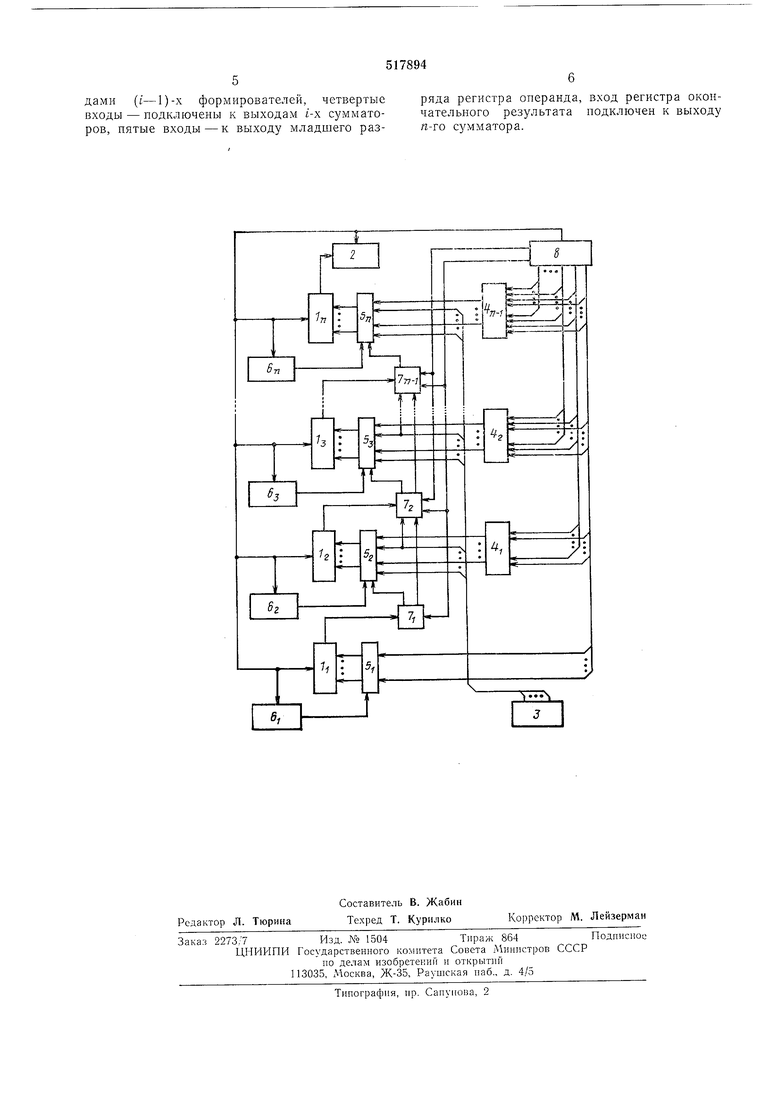

На чертеже приведена структурная схема описываемого устройства.

Оно содержит сумматоры Ь-In (п-степень многочлена), регистр 2 окончательного результата, регистр операнда 3, блоки 4i-4n-i элементов «ИЛИ, коммутаторы 5,-5п, регистры коэффициентов 6i-6п, формирователи 7i-7n-i и блок управления 8. Входы сумматоров соединены с выходами соответственно коммутаторов 5;-5,г, а выход сумматора In подключен ко входу регистра 2 окончательного результата. К одним информационным входам коммутаторов 52-5п подключены выходы соответственно блоков 4 -4«-i элементов «ИЛИ, а к другим - выходы регистра операнда 3. Выходы младших разрядов регистров коэффициентов 6i-6п соединены с первыми управляющими входами соответственно коммутаторов 5i-5п, а ко вторым управляющим входам коммутаторов 52-5п подключены выходы соответственно формирователей -7п-1. Первый выход блока управления 8 соединен с управляющими входами сумматоров , регистров коэффициентов GI-6„ и регистра 2 окончательного результата. Второй выход блока управления 8 подключен к первым входам формирователей 7i- , а третий-ко вторым входам формирователей 72-7„ 1, к третьим входам которых подключены вторые выходы соответственно формирователей 7i-7п 2- Выходы младщих разрядов сумматоров h-In-i соединены с четвертыми входами соответственно формирователей 7i-7п ь а к пятым входам формирователей 72-7,г-1 подключен выход младшего разряда регистра операнда 3. Отдельная группа выходов блока управления 8 образует п кодовых щин. Первая кодовая щина подключена ко входам коммутатора 5i в соответствии с двоичным кодом числа п. Ко входам г-х блоков 4i-4„ 1 элементов «ИЛИ (i - индекс блока) каждая k-я (, 2, ..., п) кодовая шина подключена в соответствии с двоичныk-iми кодами, равными П (« - i + У) . Регистр

операнда 3 и регистры коэффициентов имеют по т разрядов, где т - разрядность операнда. Сумматоры h-1«, имеющие индексы /, содержат по k двоичных разрядов,

Iопределяемых из соотношения //SslogariH -У)

Формирователи могут быть построены в соответствии с переключительными функциями вида

gi®hi-i-c,

где hi - функции, реализуемые формирователями 7i-7n-i с индексами /; gi - цифры младших разрядов сумматоров с индексами i; йг-1 - функции, реализуемые формирователями 7i-7п 2 с индексами i-1; с - цифра младшего разряда регистра операнда 3.

Пусть необходимо вычислить производную k-TO порядка (, 2, ..., п) Б точке X XOOT

п

функции, представленной многочленом .

i-O

Перед началом вычислений операнд XQ записывается в регистр операнда 3, коэффициенты uii, ait+i,- ..., an записываются соответственно в регистры коэффициентов би, 6п-ь , 6;,. Сумматоры li-In и регистры коэффициентов 6 -G/i-i устанавливаются в нулевое состояние, а k-u триггер настройки, входящий в состав блока управления 8, устанавливается в «единичное состояние. В процессе вычисления блок управления 8 последовательно во времени вырабатывает управляющие сигналы

7, Т2, ТЗ и Г4. При наличии единицы в й-м триггере настройки блок управления 8 выдает управляющий сигнал Т1 только на k-ю кодовую шину. При этом коды с выходов блоков 4|-4п-1 элементов «ИЛИ через коммутаторы 52-5,1 передаются соответственно в сумматоры ,г, где осуп1ествляется их суммирование с содержимым сумматоров Ь-In, а процессом передачи кодов в сумматоры

управляют младщие разряды соответственно регистров коэффициентов 62-6и. При вычислении первой производной но сигналу Т1 осуществляется также прием двоичного кода числа п в сумматор 1 через коммутатор БЬ

управляет которым младший разряд регистра коэффициентов 6. По сигналу Т2 в формирователях 72-7п-1 формируются и запоминаются значения функций hi, по сигналу ТЗ сформированные функции /г, управляют передачей кода регистра операнда 3 в сумматоры Ь-1и, где осуществляется суммирование этого кода с содержимым сумматоров Ь-In-Затем по сигналу Г4 выполняется иравый сдвиг на один разряд содержимого сумматоров Ь-

-1„, регистров коэффициентов 6i-6п и регистра 2 окончательного результата. При сдвиге очередная цифра результата с выхода младшего разряда сумматора In переписывается в старший разряд регистра 2 окончательного результата. На этом заканчивается один цикл вычислений.

Для получения полного результата необходимо выполнить lh+(n-k)m циклов, после чего результат записывается в т младших разрядах сумматоров U и в регистре 2 окончательного результата.

Формула изобретения

Дифференцирующее устройство, содержащее коммутаторы и блок управления, отличающееся тем, что, с целью повышения

быстродействия устройства .и упрощения вычисления производной любого порядка от функции, представленной многочленом, в него введены регистр операнда, регистр окончательного результата, блоки элементов

«ИЛИ, формирователи, регистры коэффициентов и сумматоры, вход каждого из которых подключен к выходу соответствующего коммутатора, информационные входы которых соединены с выходами соответствующих блоков элементов «ИЛИ и регистра операнда, выходы каждого регистра коэффициентов и каждого формирователя подключены к управляющим входам соответствующих коммутаторов, управляюшие входы регистров коэффициентов, регистра окончательного результата, сумматоров, входы блоков элементов «ИЛИ и первые и вторые входы формирователей соединены с соответствующими выходами блока унравления, третьи входы г-х

формирователей соединены со вторыми выходами (i-1)-х формирователей, четвертые входы - подключены к выходам i-x сумматоров, пятые входы - к выходу младшего разряда регистра операнда, вход регистра окончательного результата подключен к выходу я-го сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравлений | 1974 |

|

SU526905A1 |

| Дифференцирующее устройство | 1974 |

|

SU516041A1 |

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

| Устройство для вычисления многочленов вида @ @ | 1978 |

|

SU868767A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для вычисления интегра-лОВ | 1976 |

|

SU840901A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

Авторы

Даты

1976-06-15—Публикация

1974-10-09—Подача