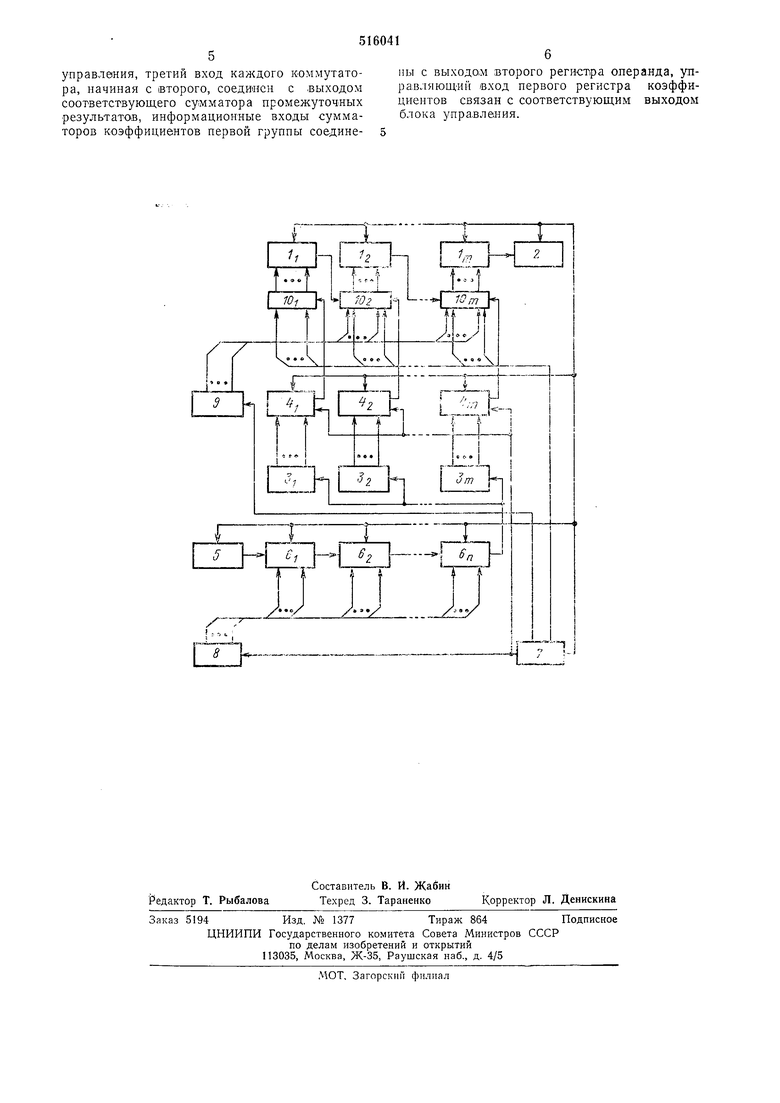

фициентов uf , блок 7 управления, регистр 8 операаада х, регистр 9 операщда у -и коммутаторы lOi, Юг, ..., 10,„. Регистры 5, 8, 9 и Зь За, ..., 3„ имеют по /г разрядов (k - разрядность операндов), сумматоры 4i, 42, ..., 4 „ коэффициентов bj - по k + разрядов, сумматор li первого промежуточного результата - / + 1 разрядов (I logzfn), сумматары Ь, 1з, , 1т соответственно /-х промежуточных результатов (/ 2, 3, ..., т) - по k + j ,+ 1 разрядов, сумматоры 6i, 62, ..., 6„ коэффициентов а,- - по + я - t + 1 разрядов, а регистр 2 - k (п + т) - т + I разрядов. Выходы регистра 9 операида у через ком1мутаторы 102, Юз, ..., 10„ подключены соответственно ,к входам сумматоров 12, 1з, ..., 1 промежуточных результатов со сдвигом влево «а один разряд. Через другие входы коммутаторов 10, 102, , Ю к входам соот)ветстщбн«о сумматоров li, Ь, .... т промежуточных результатов подведена кодовая шина блока управления 7. К входам каждого сумматора 1у /-го промежуточного результата кодовая шина подведена в соответствии с /наличием едияиц в двоичных кодах показателей степени равных т + I - / и сдвинутых на / - 1 разрядов влево. Выходы регисцра 8 оюераида х подведены к входам сумматоров бь 62, ..., 6 коэффициентов at со сдвигом на оди-н разряд влево.

Устройство работает следуюш,им образом.

Перед началом вычисления выражения

(5пт

(Е aix- 2 bjijJ}

У

при заданных значениях х и // коэффициент а „ записывается в регистр 5, а коэф|фициенты un-i , cin-z , . , «О записываются в k + 1 старшие разряды соответственно сумматоров 6ь б2, ..., 6„. Коэффициенты &„„ Ьш-ь ..., 1 записываются соответствен-но в регистры 3i, 32, ..., 3,„, операнд х - в регистр 8, а операнд у - в регистр 9. Сумматоры 1, Ь, ..., 1т промежуточных результатов сумматоры 4, 42, . .., 4 коэффициентов bj и регистр 2 окончательного результата устанавливаются в нулевое состояние. В процессе выч-исления блок управления 7 в каждом цикле последовательно вырабатывает управляюШИе сигналы TI, Т, Т и Т. Управляющий сигнал Г поступаег на цепи выдачи 1кода регистра 8 операнда л; и на цепи приема кода сумматоров 4i, 42, . .., 4 „, коэффициентов bj. При этом цифры младших разрядов сумматоров 6, 62, ..., . коэффициентов а,- управляют сложением кода операнда X, записанного в регистре 8 этого операнда, с содержимым соответственно сумматоров 62, 6з6„ Коэффициентов а; , а цифры

младшего разряда сумматора 6 управляют сложением кодов коэффициентов bj с содерЖимьш сумматоров 4i, 42, .. ., 4„ этих коэффициентов. Управляющий сигнал TZ поступает на кодовую шину показателей степени, в

результате чего нро 1сходнт кодоа показателен сте-нонн с содержимым сумматоров li, Ь, ..., 1,,, промежуточных результатов, а процессом сложения управляют младшие разряды сумматоров 4i, 42, ..., 4,„ .

Управляющий снглал Т поступает на цепц выдачи кода регистра 9 опера 1да у. При этом код регистра 9 операнда у передается через коммутаторы 102, 10з, ..., 10,„ в сумматоры 12, 1з, .-, IOT промежуточных результатов. Процессом передачи кода операнда у в сум-маторь1 Ь, Ь, , 1,« промежуточпых результатов управляют младшие разряды соответственно сумматоров li, Ь, ...,

1 m-i. Затем по сигналу Ti осуществляется сдвиг вправо на один разряд содержимого регистра 2 окончательного результата, регистра 5 коэффициента а„, а также сумматоров li, l2, ..., 1,„ промежуточных результатов и сумматоров 4ь 42, .. . , 4„ коэффициентов Ь J .

При сдвиге очередная цифра результата с выхода младшего разряда сумматора 1 ,„ П1-ГО промежуточного результата переписывается в регистр 2 окончательного результата. Па этом заканчивается один цикл вычислений. Для получения нолного результата необходимо выполнить k (п + т) + п + I - 1 циклов, после чего младшие разряды результата паходят в регистре 2 окончательного результата, а старшие разряды - в сумматоре 1 „, /п-го нромежуточного результата.

Формула изобретения

Дифференцирующее устройство, содержащее регистры коэффициентов, сумматоры промежуточных результатов, вход каждого из которых подключен к выходу соответствующего коммутатора, регистр операнда, выход которого нодключен к информационным входам соответствующих коммутагоров, регистр окончательного результата, вход которого соединен с выходом ш-го сумматора промежуточных результатов, блок управления, выходы которого подключены соответственно к управляющим входам сумматоров промежуточных результатов, регистра окончательного результата и регистра опера-нда, отличающееся тем, что, с целью повышения быстродействия при вычислении частной производной от произведения двух функций, представленных многочленами, в него введены второй регистр операнда и сумматоры коэффициентов, унравляющие входы которых подключены к соответствующим выходам блока управления, выход первого регистра коэффициентов через последовательно соединенные сумматоры коэффициентов .первой группы подключен к входам регистров коэффициентов, начиная с второго регистра, выход каждого из которых через соответствующий сумматор коэффициентов второй группы подключен к одному ич входов соответствующего коммутатора, другой вход которого соедннен с выходом блока управления, третий вход каждого коммутатора, начиная с второго, соедиисн с выходом соответствующего сумматора промежуточ ных результатов, информационные входы сумматоров коэффициентов первой группы соедине- 5 ны с выходо м второго регистра операнда, управляюЩИй вход первого регистра коэффициентов связан с соответствующим выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференцирующее устройство | 1974 |

|

SU517894A1 |

| Устройство для решения дифференциальных уравлений | 1974 |

|

SU526905A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для перемножения многочленов | 1973 |

|

SU495663A1 |

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| Устройство для возведения в квадрат и умножения | 1979 |

|

SU857975A1 |

Авторы

Даты

1976-05-30—Публикация

1974-10-15—Подача