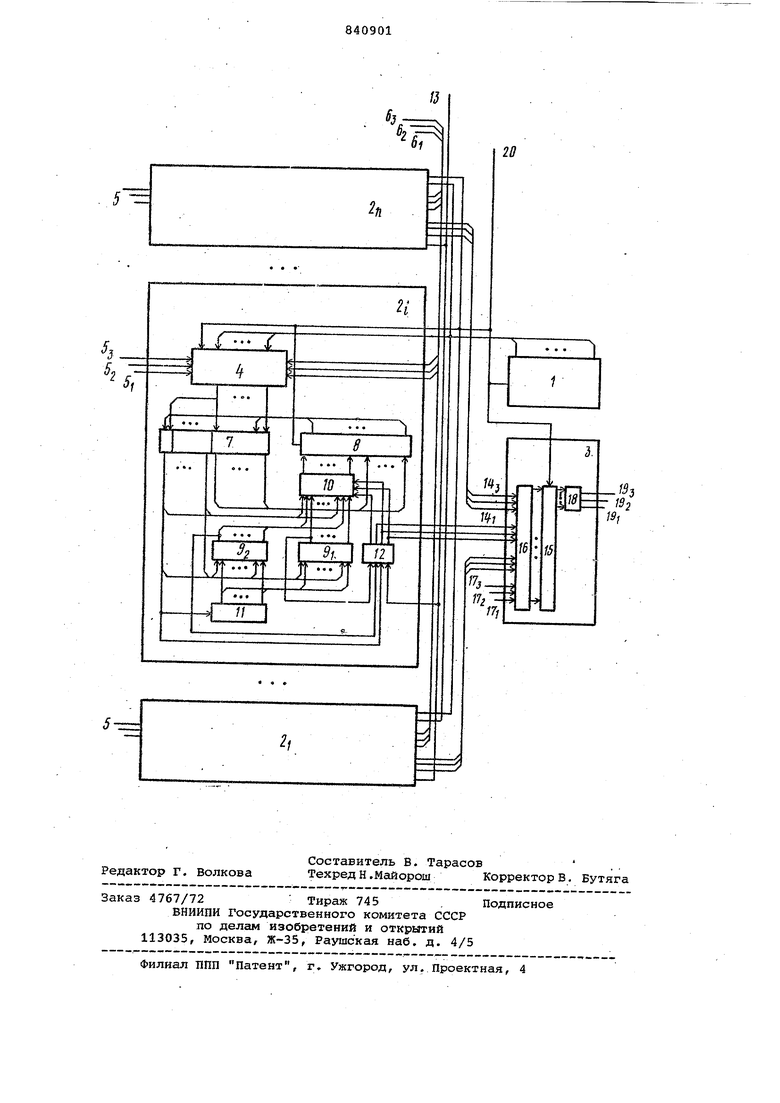

Изобретение относится к вычислительной технике и может быть применено в цифровых моделирующих устрой ствах для вычисления интеграла на интервале Го, XJ от функции, предст ленной многочленом. Известно устройство для вычисления интегралов , содержащее регистр подынтегральной функции, сумматоры и регистр, в котором накапливается результат D-JОднако это устройство имеет боль шое время вычисления интеграла.. Наиболее близким цр технической сущности к предлагаемому является устройство для вычисления интеграло содержащее блок управления, накапливающий блок и п решающих блоков, каждый из которых содержит арифметический узел, сумматор остатка, ре гистр остатка, регистр порядка я блок элементов И-НЕ, причем группа .выходов блока управления соединена группой входов арифметического узла группа выходов которого подключена к первой группе входов сумматора ос татка, вторая группа входов которог соединена с группой выходов регистipa остатка, первая группа выходов которого подключена ко входу регист ра порядка и первому входу блока элементов И-НЕ, группа выходов которого подключена к .соответствуюа1ей группе входов накапливгшадего блока 123 Недостатком известного устройства является низкое быстродействие. Цель изобретения - увеличение быстродействия устройства для вычисления интегралов на интервале Го, X от функции, представленной многочленом. Поставленная цель достигается тем, что каждый из п решающих блоков дополнительно содержит к выходных сумматоров и коммутатор, а накапливающий блок содержит два дешифратора, и сумматор, причем п,ёрвая группа выходов сумматора остатка i-го решающего. блока (где i 1, 2, ...п) соединена с первой группой входов коммутатора того же блока, вторая, третья .,., (К+1} группы входов коммутатора под ключены к соответствующим группам выходов К выходных сумматоров, первые группы входов которых соединены с первой группой выходов сумматора остатка, а вторые группы входов выходных .сумматоров подключены к группе выходов регистра порядка, старшие разряды каждого из К рыходных сумматоров соединены с соответствующими входами блока элементов И-НЕ, группа выходов которого подключена к четвертой группе входов коммутатора, группа выходов которого подключена к первой группе входов регистра остатка, вто |рая группа входов которого соединена со второй группой выходов сумматора остатка, группы входов накапли вающего блока через первый дешифратор,, сумматор, и второй дешифратор связаны с группой выходов накапливающего блока. . На чертеже изображена структурная схема устройства для вычисления интегралов. Устройство содержит блок 1 управ ления, п решающих блоков 2 и накапл вающий блок 3. Блок управления может быть выпол нен как кольцевой сдвиговый регистр или как счетчик с дешифратором. Каждый решающий блок 2 содержит арифметический узел 4, ко входам ко торого подключены входные шины 5, 6, а также выходы 5/, 5 и б , б, блока 1 управления. Выходы узла 4 подведены ко входам младших разрядов сумматора 7 остатка, ко входам которого со сдвигом на один разряд влево (т.е. в сторону старших разрядов) подключены выходы регистра 8 оста.тка, выполненного на триггерах с внутренней задержкой. Выходы стар ших разрядов сумматора 7 соединены со входами выходных сумматоров 9 и 9/2. и коммутатора 10, соединенного со входами старших разрядов регист.ра 8, а выходы остальных младших разрядов сумглатора 7 связаны со вхо дами остальных разрядов регистра 8. Выходы регистра 11 порядка соединены со входами сумматоров 9, связанных со входами коммутатора 10, причем ко входу сумматора 9,. выходы регистра 11 подведены со сдвигом влево на один разряд. Кроме того, выход знакового разряда сумматора 7 подключен к управляющему входу реги стра 11 и к первому входу блока элементов И-НЕ 12, выполняющего систему переключательных функций. Ко второму и третьему входам блока 12 подведены выходы знаковых разряд сумматоров 9 и 9/, а с четвертым входом .соединена шина 13 признака инвертирования. Первый, второй и третий выходы блока 12 соединены со ответственно с выходными шинами 14 14,j , 14, блока 2,а три управляющих входа коммутатора 10 связаны соответственно со вторым, первым и четвертым выходом. Накапливающий блок 3 содержит сумматор 15, выходы которого через первый дешифратор 16 связаны с выходными шинами 14 всех I блоков 2 и входными шинами -17 , 17 JITS начального условия, а выходы трех старших разрядов сумматора 15 через второй дешифратор 18 соединены с выходными шинами 19 , 19,/ 19 накапливающего блока 3. Синхронизирующая шина 20 подключена к цепям сдвига в блоке 1 управления, к управляющему входу узла 4 и к цепям приема кода на регистр ,8 во всех блоках 2, и к цепям сдвига сумматора 15 в накапливающем блоке 3. В исходном состоянии (цепи установки исходного состояния на чертеже не показаны) в блоке 1 управления единица находится в крайнем левом положении. В каждом i-ом блоке 2 в регистре 11 записано число i . В регистре 8 и сумматоре 15 записаны нули. В- каждом J-OM цикле на входные шины 5 каждого блока 2 поступает очередная цифра yj числа а.,- X Y (т.е. численного значения в точке X i-го члена подынтегральной функции), а на входные шины б поступает очередная цифра числа X. В устройстве числа подаются на входные шины и формируются на выходных шинах последовательно, начиная со старших разрядов, в избыточном двоичном коде с цифрами -2, -1, О, +1, +2, причем единица на первой и второй шинах имеют вес соответственно 2 и 2 , а третья шина знаковая. При этом с . выходов узла 4 на вход сумматора 7 поступает число, равное у- Х- + xj Y-, где Х Y.j,, - числа X и Y f представленные соответственно только j и j-1 старшими цифрами. Это число складывается в сумматоре 7 с содержимым регистра 8 и знак полученной суммы управляет выдачей кода из регистра 11 таким образом, что если эта сумма отрицательна, то на сумматоры 9 выдается прямой код числа хран,имого на регистре 11, в противном случае выдается дополнительный код. Кроме того, на сумматоры 9 поступает содержимое старших разрядов сумматора 7. Блок 12, анализируя состояние знаковых разрядов сумматоров 7, 9 9 и шины 13 признака инвертирования вырабатывает .управляющий сигнал для коммутатора 10 и очередную цифру Z.J результата (т.е. числа Z Ь- , являющегося численным значением в точке X i+1-го члена .первообразной функции, представленной многочленом), которая., выдается на ВБ1Ходные шины 14 блока 2. Так, если значения знаковых разрядов сумматоров 7 и 9-2 совпадают, то формируется цифра результата Z, , равная по модулю двум, и коммутатор 10 ко входам старших разрядов регистра 8 подключает выходы сумматора 9. Если предьщущее условие не выполняется, но совпадают значения знаковых разрядов, сумматоров 7 и 9. , то формируется цифра 2 , равная по модулю

единице, и коммутатор 10 подключает ко входам старших разрядов регистра 8 выходы сумматора 9 , Если же не выполняются оба предыдущие условия, то формируется цифра Zy , равная нулю, и коммутатор 10 ко входам регистра 8 подключает старшие разряды регистра сумматора 7. При отсутствии сигнала на шине 13 знак цифры результата Z: формируется равным знаку числа на сумматоре 7, в противном случае знак Zj противоположен знаку кода сумматора 7, В накапливающем блока 3 в казкдом цикле вычисления происходит сложение цифр, поступающих по входным шинам начального условия 17 и цифр с выходов блоков 2. Результат накапливается в сумматоре 15 и в каждом цикле в трех его старших разрядах формируется очередная цифра численного значения интеграла. Схемы 16 служат для преобразования цифр из прямого кода в код удобный для работы сумматоров (например, дополнительный), а схема 18 на выходе блока 3 - для обратного преобразования, В конце цикла следует, сигнал в шине 20, по которому в блоке 1 единица сдвигается на разряд вправо, во всех блоках 2 в регистры 8 заносится код, сформированный на входе этих регистров, в сумматоре 15 значение знакового разряда записывается в соседний младший разряд, а в остальных разрядах происходит сдвиг на один разряд в сторону старших разрядов. Время вычисления интеграла на интервсше Го, Х от функции, представленной многочленом, в предлагаемом устройстве не зависит от X, причем задержка появления старшей цифры результата составляет пять циклов, т.е. для получения значения интеграла с точностью до п разрядов, необходимо выполнить п+5 циклов вычисления..

В известных устройствах, время вычисления только одного члена суммы превышает время вычисления интеграла в предлагаемом устройстве. Следовательно, предлагаемое устройство по меньшей мере в К раз превосходит по быстродействию известные, где К - количество членов суммы, зависящее от заданной точности вы числения и от величины интервала ин.тегрирования.

Формула изобретения

Устройство для вычисления интегралов, содержащее блок управления.

накапливающий блок и ri решающих, блоков, каждый из которых содержит арифметический узел, сумматор остат- ка, регистр остатка, регистр порядка и блок элементов И-НБ, причем группа выходов блока управления соединена с группой входов арифметического узла, группа выходов которого подключена к первойгруппе входов сумматора остатка,- вторая группа входов которого соединена с

0 группой выходов регистра остатка, первая группа выходов которого подключена ко входу регистра порядка и первому входу блока элементов И-НЕ, группа выходов которого подключена

s к соответствующей группе входов накапливающего блока, отличающ е е с я тем, что, с целью порышения быстродействия j ка1ждый изп решающих блоков дополнительно содержит к -выходных сумматоров и коммута0тор, а накапливающий блок содержит два дешифратора, и сумматор, причем первая группа выходов сумматора остатка 1-го решающего блока (где i 1, 2, ... п) соединена с первой

5 группой входов коммутатора того же блока, вторая, третья, ..., (к+1) группь входов коммутатора подключены к соответствующим группам выходов k выходных сумматоров, первые группы

0 входов которых соединены с первой группой выходов сумматора остатка, а вторые группы входов выходных сумматоров подключены к группе выходов регистра порядка, старшие разряды

5 каждого иэ К выходных сумматоров соединены с соответствующими входами блока: элементов Й-НЕ, группа выходов которого Подключена к четвертой группе входов коммутатора, группа выходов которого подключена к. первой

0 группе входов регистра остатка, вторая группа входов которого соединена со второй группой выходов сумматора остатка, группы входов накапливающего блока через первый, дешифратор,

5 сумматор и второй дешифратор связаны с группьа Ьыходов накапливающего блока..

Источники информации,

0 принятые во внимание при экспертизе

1.Авторское свидетельство СССР 46998, кл. G 06 J 1/02, 1974.

2.Авторское свидетельство СССР

5 388278, кл. G Об J 1/02, 1972 (прототип).

J

5,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Устройство для вычисления квадратного корня | 1976 |

|

SU642706A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| Дифференцирующее устройство | 1974 |

|

SU517894A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для вычисления обратной величины | 1976 |

|

SU732861A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

г 92

19,

Авторы

Даты

1981-06-23—Публикация

1976-03-16—Подача