1

Изобретение относится к области вычислительной техники, в частности к устройствам сопряжения -вычислительных машин с цифровыми иятеграторами н может быть использовано при построении гибридных вычислительных систем.

Известно устройство сопряжения, содержащее дешифратор адреса, входы которого соединены с выходами регистра кода операции и счетчика адреса, регистр признака, выход которого через дешифратор признака соединен с первым управляющим выходом устройства и управляющими входами регистра кода операции н счетчика адреса, счетчик данных, выход которого соединен с входом блока управления, соединенного двухсторонними связями с первым и вторым входамивыходами устройства, реверсивный преобразователь прямого кода в дополнительный, первый информационный вход которого соединен с первым информационным выходом буферного регистра, причем вычитающий вход счетчика данных, первый информационный вход буферного регистра и вход регистра признаков соединены с информационным входом с первым информационным выходом устройства, а выходы дешифратора адреса соединены с группой выходов устройства.

Цель изобретения - сокращение Обо1рудования устройства.

Поставленная цель достигается тем, что второй и третий информационные выходы устройства соединены соответственно с первым и вторым информационными выходами

буферного регистра, второй информационный вход которого соединен с первым информационным выходом реверсивного преобразователя прямого кода в дополнительный, управляющий вход которого соединен с выходом

дещифратора признаков, а вторые информационные вход и выход реверсивного преобразователя прямого кода в дополнительный соединены соответственно с вторым информационным входом п третьим информационным выходом устройства.

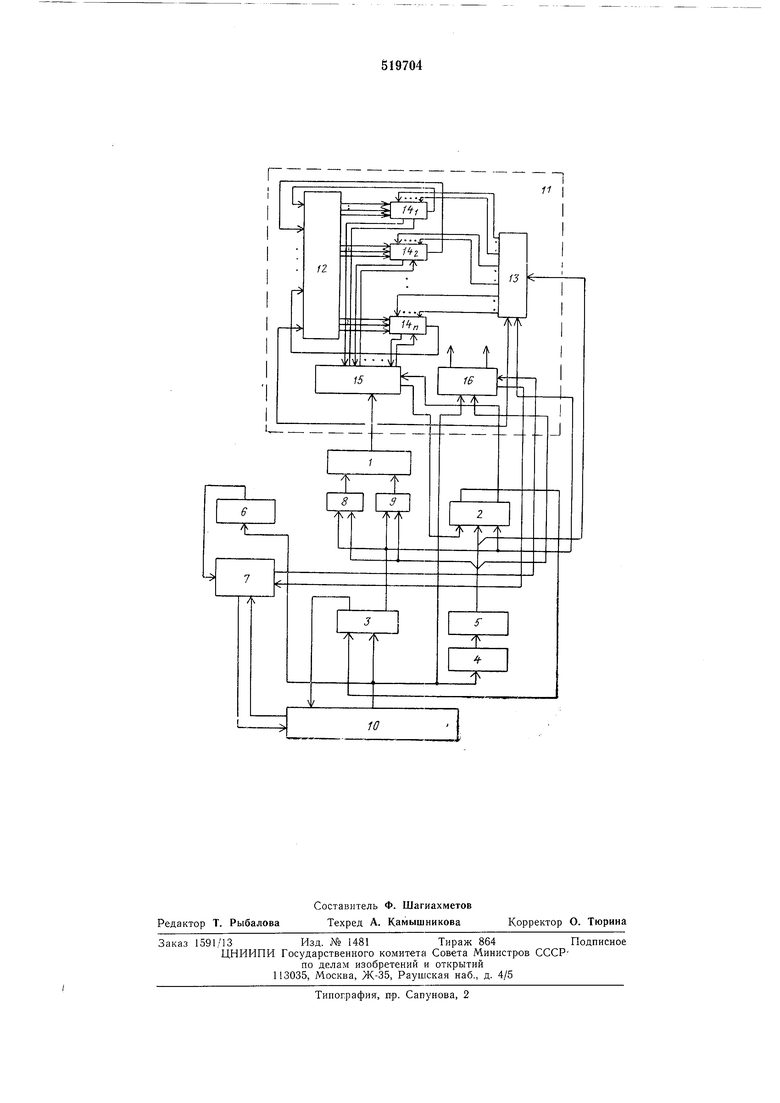

Блок-схема устройства сопряжения представлена на чертеже.

Устройство сопряжения содерл ит дешифратор адреса 1, реверсивный преобразователь

2 прямого кода в дополнительный, буферный регистр 3, регистр признака 4, дешифратор признака 5, счетчик данных 6, блок управления 7, регистр 8 кода операции, счетчик адреса 9.

В схему входят вычислительная машина 10 (ЦВМ), цифровой интегратор 11, коммутатор 12, командное запоминающее устройство 13, решающие блоки 14i-14п, числовое запоминающее устройство 15 и блок 16 управления. В запоминающем устройстве 15, предназначенном для хранения значений подынтегральной функции, возможно осуществление обращения параллельно по словам и последовательяо по разрядам (режим рещения), 5 обращение лараллельно по разрядам и последовательно по словам (режим обмена идформацией с ЦВМ через устройство связи). Запоминающее устройство 13 служит для ю приема и хранения команд настройки рещающих блоков. Каждый помер ячеек памяти запоминающих устройств 13 и 15 соответствует, таким образом, тому же номеру рещающего блока. Однотипные рещающие 15 блОКн 14i-14„ настраиваются командами настройки перед рещением задачи на выполнение определенных операций (суммирования приращений, интегрирование функций и т. д.) В зависимости от «ода операции адрес используется или для осуществления соединения выходов и входов решающих блоков в соответствии со структурной схемой набора задачи, или для задания ячейки памяти за- 25 поминающих устройств 13, 15. Устройство работает следующим образом. Цри выполнении команд обращения к интегратору 11 «Записать, «Читать и «Управление осуществляются следующие функ- ЗО ции управления работой инте-гратора 11 со стороны ЦВМ 10 через устройство сопряжения: передача начальных значений подынтегральной функции в устройство 15; ввод команд настройки в устройство 13; вывод ре- 35 зультатов решения из устройства 15; ввод адресных команд для осуществления электронной коммутации выходов и «ходов решающих блоков или для выбора ячейки памяти в устройствах 13 и 15 при вводе чисел, ко- 40 манд настройки или выводе результатов решения, ввод управляющей, информации в блок управления 16 и в устройство сопряжения. К управляющей информации относятся: ко- 45 личество передаваемых данных; сигналы «Цуск и «Сброс интегратора И; код, задающий время решения задачи интегратором 11; коды, определяющие время отработки начального участка интегрирования, код приз- 50 нака передаваемой информации. Командой «Записать осуществляется передача начальных значений подынтегральной функции, команд настройки, адресных команд для электронного соединения выходов 55 и входов решающих блоков 14i-14«, кодов, задающих время решения и отработки начального участка интегрирования интегратором И. Командой «Управление выполняется пере- 60 дача кода признака передаваемой информации, пуска или сброса, адресной команды для ввода числа, команд настройки в соответствующие запоминающие устройства. С помощью команды «Читать осуществля- 65 20 ется вывод результатов рещения из устройства 15. Ввод числовой информации в интегратор II происходит следующим образом. Сначала вьшолияется -команда «Упрайление, которая вводит адресную «оманду по информационным щинам ЦВМ 10 через буферный регистр 3 в дешифратор адреса 1 и код признака передачи числа в регистр признака 4, причем код операции адресной команды определяет передачу информации в параллельно-параллельное устройство 15. С помощью дещифратора 1 осуществляется выбор требуемой ячейки устройства 15. Сразу за командой «Управление выполняется -команда «Записать, осуществляющая передачу числа параллельным кодом по информационным шинам ЦВМ 10 через буферный регистр 3 и преобразователь 2 (преобразует прямой код в дополнительный) в соответствующую ячейку памяти, определенную дещифратором адреса 1. Кроме того, при выполнении команды «Записать («Читать) в счетчик 6 передается число, хранящееся в ее адресной части и определяющее количество -передаваемых данных. Цри передаче массива чисел в ячейки устройства 15 с последовательными адресами достаточно один раз задать командой «Управление начальный адрес ячейки устройспва 15 для ввода первого числа. При вводе остальных чисел содержимое счетчика адреса 9 автоматически увеличивается, а содержимое счетчика 6 уменьшается на единицу по сигналам блока управления 7. Как только в счетчике 6 окажется пулевой код, блок управления 7 выдает в ЦВМ 10 сигнал об окончании передачи массива чисел при выполнении команды «Записать («Читать). Так как с буферного регистра 3 информация может передаваться в дешифратор адреса I, в преобразователь 2, в блок управления 16 или в устройство 13, то для ее идентификации цри вводе в соответствующий блок служат регистр 4 и дешифратор 5 признака информации. Поэтому при передаче соответствующего вида информации командой «Записать, в предварительно выполняемой команде «Управления ставится признак этой информации. Вывод результатов решения происходит аналогично вводу начальных значений. Предварительно командой «Управлепие задается начальный адрес ячейки памяти, начиная с которой будут считываться данные в ЦВМ 10. Затем при выполнении команды «Читать, в которой задано количество считываемых данных и начальный адрес оперативного запоминающего устройства ЦВМ 10, считываемые числа параллельными кодами через преобразователь 2 (дополнительный код преобразуется в прямой) и буферный регистр 3 по информационным шинам записываются в память ЦВМ 10. Ввод управляющей информации, кода, задающего время решения или отработки начального участка интегрирования, из памяти ЦВМ 10 в интегратор 11 осуществляется командой «Записать по информационным шинам ЦВМ 10 в блок управления 16, причем командой «Управление предварительно определен призна1К передаваемой информации. Потенциал, снимаемый с дешифратора 5 и задаваемый в блок управления, разрешает прием соответствующего вида информации. Кроме того, на выходе дешифратора 5 образуются сигналы пуска или -сброса интегратора И при выполнении :соответствуюш,их модификации команды «Управление.

Ввод команд настройки в запоминающее устройство 13 организуется таким же образом, «ак и при передаче начальных значений в устройство 15. Команды настройки при выполнении команды «Записать по информационным шинам ЦВМ 10 через буферный регистр 3 попадают в устройство 13, куда. разрешен прием информации сигналом с дешифратора признака 5 при выполнении предварительной команды «Управление.

Передача адресных команд из ЦВМ 10 в дешифратор адреса 1 для осуществления электронной коммутации выходов и входов решающих блоков 14i-14п выполняется командами «Управление и «Записать. Предварительно выполняемая команда «Управление передает в регистр 4 признак информации, а команда «Записать осуществляет непосредственную передачу адресных команд из намяти ЦВМ 10 в устройство сопряжения. Код операции адресных команд определяет выход или вход соответствующих решающих блоков 14i-14«. С помощью деш 1фратора адреса 1 происходит настройка коммутатора 12 на требуемые соединения выходов и входов решаюших блоков 14i-14и.

Формула изобретения

Устройство сопряжения, содержащее дешифратор адреса, входы которого соединены

с выходами регистра кода операции и счетчика адреса, регистр признака, выход которого через дешифратор признака соединен с первым управляющим выходом устройства и управляющими входами регистра кода операции и счетчика адреса, счетчик данных, выход которого соединен с входом блока управления, соединенного двусторонними связями с первым и вторым входами-выходами устройства, реверсивный преобразователь

прямого кода в дополнительный, первый информационный вход которого соединен с первым информационным выходом буферного регистра, причем вычитающий вход счетчика данных, первый информационный вход буферного регистра и вход регистра признака соединены с информационным входом и первым информационным выходом устройства, а выходы дешифратора адреса соединены с группой выходов устройства, отличающееся

тем, что, с целью сокращения оборудования, второй и третий информационные выходы устройства соединены соответственно с первым и вторым информационными выходами буферного регистра, второй информационный

вход которого соединен с первым информационным выходом реверсивного преобразователя прямого кода в дополнительный, управляющий вход которого соединен с выходом дешифратора признаков, а вторые ииформационные вход и выход реверсивного преобразователя прямого кода в дополнительный соединены соответственно с вторым информационным входом и третьим информационным выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1978 |

|

SU741259A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1619284A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство сопряжения интегрирующей машины с цифровой вычислительной машиной | 1974 |

|

SU599273A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

Авторы

Даты

1976-06-30—Публикация

1974-09-26—Подача