Изобретение относится к вычислительной технике и может быть использовано, например, для сопряжения ЦВМ со стохастическими интеграторами при построении гибридных вычислительных систем.

Известны устройства для сопряжения, содержащие блок буферных регистров, соединенный входами с соответствующими входами устройства, распределитель опроса, блок управления, блок синхронизации и блок формирования адреса, и выполняющие функции управления организацией обмена между объектами и ЦВМ 1.

Недостаток этих устройств состоит в ограниченных функциональных возможностях и низком быстродействии, поскольку выбор объекта производится последовательно вне зависимости от его состояния.

Наиболее близким к технической сущности к изобретению является устройство сопряжения/ содержащее буферный регистр, счетчик адреса, дешифратор адреса, регистр кода операции, регистр признака, дешифратор признака, счетчик данных, реверсивный преобразователь и блок управления, и выполняющее функции сопряжения ЦВМ с цифровым интегратором. В устройстве вводу исходных данных в каждом функциональном направлении предшествует передача управляющего слова, по которому выполняется команда Управление, а затем передается информация (выполнение командам Записать) .Управляющее слово содержит код признака передаваемой

10 информации, код признака адресной команды для ввода числа, код признака команды настройки запомина|ощего устройства, а также.команды пуска или сброса. При выполнении команды

15

Записать

осуществляется передача на интегратор одного информационного слова или группы слов в функциональном направлении, заданном при

Управление

выполнении команды

20

Вывод результатов решения задачи также осуществляется путем передачи от ЦВМ управляющего слова, указывающего на функциональный адрес считываемой информации и непосредственной

25 передачи результатов решения с интегратора на ЦВМ при выполнении команды Читать 2.

Недостатки этого устройства заключаются в ограниченных функциональных

30 возможностях и низком быстродействии.

бусловленных тем, --гго оно ие позвояет ор-Ганизоьать э;-.-;.,,ечу ггнформаии от ЦВМ без .;й У :р;|вляющего лова для кш.кдого Оункч.ионального аправления, не может вьдцать инфорацию в ЦВМ без- получения от нее оманды выдачи, не позволяет сформиовать код состояния интеграторов, тражающий промежуточный или конечный этап решения згэ.дачи., а также не обеспечивает Фор ми р о s а к и я с о общения Г/инимального объем;;;. содерж.л1цего промежуточные или конечные результаты решения задачи для вьщачи в ЦВМ.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для сопряжения, содержащее буферный регистр и блок управления, соединенные первы1ли входами и выходами соответственно с информационныгл- вxoдa и и выходами устройства, регистр состояния, подключенный входами к соответствующим входам из группы входов состояния объектов устройства, второй выход блока управления соединен с выходом запуска устройства, введены память, два элемента задержки, узел приоритета и группа элементов И гашения, первые входы элементов И гашения группы соединены с соответствующими индикаторными 3xo, устройстзс1., вторые входы - с соответствуюги. выходами узла приоритета и выходами из группьт адресных выходов устройства, управляющий вход - с третьим выходомблока управЛенин и управляющим входом буферного регистра выход группы элеглентов И га1аения соединен со вторьвд входом .буферного регистра, второй и третий Быходы которого подключ-ены соответственно ко вхо.цу узла приоритета, соедкненкюму управляющим выходом со вторым входом блока управления, и второму информационному ;выходу устройства, выход регистра состоя 1ия соединен с информационным входом памяти, выход которой подключен к третьему входу буферного регистра, а управляющий вход через первый и второй элементы задержки - соответственно к управляющим входам регистра состояния и устройства и третьему входу блока управления.

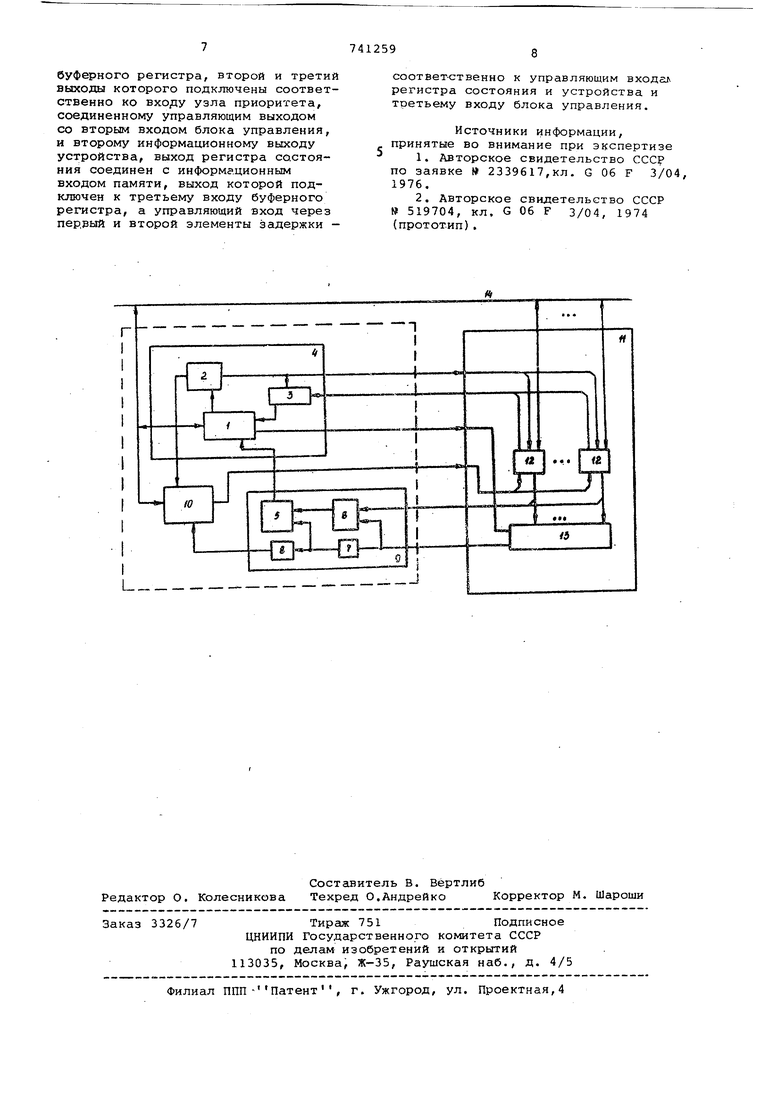

На чертеже представлена блок-схема устройства.

Схема устройства содержит буферный регистр 1, узел 2 приоритета, группу 3 элементов И гаииения, составляющие блок 4 организации циклического обмена, память 5, регистр 6 состояния, первый 7 и второй 8 элегу1енты задержки, составляющие блок 9 формирования инструкций, и блок 10 управления, специализированное вьгчислительное устройство 11, включающее стохастические интеграторы 12 и блок 13 управления, и информационную магистраль 14 связи с ЦВМ.

Блоком 4 организации циклического обмена при приеме информации от ЦВМ.осуществляется прием адресного слова, указывающего функциональное направление и порядок следования исходной информации в информационном пакете, передаваемом в сопрягаемое устройство, распределение информации в соответствии с адресны1 1и сигна.пами, содержащимися в адресном слове, а также прием и хранение кодов, режимов работы сопрягае.мого устройства .

При вьщаче на ЦВМ промежуточных или конечных результатов решаемой задачи блок 4 осуществляет прием от блока 9 кодов состояния интеграторов и адресных сигналов, которые определяют функциональный признак и порядок следования информации в инфомационном пакете,а также в соответствии с адресным словом производит подключение интеграторов к информационной магистрали для выдачи результато решения задачи на ЦВМ. Блок 10 управления предназначен для управления обменом информацией между ЦВМ, блоком 4 и сопрягаемым устройством при вводе и выводе информации.

Блок 9 форш рования инструкцией по позиционньтм сигна.пам состояния, поступающим от сопрягаемого устройства, формирует код состояния и адресное слово, которое указывает, на каком эт.;пе решег-ия задачи на ЦВМ будет выдана промежуточная или конечная информация, какой функциональный смысл в ней заключен и в каком порядке ее необходимо выдавать.

В регистр 1 при приеме информации от ЦВМ заносится адресное слово и код режима работы сопрягаемого устройства. В адресном слове каждому интегратору 12 выделен адресный разряд, наличие единицы в котором указывает на то, что при данном обме в соответствующий интегратор будет заноситься информация. Порядковый номер адресного разряда регистра 1 определяет очередность занесения информации в выб эанный интегратор 12. Узел 2 приоритета выбирает адресную ,.7 того интегратора- 12, единч у. в адресном разряде регистра I которого имеет высший приоритет. Одновременно адресные сигналы поступают на элементы 3 И группы через которые после занесения информации .vj выбранный интегратор производится гашение (сброс) того адресного разряда регистра 1, который был выбран узлом. 2. При этом на выходе узла 2 выбирается адрес следующего Функциональног направления.

При выдаче результата решения на ЦВМ в регистр 1 заносится адресное

слово и код состояния интеграторов 12. В этом случае адресное слово указывает, из каких интеграторов и в какой последовательности на ЦВМ будет выдаваться информация.

Устройство работает следующим образом.

При приеме информации от ЦВМ первая информационная посылка, содержащая адресное слово и код режима, заносится в регистр 1 и подается на узел 2 для выбора адреса того интегратора 12, адресная единица которого в адресном слове имеет высший приоритет, а на информационной магистрали 14 от ЦВМ выставляется информация, которую необходимо занести Б выбранный интегратор. После занесения информации данный интегратор 12 формирует известительный сигнал, который поступает на элементы 3 И группы. По сигналу от блока 10 производится гашение (сброс) адресного разряда, соответствующего данному интегратору. Узел 2 выбирает следующий разряд адресного слова, хранимого в регистре 1, в котором записана единица и подключает адресный сигнал к следующему интегратору

Аналогичным образом производится занесение информации в другие интеграторы, единицы в адресных разрядах которых были занесены в регистр 1 при обмене на данном цикле. .1 После занесения информации во все интеграторы, помеченные единицами в адресном слове, принятом от ЦВМ, узел 2 формирует управляющий сигнал, который поступает в блок 10 и извещает об окончании занесения информации. Блок 10 в свою очередь производит запуск интеграторов на выполнение основной операции. Код режима из регистра 1 поступает в блок. 13 для указания типа защачи и режима ее решения.

Выдача на ЦВМ промежуточных или конечных результатов решения задачи осуществляется по инициативе устройства 11. При этом интеграторы формируют позиционные сигналы состояния, которые заносятся в регистр 6. Содержимое регистра б является адресом ячейки 5 памяти, где хранится инструкция.- С задержкой на время занесения сигналов состояния в регистр б с выхода первого элемента 7 формируется сигнал запуска памяти. Через время, необходимое для считывания информации из памяти, второй элемент 8 задержки вырабатывает сигнал, поступающий в блок 10 и извещающий его об окончании формирования инструкции. Эта инструкция содержит код устройства 11, а также адресное слово, указывающее из каких интеграторов 12 и в какой последовательности будет производиться выдача

накопленной информации при данном обмене с ЦВМ.

При этом первым словом на ЦВМ передается содержимое регистра 1, а затем в соответствии с состоянием 2 разрядов в адресном слове организуется поочередная выдача информации из интеграторов 12. Причем очередность выдачи информации из интеграторов определяется расположением их

... адресных разрядов в адресном слове регистра 1.

После выдачи информации с очередного интегратора производится гашение его адресного разряда в алресном слове регистра 1, узел 2 выбирает

5 следующий интегратор и блоком 10 разрешается выдача информации на ЦВМ от вновь выбранного интегрптора.

Таким образом, устройство позволяет обеспечить подключение группы

0 интеграторов, решающих одну общую

задачу, и организовать обмен информацией таким образом, что вся информация, вводимая из ЦВМ или выводимая на ЦВМ, сопровождается только одниМ

5 служебным словом, а это сокращает время обмена информацией между ЦВМ с сопрягаемыми устройствами.

Устройство позволяет также организовать циклический обмен информаq цией в процессе решения задачи с выдачей на ЦВМ не только промежуточных или конечных результатов решений, но и кодов состояния, указывающих, каким образом это решение проходило, что

г в свою очередь расширяет функциональные возможности устройства.

Формула изобретения

Устройство для сопряжения, содержащее буферный регистр и блок управления, соединенные первым входами и выходами соответственно с информационными входами и выходами устройства, регистр состояния, подключенный Входами к соответствующим входам из группы входов состояния объектов устройства, второй выход блока управления соединен с выходом запуска устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство введены память, два элемента задержки, узел приоритета и группа элементов И

гашения, первые входы элементов И гашения группы соединены с соответствующими индикаторными входами устройства, вторые входы - с соотетств тощими выходами узла приорит.еа и выходами из группы адресных выходов устройства, управляющий вход - с третьим выходом блока управения и управляющим входом буферного егистра, выход группы элементов И

гашения соединен со вторым входом

буферного регистра, второй и третий выходы которого подключены соответственно ко Bxofly узла приоритета, соединенному управляющим выходом со вторым входом блока управления, и второму информационному выходу устройства, выход регистра состояния соединен с информационным входом памяти, выход которой подключен к третьему входу буферного регистра, а управляющий вход через первый и второй элементы задержки соответ-ственно к управляющим входал регистра состояния и устройства и третьему входу блока управления,

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР по заявке 2339617,кл. G 06 F 3/0

2,Авторское свидетельство СССР 519704, кл. G 06 F з/04, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для обмена информацией | 1982 |

|

SU1091151A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для обмена информацией | 1977 |

|

SU741257A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

Авторы

Даты

1980-06-15—Публикация

1978-01-04—Подача