третьего элемсптои И, ,ыходы которых подключены cooTBeTCTJsciiHo к одним входам элементов ИЛИ 1 к входам блока переадресании, выходы которого еоедннены с другими входами элементов ИЛР, входы блока сравнения подключены соответствеино к выходам нервого входного регистра и донолнительного накопителя н сумматора, а в 1ходы блока сравнения соединены со входами второго входного регистра и сумматора, вход иерво1-о доиолнительного адресного блока иодключен к выходу регистра адреса, а его выход - к одному входу второго дополнительного адресного блока, другой вход которого соеди 1ен с выходом донолнительио1о иаконнтеля, а выходы второго донолнительиого адресного блока нодключены соответственно к входам дополнительного накопителя и счетчика.

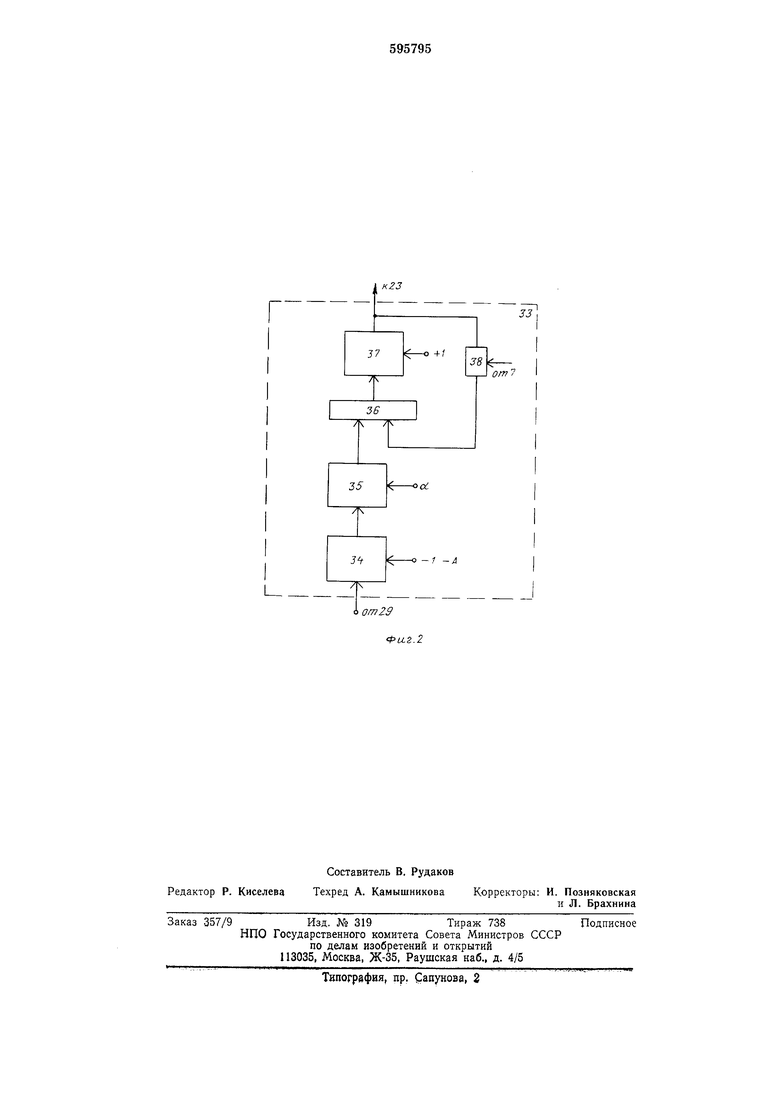

На фиг. 1 изображена схема устройства; на фиг. 2 - схема одного из вариантов блока переадресации.

Устройство (фиг. i) содержит накопитель 1, каждая ячейка которого имеет онределенное число резерв 1ых разрядов, информапионный выход накопителя 1 соедипен через разрядный блок 2 с блоком обнаружения и коррекции ошибок 3. Блок 3 содер кит регистры числа 4, 5, входы которых нодключены через разрядный блок 2 к выходам накоиителя 1, схему анализа 6, соединенную с регнстром числа 4 п блоком управления 7. Регистр числа 4 связан с блоком обпаруження ошибки 8, выходы которого подключены гс выходному peiiiCTpy 9 непосредствепно и через блок корре цин ошибок 10. Выходы регистров 4, 5 связаны со входом схемы обнаруження отказавших разрядов 11, выходы которой соединены со входами схемы развертки числа 12 и схемы свертки числа 13, кроме того, ко входам этих схем по.з,ключены выходы регистров 8, 4 соответственно, а выходы этих же схем связаны с регистром числа 4 н блоком обнаружения онн15ки 8 соответствеиио. Регистры 5, 4 через группу элемеито ИЛИ 1 1 и разрядный блок 2 С1)едипены со входом накопителя 1. Иаконитоль 1 подг;лючен через адресный блок 15 и де1ппфратс.р адреса 16 к регистру a;i,pcca 17,

Устройство также содержит первый 18 и второй И) доиолннтеллиле адресные блоки, счетчик 20, дополнительный наконитель 21, блок сравнения 22, сумматор 23, первый 24 н второй 25 входные ре1истры, дополнительный дешпфратор адреса 26, дополннтсльные элементы ИЛИ 27, первый 28, второй 29 н третий 30 элелюнты И, элемент за.тержки 31, элементы ИЛИ 32 н блок переадресании 33. Входы донолннтельного дегнифратора ад К:са 26 подключены к выходам nepBOio входного регистра 24, а 15ЫХОДЫ через дополпительные э.тсметы ИЛИ 27 соедииепы с управляюндимт входами элементов И 28-30, выходы первого входного регистра 24 подключеиы через последовательно соединенные элементы задержки 31, ервый элемент И 28, второй входной регистр 25 к информационным входам второго

29 н TpcTbeio 30 элементов 14, выходы которых подключ.ены соответственно к од1:И},1 входам элементо ИЛИ 32 и входам блока 33 нереадрееации, выходы которого соединены с другимн входамг элементов 1К1И 32, входы блока сравнения 22 подключены соответственпо к выходам первого входного регистра 24, дополпительиого накопителя 21 и сумматора 23, а выходы блока сравнення -22 соединены со

входами второго входного регистра 25 и сумматора 23, вход первого донолнительного адресного блока 18 нодключен iv выходу регистра адреса 17, а eio выхо,, -- к одному входу )5торого доиОо1нительиого адресного блока 19,

другой вход которого соеднне с выходом допол11птел1)Пог() на1 оннте,ля 21, а выходы второго донолиите.чьпого адресного б.чока ГУ подключеп соответственно ко входам дополнительного накопителя 21 и счетчика 20.

Блок переадресацпп 33 (см. фиг. 2) содержит сумматор 34, блок умпожения 35, соединенные поеледовательпо и подключенные ко входу элемента ИЛИ 36, выход которого нодключен к сумматору 37. Выход сумматора 37

связан со входом элеменга ИЛИ 36 через элемент задержкн 38, который соединен с блоком }Т1равле1; 1я 7. Выход сумматора 37 является выходом блока переадресацпи 33. Описанное устройство работает следуюш,им

образом.

Ирп считывании числа с иакоиителя 1, оно поступает на регнсгры 4, 5 и дальше на блок обнаружения оишбок 8. Ес.ти опшбок пет, число сразу передается на выходной регистр 9;

в случае 1аличия ошибки, число поступает на выходной регистр 9 через 5ло коррекции ошибок 10, :де ошибка устраняетея.

.1,ля того, чтобы при последующих обращениях к от --:азавгпей ячейке, сч1ггываемое число не содержало опншок, необходимо обеспечнт.з заннс1 этого числа в имеющиеся исправные резервные разряды.

Для обпаруження отказавших разрядов из регистра 5 в oтi:aзaвнJyю ячейку накопителя 1

записывается обратный код считанного числа и счить :;ается па ;от же; регнетр 5, па регис11)е 4 ()Д. ,ч:я з это время прямой код счиTRinioro Miic.ia. (хема обпаружони; отказавших ;)азр):дов 11 и:, совпадеппю содержилюго

однопмеи1:ых разрядов определяет позиции отказавнл1х разрядов и запоминает их. Схема развертки числа 12 запрещает заптсь ипформан1М в разряды регистра 4, соответствующие (зтказавн :м )а: рядам, затем число записывар а: ряды.

J-3 момент об ару кення onjn6KH адрес отказавгией ячейки ностунает на первый дополнительный адрееный блок 18, на выходе последпего формп:Э;|ется адрес ячсйкн дополнптельпой памяти, в состав коЧ)рой входят резервпые разряды отказави:ей , еслн псследняя относнтся к ocHOBHoii нал1}гти.

Если отказавпшя ячейка опгосптся х дополпительной иамятн, то на выходе первого дополнитслы1()1-о адресного блока 18 формируется непосредственно адрес отказавшей ячейкн. Второй донолнртельный адресный блок 19 заноснт постунившпй адрес в дополнительный паконнтель 21 таким образом, чтобы поступившие адреса располагались в порядке возрастания. При этом, на счетчик 20, на котором первоначально было записано общее число ячеек основной и дополнительной памяти, поступает сигнал вычитания «1. На счетчике, таким образом, фиксируется текущее зиачение общего объема памяти иакопителя 1. При последующем обращении к заиоминающему устройству с самоконтролем, адрес вызываемой ячейки поступает на первый входной регистр 24. Дополнительный дешифратор адреса 26 определяет к какому виду памяти основной или дополнительной) относится вызываемая ячейка. В первом случае на выходе элемента ИЛИ 27 формируется логический «О, разрешающий прохождение сигнала через элементы И 28, 30 и закрывающий элемент И 29. Адрес вызваниой ячейки через элемент задержки 31 и элемент И 28 иоступает иа второй входной регистр 25 и дальше через элементы И 30 и ИЛИ 32 на регистр адреса 17.

Если вызываемая ячейка относится к дополнительной иамяти, то па выходе элемента ИЛИ 27 формируется логическая «1, которая запрещает передачу сигналов через элементы И 28, 30 и иоступает на вход сумматора 23. Адрес вызываемой ячейкн поступает на блок сравнения 22. Туда же поступает первый (т. е. наимеиьший) из адресов, хранящихся в дополпительпом пакопителе 21. Если вызываемый адрес меньще поступившего из дополнительного накопителя 21, то первый поступает на второй входной регистр 25. В противном случае к адресу вызываемой ячейки на сумматоре 23 прибавляется «1 и вновь образовавщийся адрес поступает на блок сравнения 22 вместе со вторым по очередности адресом, хранящемся в дополнительном накопителе 21.

В дальнейшем работа аналогичная описанной будет иметь место до тех пор, пока вызываемый адрес не окажется меньше очередного адреса из дополнительного накопителя 21, или все адреса, которые имелись в дополнительном накопителе будут исчерпаны.

Таким образом, иа второй входной регистр 25 поступит адрес, отличающийся от поданного на первый входной регистр 24 на столько единиц, сколько дополнительных ячеек с адресами, меньшими вызываемого, вышли из строя (адреса последиих хранятся в дополнительном накопителе 21).

Через элемент И 29 преобразованный адрес поступает на блок переадресапии 33. Последний осуществляет преобразование поступающего на его вход адреса в последовательность адресов тех основных ячеек, резервные разряды которых образуют дополнительную ячейку с адресом, поданным на вход блока переадресации 33.

В качестве возможного варианта исиолиення блока иереадресаиин 33 рассматривается блок переадресации, выполняющий исреадресацию согласно вырал еи)по

Л,(Л„- 1-Л) + /С

где Лм - входной адрес блока переадресации; АК - выходной адрес блока переадресации;

а - количество ячеек в группе основных

ячеек, резервные разряды которых образуют одну дополннте- .ьную ячейку;

А - количество основных ячеек; К - номер основной ячейки в группе

().

Это реализуется последовательной подачей исходного адреса на сумматор 34 и блок умноження 35. затем с помощью сумматора 37 производится я-кратное прибавление «1. На выходе блока переадресации формируется последовательность адресов Ак.

Таким образов;, описанное запоминающее устройство с самоконтролем обеспечивает использование тех резервных разря т.ов в качестве дополнительной памяти, которые не используются для замены вышедших из строя разрядов основной иамяти. Запоминающее устройство с самоконтролем при незначительных аппаратурных затратах позволяет существенно увеличить эффективиый объем памяти накоиителя, особеино ири большом объеме основной памяти. Наприлтер, если осиовная память иакопителя состоит из 8192 ячеек и в каждой ячейке имеется 37 разрядов (из них 5 резервиых), то объем дополнительной памяти составит 1256 ячеек.

Формула изобретения

Заиомииающее устройство с самоконтролем, содержащее накопитель, адресные входы которого через последовательно соединенные адресный блок, дешифратор адреса и регистр

адреса подключеиы к выходам элементов ИЛИ, а разрядные входы и выходы накопителя через разрядный блок соедииеиы с соответствующими выходами и входами блока обнаружения и коррекции ошибок, дополнительный накопитель, блок сравнения, входные регистры, элементы И и дополпительные элементы ИЛИ, отличающееся тем, что, с целью повышенпя надежности и эффективной емкости устройства, оио содержит дополнительные

адрееные блоки, счетчик, сумматор, блок переадресации, элемент задержки и дополнительный дещифратор адреса, входы которого подключены к выходам первого входного регистра, а выходы через дополнительные элементы

ИЛИ соединены с управляющими входами элементов И, выходы первого входного регистра подключеиы через иоследовательно соединенные элемент задержки, первый элемент И и второй входной регистр к информационным входам второго и третьего элементов И,

/

выходы которых подключены соответственно к ОД1ПП1 входам элсме тов ИЛИ и к.входам блока персадресации, выходы которого соединены с дру1 -1М1( р.ходамн элементов ИЛИ, входы блока сравнения подключены соответственно к выходам первого входного регистра, дополнительного накопителя и сумматора, а выходы блока сравнения соединены со входами второго входного регистра и сумматора, вход первого донолнительного адрееного блока подключен к выходу регистра адреса, а его выход - к одному входу второго доиолнительного адресного блока, другой вход которого соединен с выходом дополнительного накопителя, а выходы второго дополнительного адресиого блока подключены соответственно к входам донолнительного накопителя и счетчика.

И сточники информации, принятые во внимание при экспертизе

1.Иатент США 3742459, кл. 34-172.5, 1973.

2.Авторское свидетельство СССР „Yg 504249, кл. G НС 29/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Постоянное запоминающее устройство с самоконтролем | 1985 |

|

SU1285538A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Запоминающее устройство с автономным контролем | 1973 |

|

SU476605A1 |

| Устройство переадресации накопителяиНфОРМАции СиСТЕМы ОбРАбОТКи дАННыХ | 1979 |

|

SU845157A1 |

| Ассоциативное запоминающее устройство | 1972 |

|

SU477463A1 |

| Запоминающее устройство | 1973 |

|

SU475663A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970478A1 |

| Постоянное запоминающее устройство с самоконтролем | 1983 |

|

SU1153360A1 |

Г

33

от

Авторы

Даты

1978-02-28—Публикация

1976-01-12—Подача