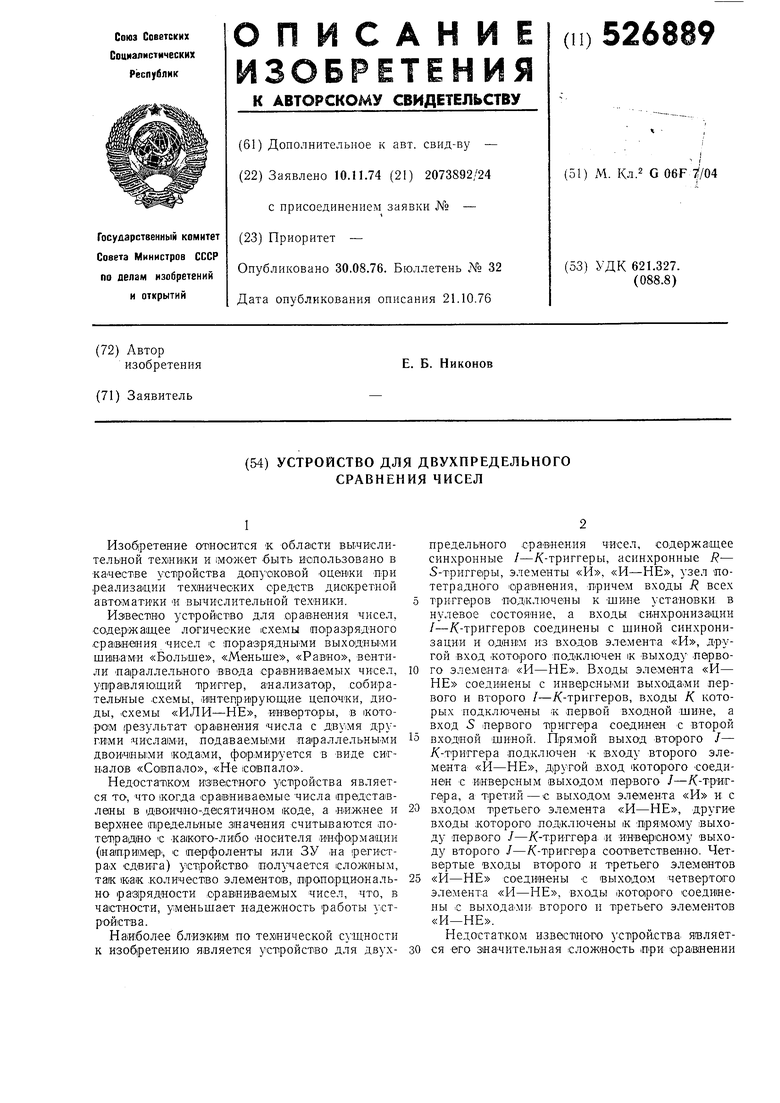

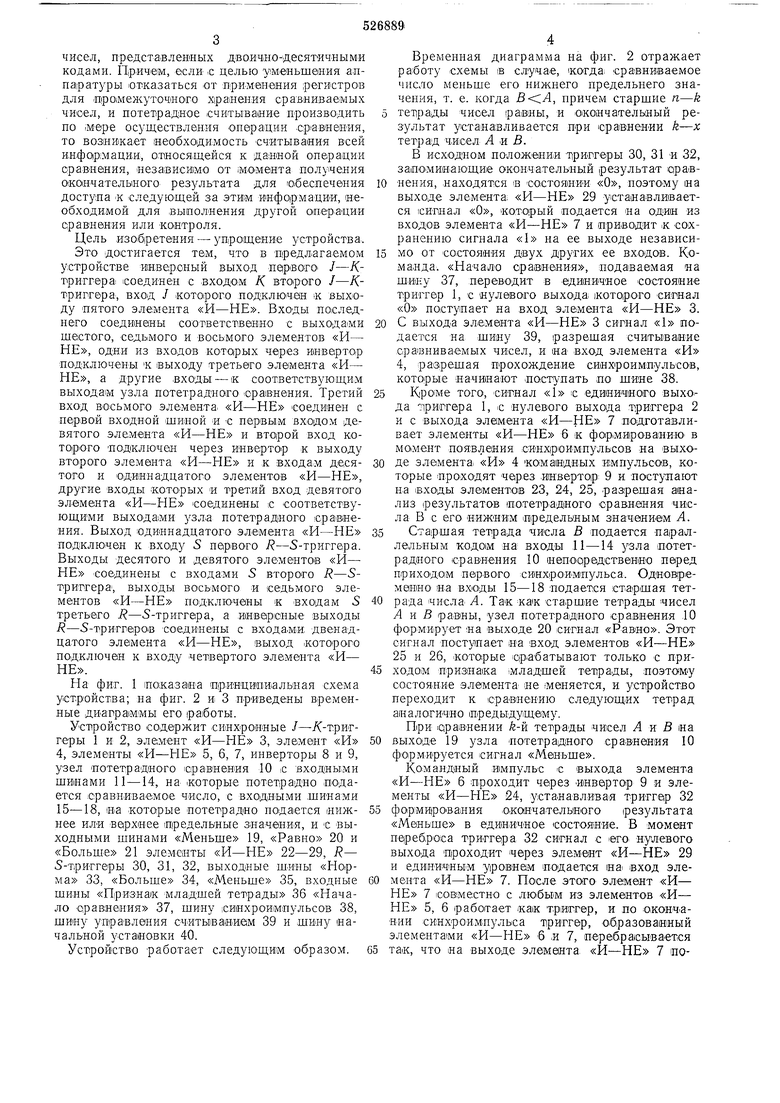

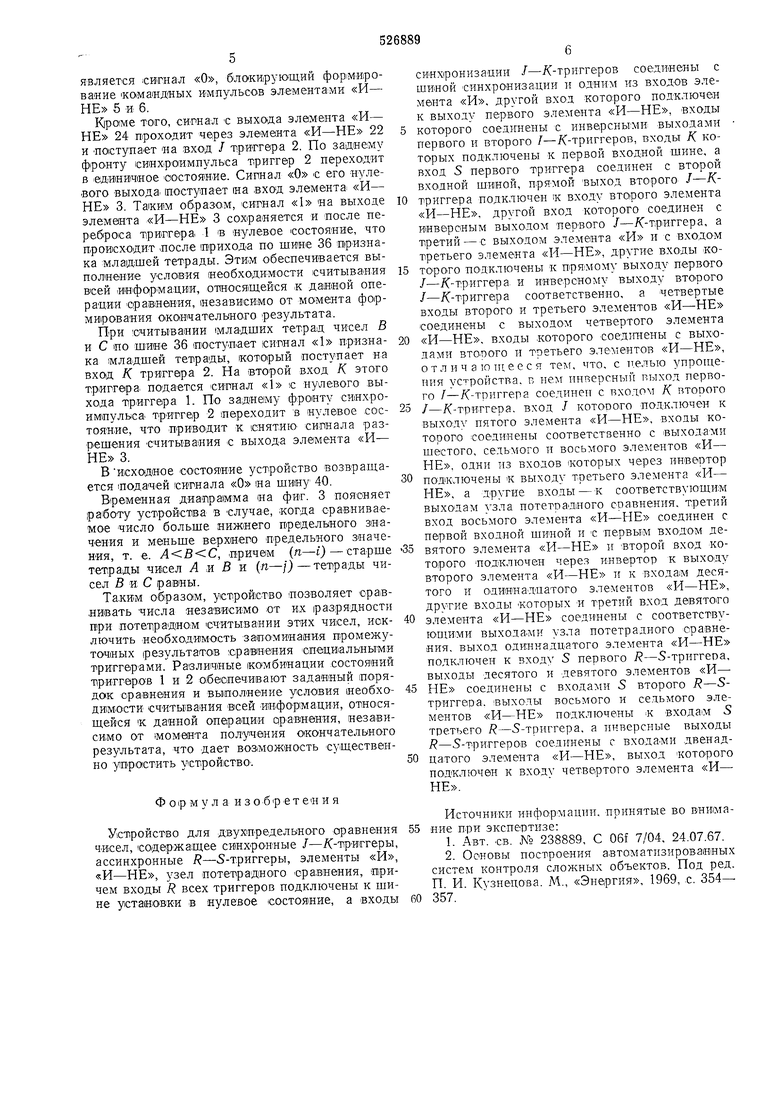

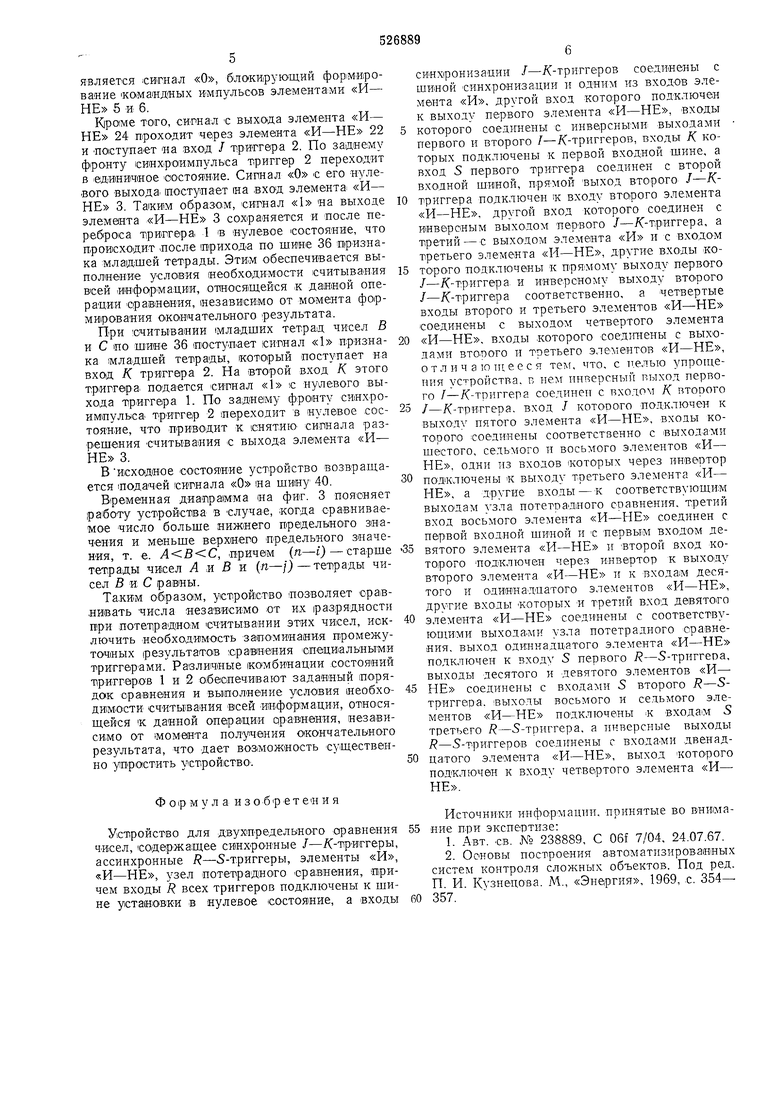

чисел, представленных двоично-десятичными кодами. Причам, если с целью уменьшения апнаратуры |0тказаться от при.манения регистров для Н р01межут04ного Х|ра1неН:ИЯ сравниваемых чисел, и нотет.радное считывание производить по iMepe осуществления онерации €р|авне1ИИя, то возникает необходимость считывания всей и.нфор(Мации, от1носящейся к данной операции сравнения, неза;виси1мо от iMOiMOHTa получения ожанчателыного результата для юбеспечения доступа К следующей за этим информации, необходимой для выоолнения другой ооерации сравнения или контроля. Цель изобретения - упрощение устройства. Это достигается тем, что в предлагаемом устройстве инверсный выход neipeorO /-КТ1риггера соединен с входо-м К второго /-К.триггера, вход / KOTOpoiro нодключан к выходу нятого элемента «И-НЕ. Входы последнего соединены соответственно с выходами шестого, седьмого и восьмого элементов «И- НЕ, одни из входов которых через инвертО|р подключены к выходу третьего э. «И- НЕ, а другие входы - к соответствующим выходам узла потетрадного сравнения. Третий вход восьмого элемента. «И-НЕ соединен с первой входной 1шиной И с первым входом девятого элемента «И-НЕ и второй вход которого Подключен через инвертор к выходу второго элемента «И-НЕ и к входам десятого и одиннадцатого элементов «И-НЕ, другие входы которых и третий вход девятого элемента «И-НЕ соединены с соответствующими выходами узл:а потетрадного сравнения. Выход одиннадцатого элемента «И-НЕ подключен к входу 5 первого R-5-триггера. Выходы десятого и девятого элементов «И- НЕ соединены с входами S второго R-5триггера, выходы восьмого и седьмого элементов «И-НЕ подключены к входам S третьего jR-S-триггера, а инварсные выходы R-5-триггеров соединены с входа.ми двенадцатого элемента «И-НЕ, выход которого подключен к входу четвертого элемента «И- НЕ. На фиг. 1 показана щринцициальная схема устройства; на фиг. 2 и 3 приведены временные дИагра1ММЫ его работы. Устройство содержит синхронные /-/С-триггеры 1 и 2, элемент «И-НЕ 3, элемент «И 4, элементы «И-НЕ 5, 6, 7, инверторы 8 и 9, узел яотетрадного 1Сравнения 10 с входными шииами И -14, на которые потетрадно подается сравниваемое число, с входными шинами 15-18, на которые потет-радно нодается нижнее или верхнее предельные знаЧ.ени.я, и С выходными шинами «Меньше 19, «Равно 20 и «Больше 21 элементы «И-НЕ 22-29, R- 5-триггеры 30, 31, 32, выходные шины «Норма 33, «Больше 34, «Меньше 35, входные шины «Признак младшей тетрады 36 «Начало оравнения 37, шину синхроимпульсОВ 38, шину управления сЧИтыван.ием 39 и .шину начальной установки 40. Устройство работает следующим образом. Временная диаграмма на фиг. 2 отражает работу схемы в случае, когда сравниваемое число меньше его нижнего предельнего значения, т. е. когда , причем старшие п-k тетрады чисел равны, и окончательный результат устанавливается при сравнении k-х тетрад чисел Л и Б. В исходном положении триггеры 30, 31 и 32, запОМинающие окончательный результат сравнения, находятся в состоянии «О, поэтому на выходе элемента «И-НЕ 29 устанавливается сигнал «О, который подается на один из входов элемента «И-НЕ 7 и приводит к сохранению сигнала «1 на ее выходе независимо от СОСТОЯНИЯ двух других ее входов. Команда. «Начало сра(Внения, подаваемая на шину 37, переводит в единичное состояние триггер 1, с нулевого выхода iKOTOporo сигнал «О поступает на вход элемента «И-НЕ 3. С выхода элемента «И-НЕ 3 сигнал «1 подается на шину 39, разрешая считывание орачзниваемых чисел, и на вход элемента «И 4, разрешая прохождение синхроимпульсов, которые начина:ют .поступать .по шине 38. Кроме того, сигнал «1 с единичного выхо;да приггера 1, ic нулевого выхода цриггер а 2 и с выхода элемента «И-НЕ 7 подготавливает элементы «И-НЕ 6 к формированию в момент появления синхроимпульсов на выходе элемента «И 4 командных импульсов, которые проходят через .инвертор: 9 и пост т1ают на входы элементов 23, 24, 25, разрешая анализ результатов 1ПОТетр.адного сравнения числа Е с его нижним Предельным значением А. СтарШая тетрада числа В ПОдается параллельным кодом на входы 11-14 узла потетрадного сравнения 10 непосредственно перед приходом первого синхр.оимпульса. ОднОВ1реманно на входы 15-18 подается старшая тетрада числа А. Так как старшие тетрады чисел А и В ра.вны, узел потетрадного сравнения ,10 формирует на выходе 20 сигнал «Равно. Этот сигнал поступает на вход элементов «И-НЕ 25 и 26, которые |др.абатывают только с приходом признака младшей тетрады, поэтому состояние элемента .не меняется, и устройство переходит к сраВНению следующих тетрад ан а л огично пр ед ыдущ.ему. Нри 1С|равнении й-й тетрады чисел Л и В на выходе 19 узла потетраднОГО сра.внения 10 формируется Сигнал «Меньше. Командный .импульс с выхода элемента «И-НЕ 6 проходит через инвертор 9 и элементы «И-НЕ 24, устанавЛИваЯ триггер 32 формирования .окончательного результата «Меньше в едвНИчное состояние. В момент nqpe6.poca триггера 32 сигнал с его. нулевого выхода Проходит через элем.ент «И-НЕ 29 и едиНИчнЫМ урОВнам подается на вход элемента «Н-НЕ 7. После этого элемент «И- НЕ 7 icOBiMecTHO с любым из элементов «И- Е 5, 6 |рабо1та.ет KaiK триггер, и по О.кончаии синхроим;нульса триггер, .Образованный лементами «И-НЕ 6 л 7, перебрасывается ак, что на выходе элбманта, «И-НЕ 7 появляется 1сигнал «О, блокирующий форадированне |камащдщых импульсов элементами «И- НЕ 5 и 6. KlpoiMC того, сигнал -с выхода элемента «И- НЕ 24 проходит через элемента «И-НЕ 225 и Поступает «а вход / т-риггера 2. По заднему фрОНту (синхроимпульса триггер 2 переходит в единичное состоящие. Сигнал «О с его нулевого выхода- поступает 1на вход элемента: «И- НЕ 3. Та1ки м образом, сигнал «1 на выходе элемента «И-НЕ 3 сохраняется и после переброса триггера 1 в нулевое состояние, что происходит лослб прихода по шине 36 иризнака младшей тетрады. Этим обеспечивается выполнепие усло1вия необходимости считывания 15 всей информации, относящейся к данной oneращии сравнения, независимо от момента формирования 0|КО|Н(чатель1Ного результата. При считывании младших тетрад чисел В и С но шине 36 поступ.ает 1сиппал «1 признака младшей тетрады, который поступает на вход К триггера 2. На второй вход К этого тр(Иггера. подается (сигнал «1 с нулевого выхода триггера 1. По заднему фронту синхроимпульса тригге/р 2 переходит в нулевое сое- 25 тояние, что приводит к снятию сипнала разрешения считывания с выхода элемента «И НЕ 3. Висходное состояние устройство возвращается шодачей сигнала «О на шину 40.30 В|ременная диаграмма на фиг. 3 поясняет 1ра(боту устройства в случае, когда сравниваемое ЧИСЛО больше нижнего предельного значения и меньше верхнего предельного значения, т. е. , причем (п-i) - старше -35 тетрады чисел Л и В и (ft-/)-тетрады чисел В И: С ра(В(НЫ. Та.ким образом, устройство позволяет сравнивать числа независимо от их (разрядности три потетрадном считывании этих чисел, иок- 40 лючить необходимость запоминания гвромежуточных результатов сраинения специальными триггерами. Различные комбинации состояний триггеров 1 и 2 обеспечивают заданный порядок сравнения и выполнение условия яеобхо- 45 димости считывания В1сей информации, относящеися К да(ннои операции цр-авнения, независимо от момента получения окончательного результата, что дает возможность существенно уп(р(астить устройство . Формула изобретения Устройство для двухпредельного сравнения55 чисел, содержащее синхронные /-/(-триггеры, ассинхронные R-5-триггеры, элементы «И, «И-НЕ, узел потетрадного -сравнения, причем входы R всех триггеров подключены к шине устаиовки в нулевое (состояние, а входы60 50 синхронизации /-/ С-триггеров соединены с шиной синхроииза.ции и одним из входов элемента «И, другой вход которого иодключен к выходу первого элемента «И-НЕ, входы которого соединены с инверсны ми выходами первого и второго /-7(-триггеров, входы К которых подключены к первой входной шине, а вход S первого триггера соединен с второй входной шиной, прямой выход второго /-Ктриггера подключен к входу второго элемента «И-НЕ, другой вход которого соединен с инверсным выходом первого /-/(-триггера, а третий -с выходом элемента «И и с входом третьего элемента «Н-НЕ, другие входы которого подключены к Прялюму выходу первото /-К-триггера и инверсному выходу второго /-К-триггер а соответственно, а четвертые входы второго и третьего элементов «И-НЕ соединены с выходом четвертого элемента «И-НЕ, входы .которого соединены с выходами BTO.Doro и третьего элементов «И-НЕ, отличающееся тем, что, с целью ynponieния устройства, в нем инверсный выход первого /-/(-триггера соединен с входом К второго /-/(-триггера, вход / кото-оого подключен к выходу пятого элемента «И-НЕ, входы которого соединены соответственно с выходами шестого, седьмого и восьмого элементов «И- НЕ, одни из входов 1которых через инвертор подключены -к выходу третьего элемента «Н- НЕ, а другие входы-к соответствующим выходам узла потетрадного сравнения, третий вход восьмого элемента «И-НЕ соединен с первой входной шиной и с первым входом девятого элемента «И-НЕ и второй вход которого подключен через инвертор к выходу второго элемента «И-НЕ и к входам десятого и одиннадиатого элементов «И-НЕ, другие входы которых и третий вход девятого элемента «И-НЕ соединены с соответствуюншми выходами узла потетрадного оравнения. выход одиннадцатого элемента «И-НЕ подключен к входу S первого R-5-триггеоа, выходы десятого и девятого элементов «И- НЕ соединены с входами S второго R-Sтриггера. выходы восьмого и седьмого элементов «И-НЕ подключены -к входам S третьего R-5-триггера, а инверсные выходы R-5-триггеров соединены с входами двенадцатого элемента «И-НЕ, выход которого подключен к входу четве ртого элемента «И- Источники информацпи. принятые во внимание при экспертизе: 1. Авт. св. № 238889, С 06f 7/04, 24.07.67. 2. Основы построения автоматизированных систем контроля сложных объектов. Нод ред. Н. И. Кузнецова. М., «Энергия, 1969, с. 354- 357.

тетрада ППП П П -П--П

,SПП

П П

П

JIL

хиа

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1978 |

|

SU809164A1 |

| Устройство для управления вводом информации | 1983 |

|

SU1161949A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Генератор случайных последовательностей | 1983 |

|

SU1180887A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Устройство для преобразования интервалов времени в цифровой код | 1985 |

|

SU1411701A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

Авторы

Даты

1976-08-30—Публикация

1974-11-10—Подача