Изобретение относится к вычислительном технике и может быть использовано для обработки измерений параметров механических, гидравлических и электромеханических устройств в процессе их испытания.

Цель изобретения - упрощение преобразователя .

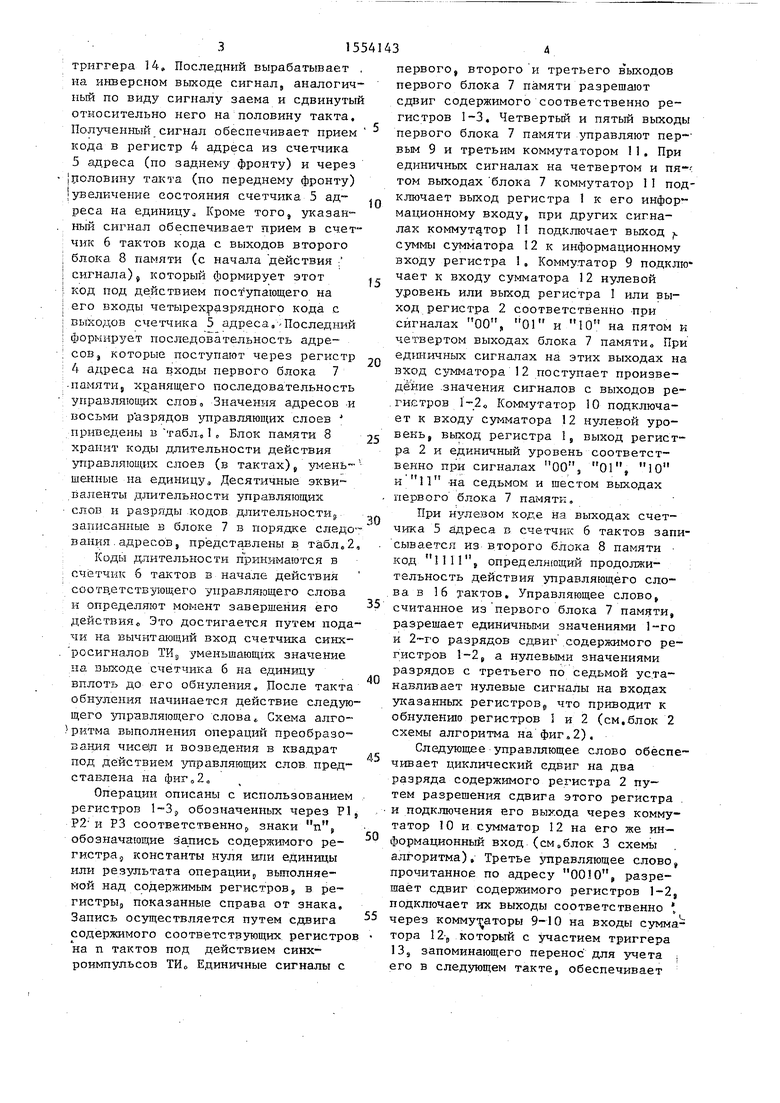

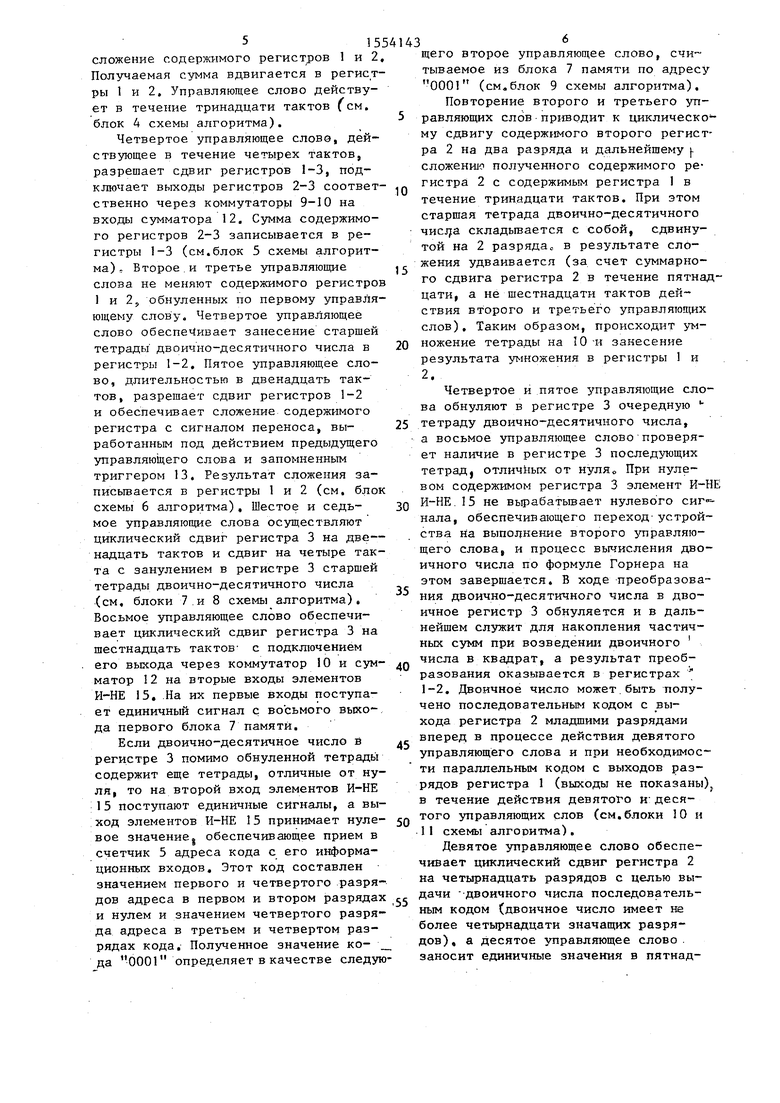

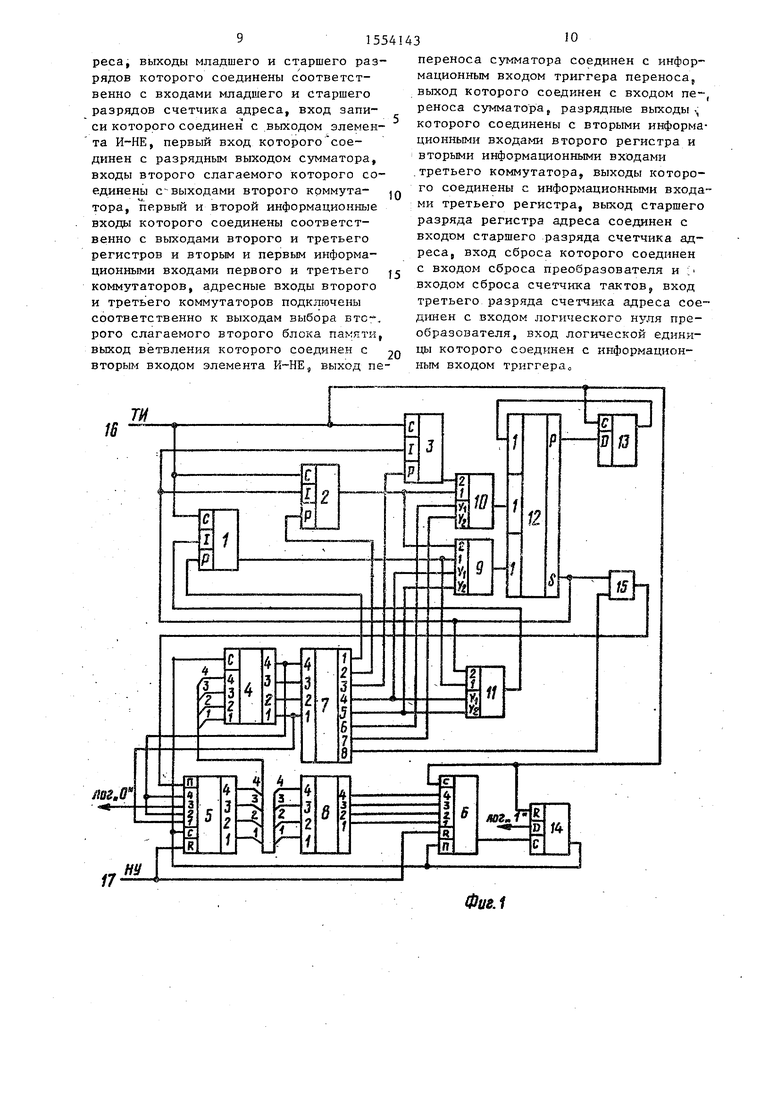

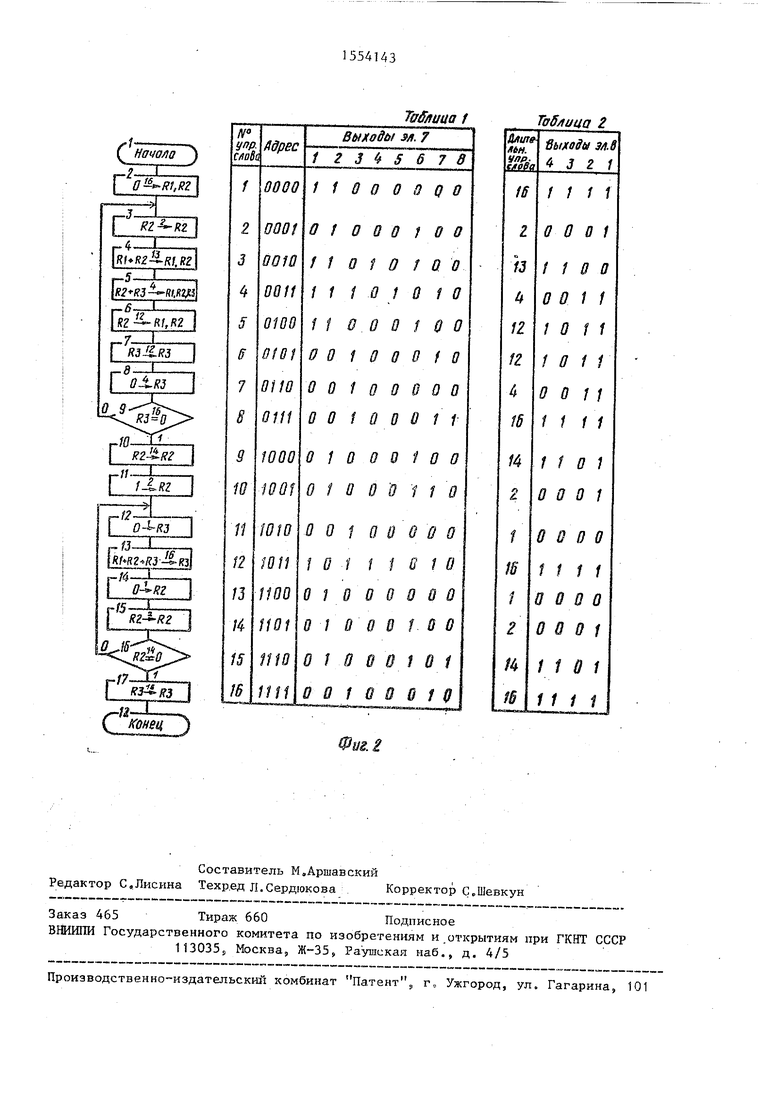

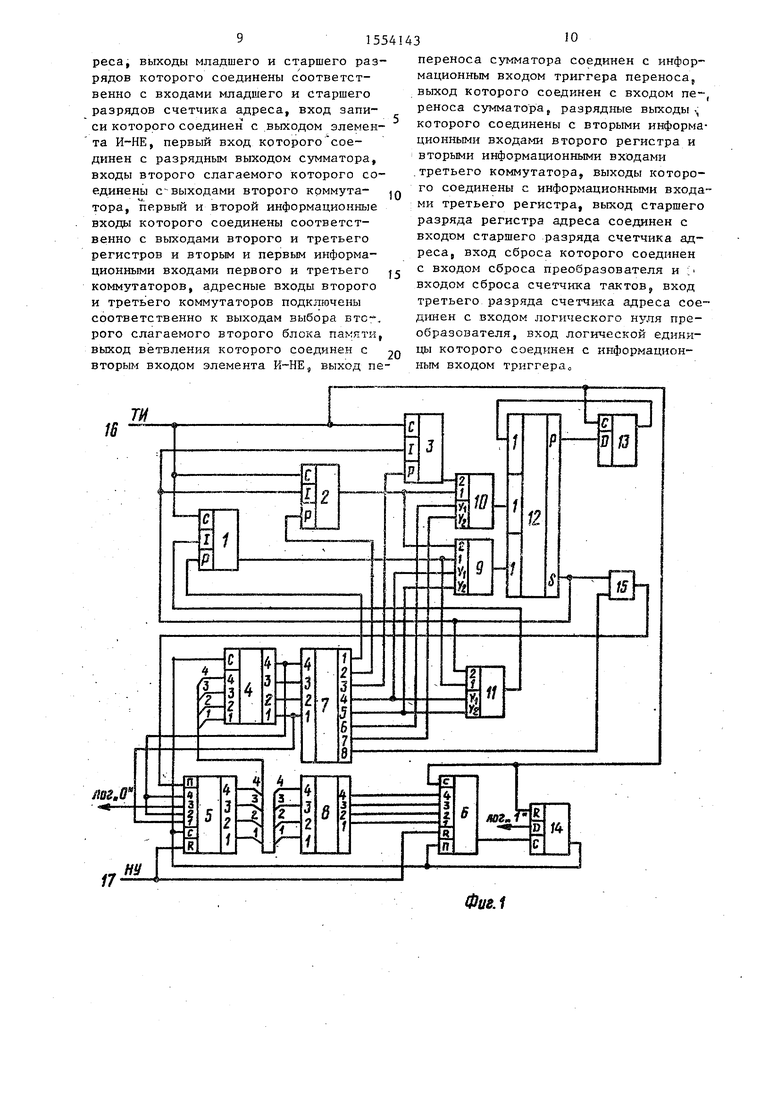

На фиг„1 приведена структурная схема преобразователя; на фиг.2 - б блок-схема алгоритма работы преобразователя .

Преобразователь содержит регистры 1-3, регистр 4 адреса, счетчик 5 адреса, счетчик 6 тактов, первый 7, второй 8 блоки памяти, коммутаторы 9-11, сумматор 12, триггер 13 переполнения и триггер 14, элементы И-НЕ 15, тактовый вход 16 преобразователя, вход 17 начальной установки. Блоки 4-8, 14 с соответствующими связями образуют .блок управления.

Преобразователь работает следующим образом.

На вход 16 поступают синхроимпульсы ТИ, типа меандр, тактирующие его работу,, На вход 17 приходит сигнал начальной установки (НУ), сбрасывающий счетчики 5 и 6 в нулевое состояние. Регистр 3 к моменту поступления сигнала НУ содержит исходное двоично-десятичное число, составленное, например, из четырех тетрад. Обнуление счетчика 6 приводит к выработке на его выходе сигнала заема, поступающего на синхровход

ЬгеИ.

СГ

СП

У Ы

3155

триггера 14, Последний вырабатывает па инверсном выходе сигнал, аналогичный по виду сигналу заема и сдвинутый относительно него на половину такта. Полученный сигнал обеспечивает прием кода в регистр 4 адреса из счетчика 5 адрьса (по заднему фронту) и через половину т акта (по переднему фронту) Iувеличение состояния счетчика 5 адреса на единицуа Кроме того, указанный сигнал обеспечивает прием в счетчик 6 тактоп кода с выходов второго блока 8 памяти (с начала действия сигнала), который формирует этот код под действием поступающего на его входы четырехразрядного кода с выходов счетчика 5 адреса. Последний формирует последовательность адресов, которые поступают через регистр 4 адреса на входы первого блока 7

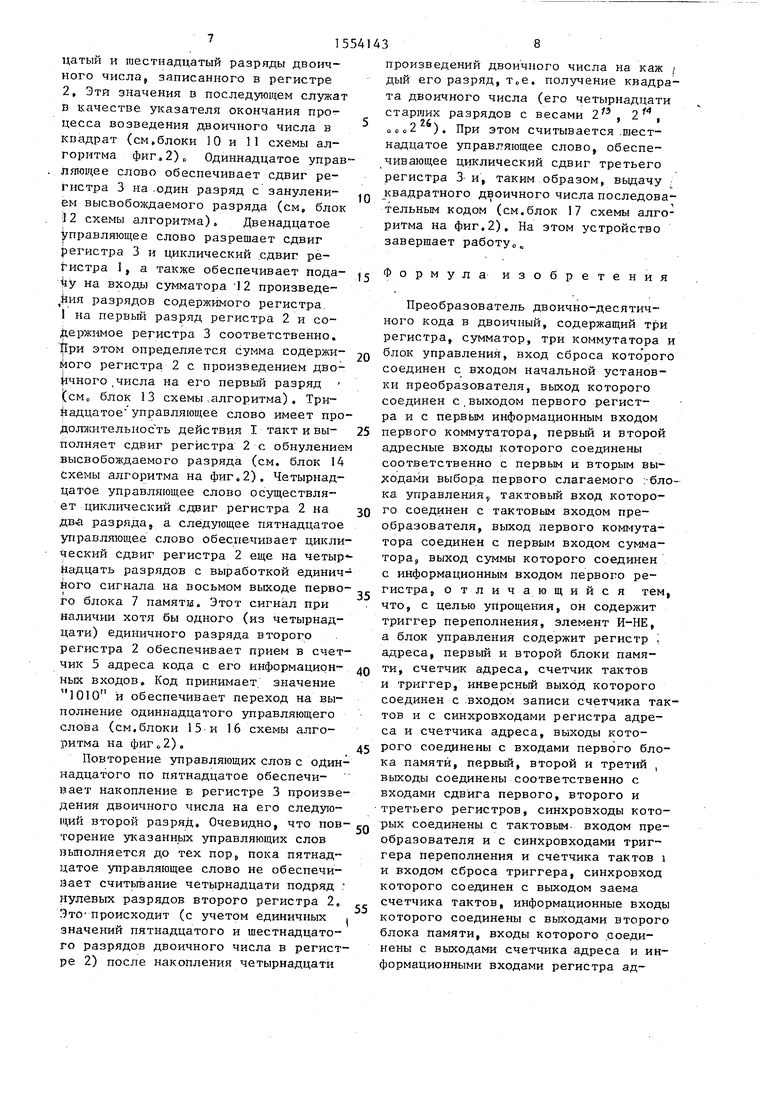

памяти, хранящего последовательность управляющих слов, Значения адресов и восьми разрядов управляющих слоев приведены в габл,1. Блок памяти 8 храпит коды длительности действия управляющих споев (в тактах), уменьшенные на единицу, Десятичные эквиваленты алитолыгасти управляющих слои и разряды кодов длительности, записанные в блоке 7 в порядке следования адресов, представлены в табл.2

Коды длительности принимаются в счетчик б тактов в начале действия соотв.о гств кшлего /праяляющего слова и определяют мокент завершения его действия. Эго достигается путем подачи на амций вход счетчика синхросигналов ТИ{ уменьшающих значение на тыходе счет мша 6 на единицу вплоть до его обнуления. После такта обнуления начинается действие следующего управляющего слова. Схема алго- 1 ритма выполнения операций преобразования чисел и возведения в квадрат под деиствнеи управляющих слов представлена на фиг„2,

Операции описаны с использованием регистров 1-3, обозначенных через Р1 Р2 и РЗ соответственноs знаки п, обозначающие запись содержимого регистра, константы нуля или единицы или результата операции, выполняемой над содержимым регистров, в регистры, показанные справа от знака. Запись осуществляется путем сдвига содержимого соответствующих регистро на п тактов под действием синхроимпульсов ТИ„ Единичные сигналы с

5

0

первого, второго и третьего выходов первого блока 7 памяти разрешают сдвиг содержимого соответственно регистров 1-3. Четвертый и пятый выходы первого блока 7 памяти управляют первым 9 и третьим коммутатором 11. При единичных сигналах на четвертом и пятом выходах блока 7 коммутатор 11 подключает выход регистра 1 к его информационному входу, при других сигналах коммутатор 1 подкплочает выход суммы сумматора 12 к информационному входу регистра 1. Коммутатор 9 подключает к входу сумматора 12 нулевой уровень или выход регистра I или выход регистра 2 соответственно при сигналах 00, О и 10 на пятом и четвертом выходах блока 7 памяти. При едшигчных сигналах на этих выходах на вход сумматора 12 поступает произведение значения сигналов с выходов регистров 1-2, Коммутатор 10 подключает к входу сумматора 12 нулевой уро5

0

5

0

5

5

ра 2 и единичный уровень соответственно при сигналах 00, 01, 10 и 11 на седьмом и шестом выходах первого блока 7 памяти.

При нулевом хоге HJ выходах счетчика 5 адреса в счетчик 6 тактов запи- сывае с:. из второго бллка 8 памяти код 1111, определяющий продолжительность действия управляющего слова в 16 тактов. Управляющее слово, считанное из первого блока 7 памяти, разрешает единичными значениями 1-го и разрядов сдвиг содержимого регистров 1-2, а нулевыми значениями разрядов с третьего по седьмой устанавливает нулевые сигналы на входах указанных регистров, что приводит к обнулению регистров 1 и 2 (см.блок 2 схемы алгоритма на фиг.2),

Следующее управляющее слово обеспечивает циклический сдвиг на два разряда содержимого регистра 2 путем разрешения сдвига этого регистра и подключения его выхода через коммутатор 10 и сумматор 12 на его же ин- 0 формационный вход (см.блок 3 схемы алгоритма). Третье управляющее слово, прочитанное по адресу 0010, разрешает сдвиг содержимого регистров 1-2, подключает их выходы соответственно через коммутаторы 9-10 на входы сумматора 12, который с участием триггера 13, запоминающего перенос для учета его в следующем такте, обеспечивает

сложение содержимого регистров 1 и 2. Получаемая сумма вдвигается в регистры 1 и 2, Управляющее слово действует в течение тринадцати тактов см. блок 4 схемы алгоритма).

Четвертое управляющее слово, действующее в течение четырех тактов, разрешает сдвиг регистров 1-3, подключает выходы регистров 2-3 соответственно через коммутаторы 9-10 на входы сумматора 12. Сумма содержимого регистров 2-3 записывается в регистры 1-3 (см.блок 5 схемы алгоритма) . Второе и третье управляющие слова не меняют содержимого регистров 1 и 2, обнуленных по первому управляющему слову. Четвертое управляющее слово обеспечивает занесение старшей тетрады двоично-десятичного числа в регистры -2. Пятое управляющее слово, длительностью в двенадцать тактов, разрешает сдвиг регистров 1-2 и обеспечивает сложение содержимого регистра с сигналом переноса, выработанным под действием предыдущего управляющего слова и запомненным триггером 13. Результат сложения записывается в регистры 1 и 2 (см. блок схемы 6 алгоритма), Шестое и седьмое управляющие слова осуществляют циклический сдвиг регистра 3 на две- надцать тактов и сдвиг на четыре такта с занулением в регистре 3 старшей тетрады двоично-десятичного числа (см, блоки 7 и 8 схемы алгоритма). Восьмое управляющее слово обеспечивает циклический сдвиг регистра 3 на шестнадцать тактов с подключением его выхода через коммутатор 10 и сумматор 12 на вторые входы элементов И-НЕ 15. На их первые входы поступает единичный сигнал с восьмого выхода первого блока 7 памяти.

Если двоично-десятичное число в регистре 3 помимо обнуленной тетрады содержит еще тетрады, отличные от нуля, то на второй вход элементов И-НЕ 15 поступают единичные сигналы, а выход элементов И-НЕ 15 принимает нулевое значение, обеспечивающее прием в счетчик 5 адреса кода с его информационных входов. Этот код составлен значением первого и четвертого разрядов адреса в первом и втором разрядах и нулем и значением четвертого разряда адреса в третьем и четвертом разрядах кода. Полученное значение ко- да 0001 определяет в качестве следую0

5

0

5

0

5

0

5

0

5

щего второе управляющее слово, считываемое из блока 7 памяти по адресу 0001 (см.блок 9 схемы алгоритма).

Повторение второго и третьего управляющих слов приводит к циклическому сдвигу содержимого второго регистра 2 на два разряда и дальнейшему сложению полученного содержимого регистра 2 с содержимым регистра 1 в течение тринадцати тактов. При этом старшая тетрада двоично-десятичного числа складывается с собой, сдвинутой на 2 разряда., в результате сложения удваивается (за счет суммарного сдвига регистра 2 в течение пятнадцати, а не шестнадцати тактов действия второго и третьего управляющих слов). Таким образом, происходит умножение тетрады на 10 и занесение результата умножения в регистры 1 и 2.

Четвертое и пятое управляющие слова обнуляют в регистре 3 очередную тетраду двоично-десятичного числа, а восьмое управляющее слово проверяет наличие в регистре 3 последующих тетрад, отличных от нуля„ При нулевом содержимом регистра 3 элемент И-НЬ И-НЕ 15 не вырабатывает нулевого нала, обеспечивающего перс-ход устройства на выполнение второго управляющего слова, и процесс вычисления двоичного числа по формуле Горнера на этом завершается. В ходе преобразования двоично-десятичного числа в двоичное регистр 3 обнуляется и в дальнейшем служит для накопления частичных сумм при возведении двоичного числа в квадрат, а результат преобразования оказывается в регистрах 1-2. Двоичное число может быть получено последовательным кодом с выхода регистра 2 младшими разрядами вперед в процессе действия девятого управляющего слова и при необходимости параллельным кодом с выходов разрядов регистра 1 (выходы не показаны), в течение действия девятого и десятого управляющих слов (см.блоки 10 и II схемы алгоритма).

Девятое управляющее слово обеспечивает циклический сдвиг регистра 2 на четырнадцать разрядов с целью выдачи двоичного числа последовательным кодом (двоичное число имеет не более четырнадцати значащих разрядов), а десятое управляющее слово заносит единичные значения в пятнад

цатый и шестнадцатый разряды двоичного числа, записанного в регистре 2, DTFI значения в последующем служат в качестве указателя окончания процесса возведения двоичного числа в квадрат (см,блоки 10 и 11 схемы алгоритма фиг.2)„ Одиннадцатое управляющее слово обеспечивает сдвиг регистра 3 на один разряд с занулени- ем высвобождаемого разряда (см. блок 12 схемы алгоритма). Двенадцатое управляющее слово разрешает сдвиг регистра 3 и циклический сдвиг регистра 1, а также обеспечивает пода- чу на входы сумматора 12 произведе- шя разрядов содержимого регистра 1 на первый разряд регистра 2. и содержимое регистра 3 соответственно. При этом определяется сумма содержи- мого регистра 2 с произведением двоичного числа на его первый разряд (сме блок 13 схемы алгоритма). Тринадцатое управляющее слово имеет продолжительность действия I такт и вы- полняет сдвиг регистра 2 с обнулением высвобождаемого разряда (см. блок 14 схемы алгоритма на фиг.2). Четырнадцатое управляющее слово осуществляет циклический сдвиг регистра 2 на двй разряда, а следующее пятнадцатое управляющее слово обеспечивает циклический сдвиг регистра 2 еще на четырнадцать разрядов с выработкой единичного сигнала на восьмом выходе первого блока 7 памяти. Этот сигнал при наличии хотя бы одного (из четырнадцати) единичного разряда второго регистра 2 обеспечивает прием в счетчик 5 адреса кода с его информацией- ных входов. Код принимает значение 1010 и обеспечивает переход на выполнение одиннадцатого управляющего слова (см.блоки 15 и 16 схемы алгоритма на фиг о 2).

Повторение управляющих слов с одиннадцатого по пятнадцатое обеспечивает накопление в регистре 3 произведения двоичного числа на его следующий второй разряд. Очевидно, что пов- горение указанных управляющих слов выполняется до тех пор, пока пятнадцатое управляющее слово не обеспечивает считывание четырнадцати подряд нулевых разрядов второго регистра 2. Это1 происходит (с учетом единичных значений пятнадцатого и шестнадцатого разрядов двоичного числа в регистре 2) после накопления четырнадцати

0

с Q 5 0 45

CQ

0

5

55

произведений двоичного числа на каж / дый его разряд, т„е. получение квадрата двоичного числа (его четырнадцати старших разрядов с весами 2 э , 2 14 ,

л /

„о«2 ). При этом считывается шестнадцатое управляющее слово, обеспечивающее циклический сдвиг третьего регистра 3 и, таким образом, выдачу квадратного двоичного числа последовательным кодом (см.блок 17 схемы алгоритма на фиг.2). На этом устройство завершает работу,„

Формула изобретения

Преобразователь двоично-десятичного кода в двоичный, содержащий три регистра, сумматор, три коммутатора и блок управления, вход сброса которого соединен с входом начальной установки преобразователя, выход которого соединен с выходом первого регистра и с первым информационным входом первого коммутатора, первый и второй адресные входы которого соединены соответственно с первым и вторым выходами выбора первого слагаемого блока управления, тактовый вход которого соединен с тактовым входом преобразователя, выход первого коммутатора соединен с первым входом сумматора, выход суммы которого соединен с информационным входом первого регистра, отличающийся тем, что, с целью упрощения, он содержит триггер переполнения, элемент И-НЕ, а блок управления содержит регистр , адреса, первый и второй блоки памяти, счетчик адреса, счетчик тактов и триггер, инверсный выход которого соединен с входом записи счетчика тактов и с синхровходами регистра адреса и счетчика адреса, выходы которого соединены с входами первого блока памяти, первый, второй и третий , выходы соединены соответственно с входами сдвига первого, второго и третьего регистров, синхровходы которых соединены с тактовым входом преобразователя и с синхровходами триггера переполнения и счетчика тактов i и входом сброса триггера, синхровход которого соединен с выходом эаема счетчика тактов, информационные входы которого соединены с выходами второго блока памяти, входы которого соединены с выходами счетчика адреса и информационными входами регистра ад1

реса, выходы младшего и старшего разрядов которого соединены соответственно с входами младшего и старшего разрядов счетчика адреса, вход записи которого соединен с выходом элемента И-НЕ, первый вход которого соединен с разрядным выходом сумматора, входы второго слагаемого которого соединены с выходами второго коммутатора, первый и второй информационные входы которого соединены соответственно с выходами второго и третьего регистров и вторым и первым информационными входами первого и третьего коммутаторов, адресные входы второго и третьего коммутаторов подключены соответственно к выходам выбора , рого слагаемого второго блока navm:;, выход ветвления которого соединен с вторым входом элемента И-НЕ, выход пе1

0

п

5

переноса сумматора соединен с информационным входом триггера переноса, выход которого соединен с входом пе-, реноса сумматора, разрядные выходы., которого соединены с вторыми информационными входами второго регистра и вторыми информационными входами третьего коммутатора, выходы которого соединены с информационными входа-ми третьего регистра, выход старшего разряда регистра адреса соединен с входом старшего разряда счетчика адреса, вход сброса которого соединен с входом сброса преобразователя и входом сброса счетчика тактов, вход третьего разряда счетчика адреса соединен с входом логического нуля преобразователя, вход логической единицы которого соединен с информационным входом триггерл0

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1649672A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1662004A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

Изобретение относится к вычислительной технике и может быть использовано для обработки измерений параметров механических, гидравлических и электромеханических устройств в процессе их испытания. Целью изобретения является упрощение преобразователя. Преобразователь содержит регистры, регистр адреса, счетчик адреса, счетчик тактов, блоки памяти, коммутаторы, сумматор, триггер переполнения и триггер, элементы И-НЕ, входы и выходы. Устройство выполняет преобразования чисел и возведение в квадрат под действием управляющих слов. 2 ил.

Фие.1

/ N

( Начала j

f i

j , I

Г4 ,

,Ег|

.w)

r-V I Uz-, J

Глл/1/ л |

Г R2&RZ

-H--4

Г чs -l.RZ

12

Г о-Ь-кз I

.13r J--i/T

«III

{ I

I

cw

Taff/н/иа 1

Таблица 2

Фиг. 2

| Устройство для преобразования двоичнодесятичных чисел в двоичные | 1975 |

|

SU550633A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-03-30—Публикация

1988-06-06—Подача