(Л

4

Изобретение относится к импульсной технике.

Целью изобретения является расширение функциональных возможностей и повышение надежности за счет уменьшения влияния нестабильности частоты следования импульсов.

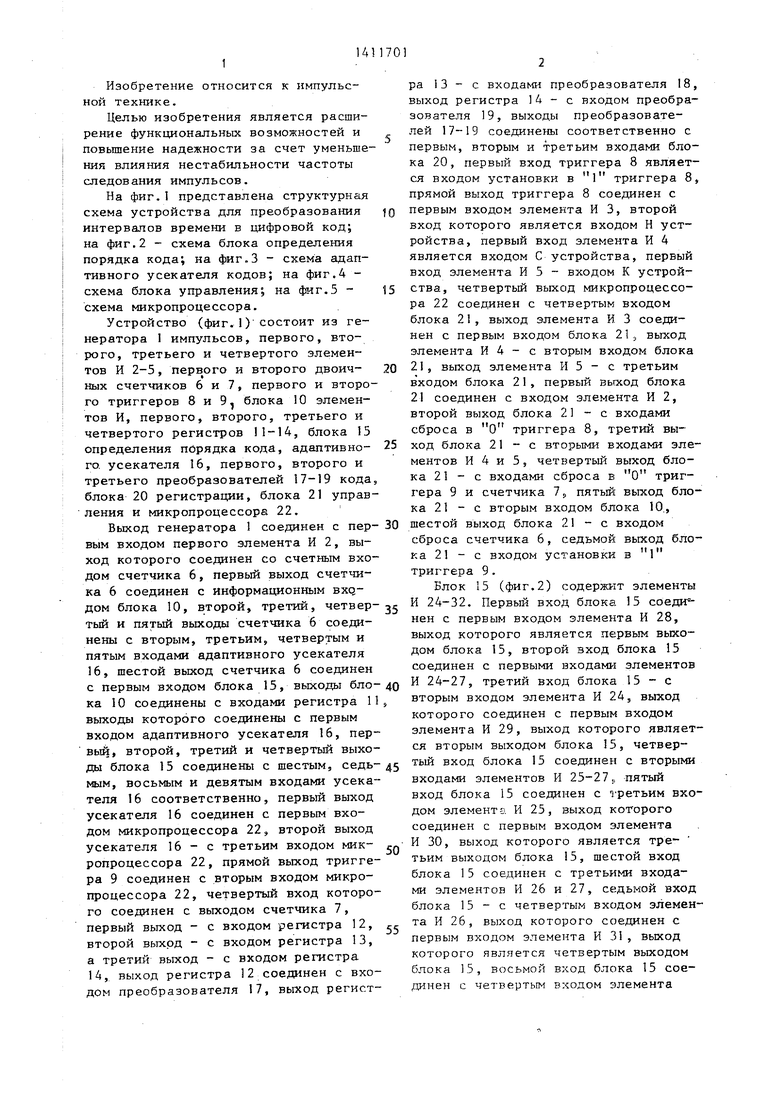

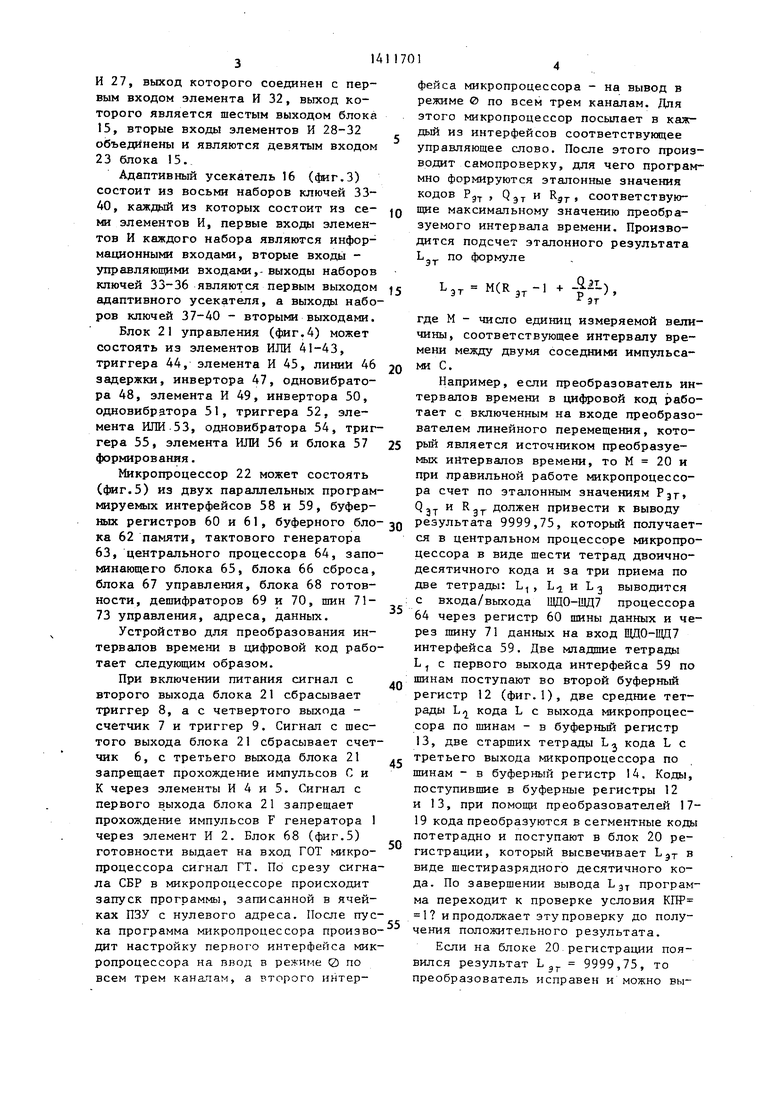

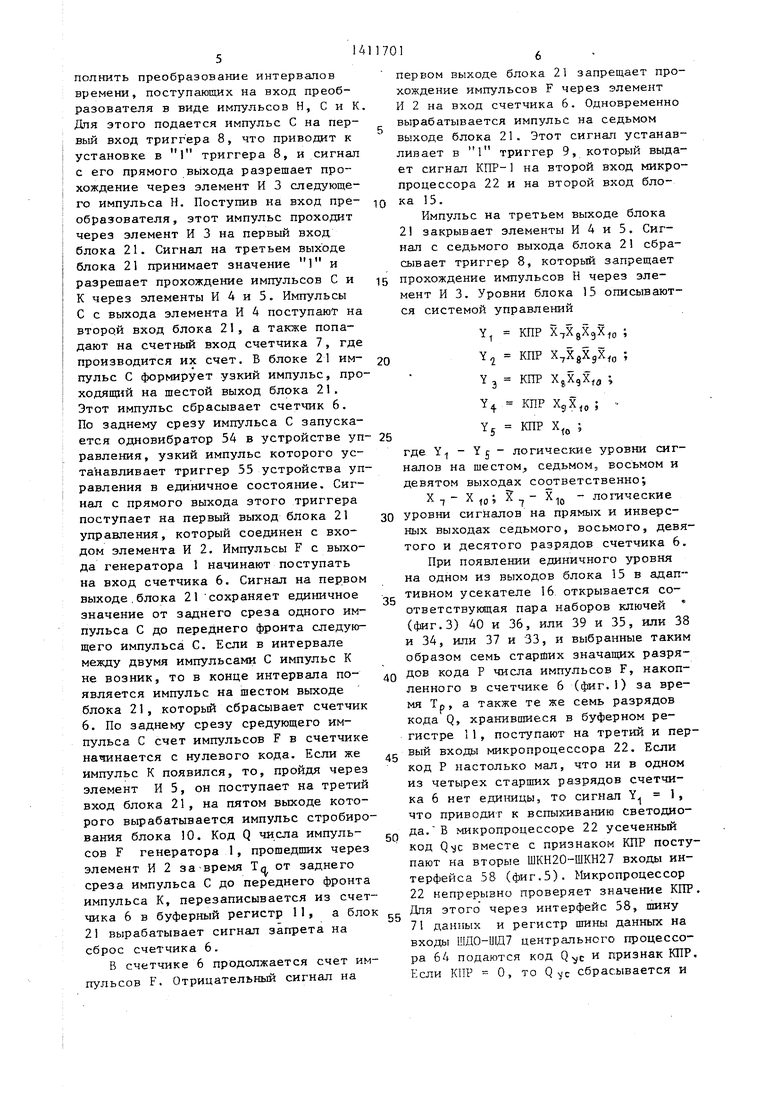

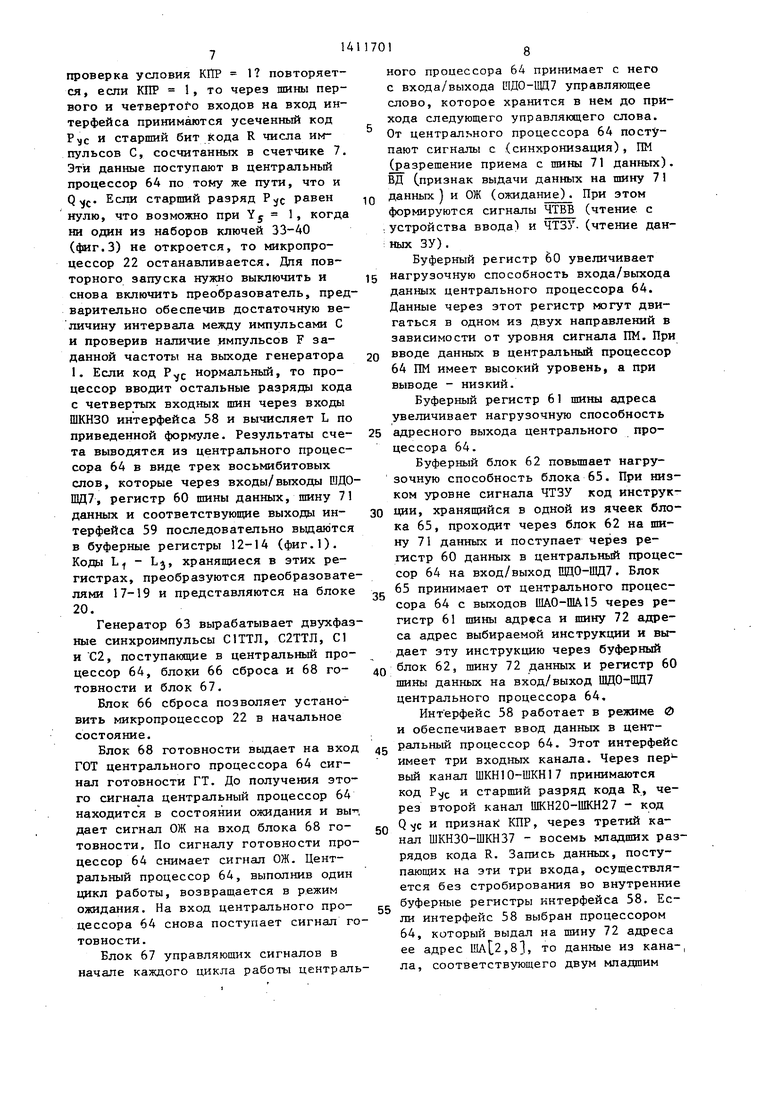

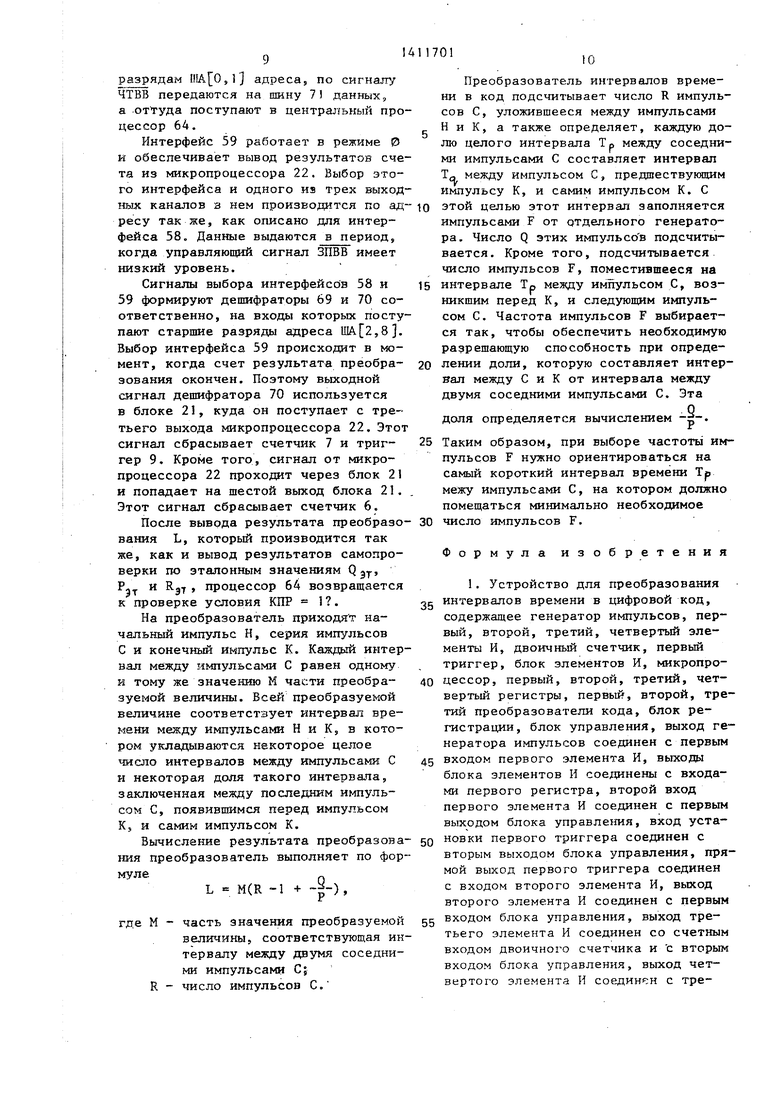

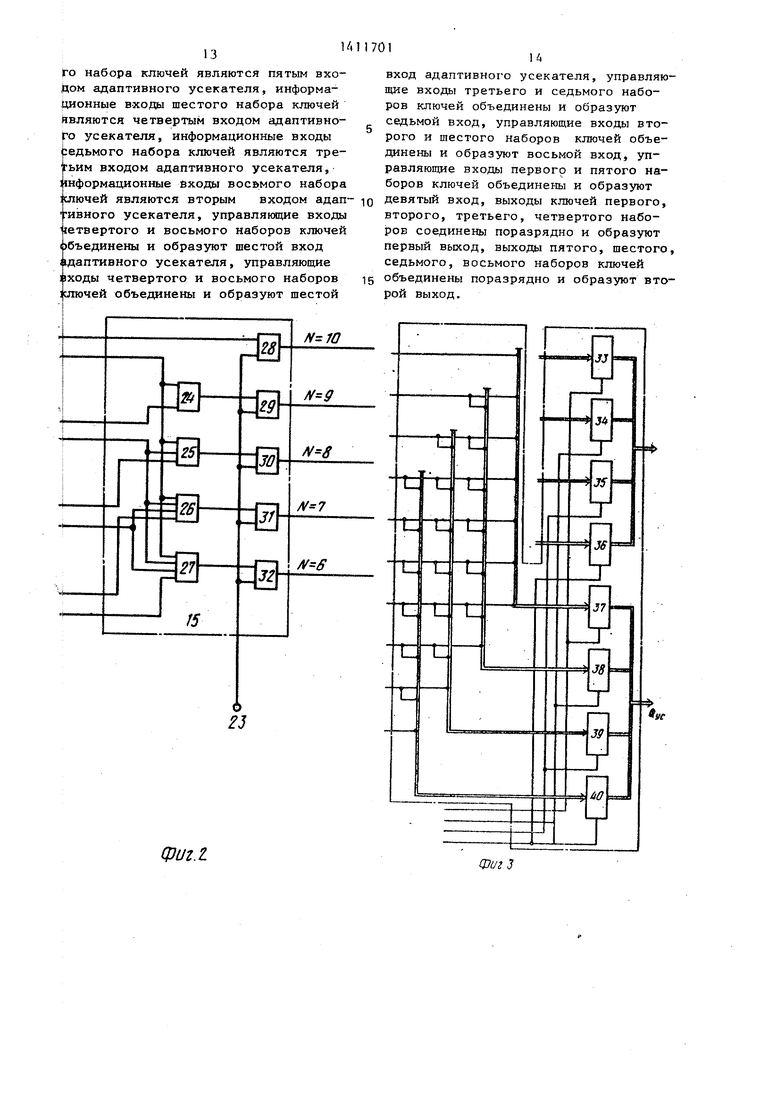

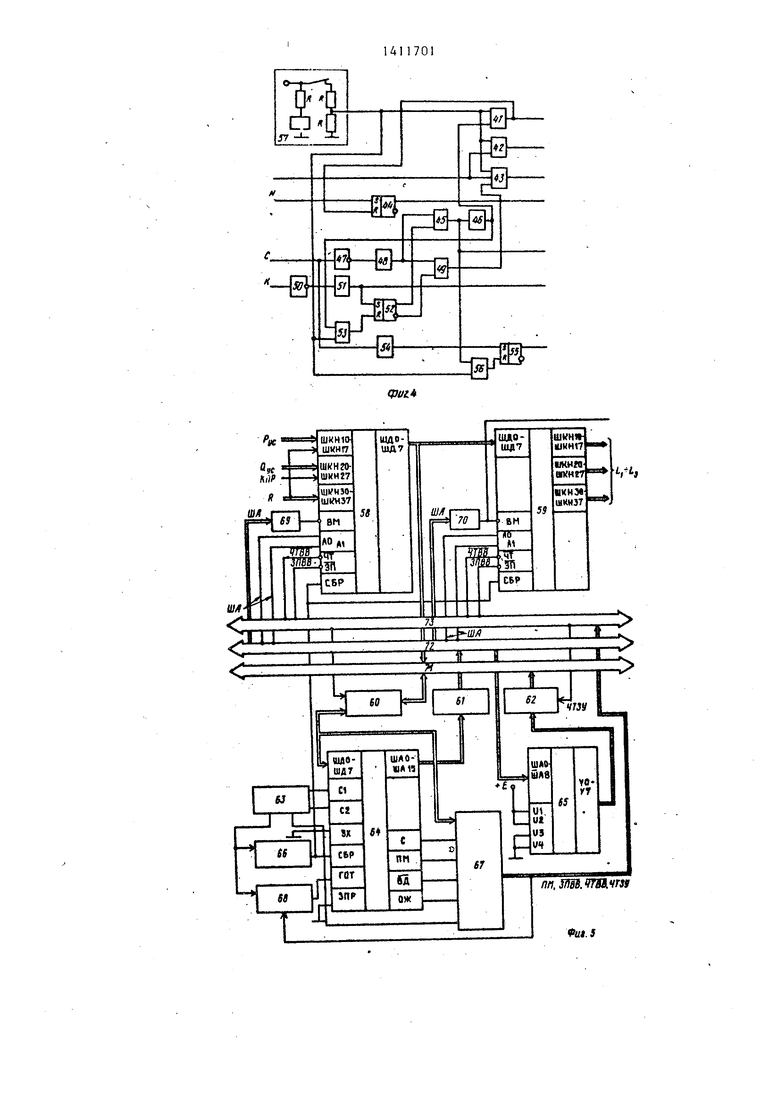

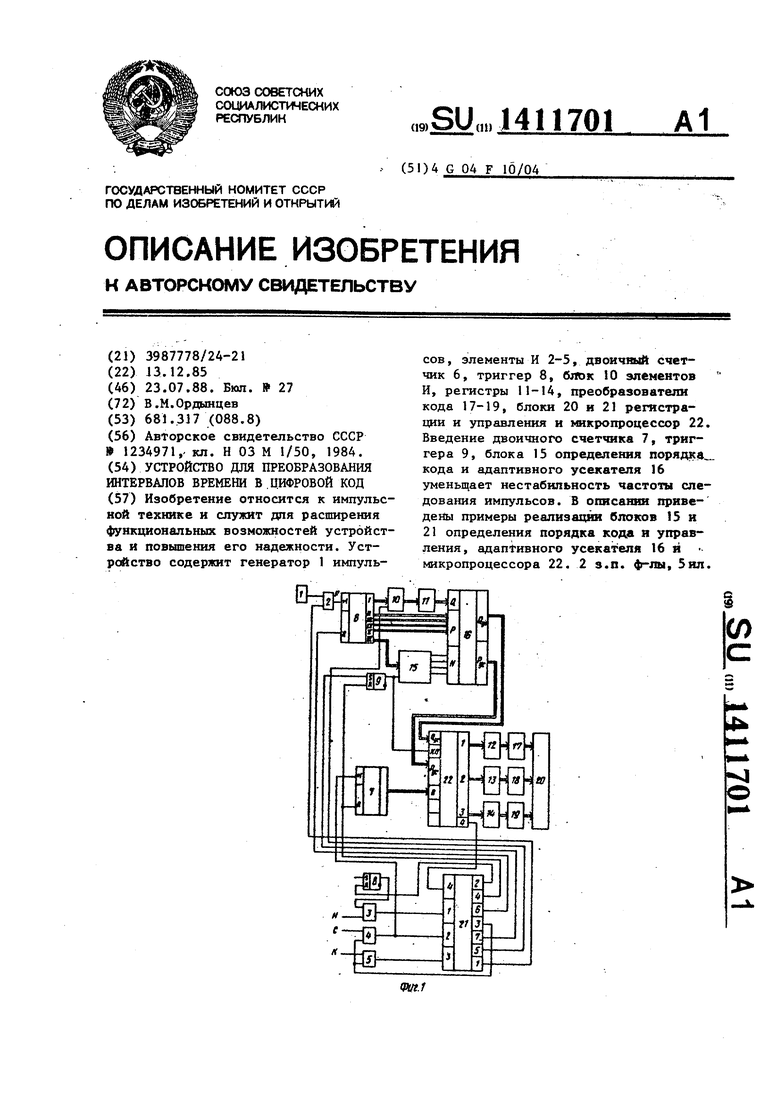

На фиг.1 представлена структурная схема устройства для преобразования интервалов времени в цифровой код; на фиг.2 - схема блока определения порядка кода; на фиг.З - схема адаптивного усекателя кодов; на фиг.4 - схема блока управления; на фиг.5 - схема микропроцессора.

Устройство (фиг.1) состоит из генератора 1 импульсов, первого, второго, третьего и четвертого элементов И 2-5, первого и второго двоичных счетчиков 6 и 7, первого и второго триггеров 8 и 9, блока 0 элементов И, первого, второго, третьего и четвертого регистров 11-14, блока 15 определения пйрядка кода, адаптивного, усекателя 16, первого, второго и третьего преобразователей 17-19 кода блока 20 регистрации, блока 21 управления и микропроцессора 22.

Выход генератора 1 соединен с первым входом первого элемента И 2, выход которого соединен со счетным входом счетчика 6, первый выход счетчика 6 соединен с информационным BXQ- дом блока 10, второй, третий, четвертый и пятый вьжоды счетчика 6 соединены с вторым, третьим, четвертым и пятым входами адаптивного усекателя 16, шестой выход счетчика 6 соединен с первым входом блока 15, выходы блока 10 соединены с входами регистра 1 выходы которого соединены с первым входом адаптивного усекателя 16, первый, второй, третий и четвертый выходы блока 15 соединены с шестым, седьмым, восьмым и девятым входами усекателя 16 соответственно, первый выход усекателя 16 соединен с первым входом микропроцессора 22, второй выход усекателя 16 - с третьим входом микропроцессора 22, прямой выход триггера 9 соединен с вторым входом микропроцессора 22, четвертый вход которого соединен с выходом счетчика 7, первый - с входом регистра 12, второй выход - с входом регистра 13, а третий выход - с входом регистра 14, выход регистра 12 соединен с входом преобразователя 17, вьтод регист0

5

0

5

0

5

0

5

0

5

ра 13 - с входами преобразователя 18, выход регистра 14 - с входом преобразователя 19, выходы преобразователей 17-19 соединены соответственно с первым, вторым и третьим входами блока 20, первый вход триггера 8 является входом установки в 1 триггера 8, прямой выход триггера 8 соединен с первым входом элемента И 3, второй вход которого является входом Н устройства, первый вход элемента И 4 является входом С устройства, первый вход элемента И 5 - входом К устройства, четвертый выход микропроцессора 22 соединен с четвертым входом блока 21, выход элемента И 3 соединен с первым входом блока 21, выход элемента И 4 - с вторым входом блока 21, выход элемента И 5 - с третьим в ходом блока 21 , первый выход блока 21 соединен с входом элемента И 2, второй выход блока 21 - с входами сброса в о триггера 8, третий выход блока 21 - с вторыми входа ет элементов И 4 и 5, четвертый выход блока 21 - с входами сброса в О триггера 9 и счетчика 7,, пятый выход блока 21 - с вторым входом блока 10., шестой выход блока 2 - с входом сброса счетчика 6, седьмой выход блока 21 - с входом установки в 1 триггера 9.

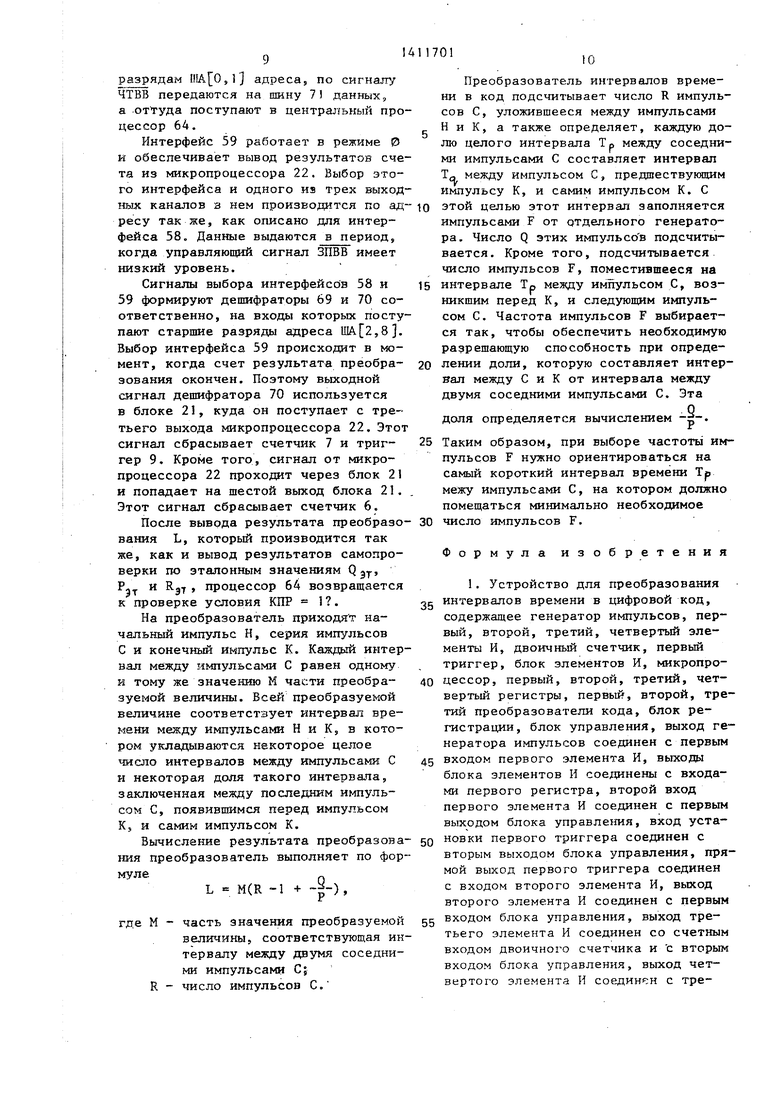

Блок 15 (фиг.2) содержит элементы И 24-32. Первый вход блока 15 соеди ней с первым входом элемента И 28, выход которого является первым выходом блока 15, второй вход блока 15 соединен с первыми входами элементов И 24-27, третий вход блока 15 - с вторым входом элемента И 24, выход которого соединен с первым входом элемента И 29, выход которого является вторым выходом блока 15, четвертый вход блока 15 соединен с вторыми входами элементов И 25-27,, пятый вход блока 15 соединен с третьим входом элемента И 25, выход которого соединен с первым входом элемента И 30, выход которого является третьим выходом блока 15, шестой вход блока 15 соединен с третьими входами элементов И 26 и 27, седьмой вход блока 15 - с четвертым входом элемента И 26, выход которого соединен с первым входом элемента И 31, выход которого является четвертым выходом блока 15, восьмой вход блока 15 соединен с четвертьЕМ входом элемента

И 27, выход которого соединен с первым входом элемента И 32, выход которого является шестым выходом блока 15, вторые входы элементов И 28-32 объединены и являются девятым входом 23 блока 15.

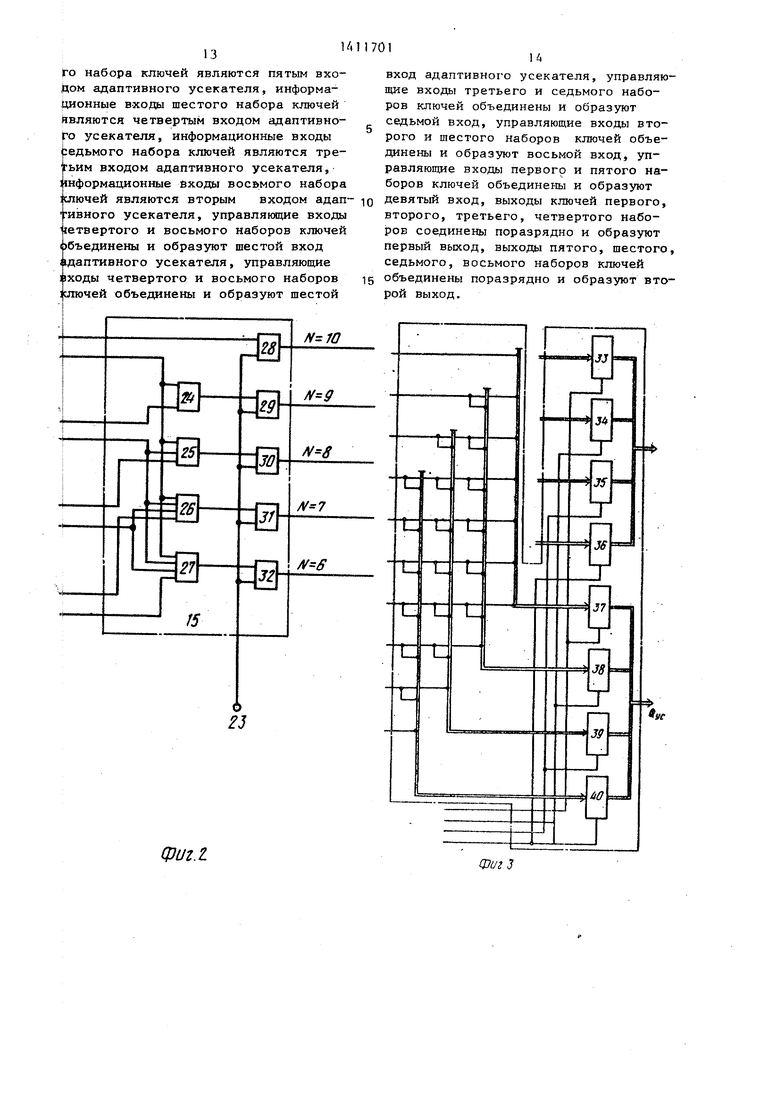

Адаптивный усекатель 16 (фиг.З) состоит из восьми наборов ключей 33- 40, каждый из которых состоит из семи элементов И, первые входы элементов И каждого набора являются информационными входами, вторые входы - управпякпу мк входами,-выходы наборов ключей 33-36 являются первым выходом адаптивного усекателя, а выходы наборов ключей 37-40 - вторыми выходами.

Блок 21 управления (фиг.4) может состоять из элементов ИЛИ 41-43, триггера 44, элемента И 45, линии 46 задержки, инвертора 47, одновибрато- ра 48, элемента И 49, инвертора 50, одновибр&тора 51, триггера 52, элемента ИЛИ 53, одновибратора 54, триггера 55, элемента ИЛИ 56 и блока 57 формирования.

Микропроцессор 22 может состоять (фиг.5) из двух параллельных програм- мируемьпс интерфейсов 58 и 59, буферных регистров 60 и 61, буферного блока 62 памяти, тактового генератора 63, центрального процессора 64, запоминающего блока 65, блока 66 сброса, блока 67 управления, блока 68 готовности, дешифраторов 69 и 70, шин 71- 73 управления, адреса, данных.

Устройство для преобразования интервалов времени в цифровой код работает следующим образом.

При включении питания сигнал с второго выхода блока 21 сбрасывает триггер 8, а с четвертого выхода - счетчик 7 и триггер 9. Сигнал с шестого выхода блока 21 сбрасывает счетчик 6, с третьего выхода блока 21 запрещает прохождение импульсов С и К через элементы И 4 и 5. Сигнал с первого выхоца блока 21 запрещает прохождение импульсов F генератора 1 через элемент И 2. Блок 68 (фиг.5) готовности выдает на вход ГОТ микропроцессора сигнал ГТ. По срезу сигнала СВР в микропроцессоре происходит запуск программы, записанной в ячейках ПЗУ с нулевого адреса. После пуска программа микропроцессора производит настройку первого интерфейса микропроцессора на ввод в режиме 0 по всем трем канатам, а второго интер

фейса микропроцессора - на вывод в режиме 0 по всем трем каналам. Для этого микропроцессор посылает в каждый из интерфейсов соответствукнцее управляющее слово. После этого производит самопроверку, для чего программно формируются эталонные значения кодов Pj , Qj и Rgi-, соответствующие максимальному значению преобразуемого интервала времени. Производится подсчет эталонного результата

L по формуле

эт

M(R

ЭТ

-1 .

),

0

5

0

5

0

5

0

5

где М - число единиц измеряемой величины, соответствующее интервалу времени между двумя соседними импульса- мк С.

Например, если преобразователь интервалов времени в цифровой код работает с включенным на входе преобразователем линейного перемещения, кото- рьш является источником преобразуемых интервалов времени, то М 20 и при правильной работе микропроцессора счет по эталонным значениям Pjr Qj и Rg должен привести к выводу результата 9999,75, который получается в центральном процессоре микропроцессора в виде шести тетрад двоично- десятичного кода и за три приема по две тетрады: L, L и L выводится с входа/выхода ШДО-ШД7 процессора 64 через регистр 60 шины данных и через шину 71 данных на вход ПЩО-ВД7 интерфейса 59. Две младшие тетрады L с первого выхода интерфейса 59 по шинам поступают во второй буферный регистр 12 (фиг.1), две средние тетрады L кода L с выхода микропроцессора по шинам - в буферный регистр 13, две старших тетрады L кода L с третьего выхода микропроцессора по шинам - в буферный регистр 14. Коды, поступившие в буферные регистры 12 и 13, при помощи преобразователей 17- 19 кода преобразуются в сегментные коды потетрадно и поступают в блок 20 регистрации, который высвечивает в виде шестиразрядного десятичного кода. По завершении вывода Lj программа переходит к проверке условия КПР 1 и продолжает эту проверку до получения положительного результата.

Если на блоке 20 регистрации появился результат L 9999,75, то преобразователь исправен и можно вы

полнить преобразование интервалов времени, поступающих на вход преобразователя в виде импульсов Н, С и К Дпя этого подается импульс С на первый вход триггера 8, что приводит к установке в l триггера 8, и сигнал с его прямого выхода разрешает прохождение через элемент И 3 следующего импульса Н. Поступив на вход преобразователя, этот импульс проходит через элемент И 3 на первый вход блока 21. Сигнал на третьем выходе блока 21 принимает значение 1 и разрешает прохождение импульсов С и К через элементы И 4 и 5. Импульсы С с выхода элемента И 4 поступают на второй вход блока 21, а также попадают на счетный вход счетчика 7, где производится их счет. В блоке 21 импульс С формирует узкий импульс, проходящий на шестой выход блока 21. Этот импульс сбрасывает счетчик 6. По заднему срезу импульса С запускается одновибратор 54 в устройстве уп равления, узкий импульс которого устанавливает триггер 55 устройства управления в единичное состояние. Сигнал с прямого выхода этого триггера поступает на первый выход блока 21 управления, который соединен с входом элемента И 2. Импульсы F с выхода генератора 1 начинают поступать на вход счетчика 6. Сигнал на первом выходе,блока 21 сохраняет единичное значение от заднего среза одного импульса С до переднего фронта следующего импульса С. Если в интервале между двумя импульсами С импульс К не возник, то в конце интервала появляется импульс на шестом выходе блока 21, который сбрасывает счетчик 6. По заднему срезу средующего импульса С счет импульсов F в счетчике начинается с нулевого кода. Если же импульс К появился, то, пройдя через элемент И 5, он поступает на третий вход блока 21, на пятом выходе которого вьфабатывается импульс стробиро вания блока 10. Код Q числа импульсов F генератора 1, прошедших через элемент И 2 за-время Тя от заднего среза импульса С до переднего фронта импульса К, перезаписывается из счетчика 6 в буферный регистр 11, а бло 2 вырабатывает сигнал запрета на сброс счетчика 6.

В счетчике 6 продолжается счет им ггульсов F, Отрицательный сигнал на

первом выходе блока 21 запрещает прохождение импульсов F через элемент И 2 на вход счетчика 6. Одновременно вырабатывается импульс на седьмом выходе блока 21. Этот сигнал устанавливает в 1 триггер 9, который выдает сигнал КИР-1 на второй вход микропроцессора 22 и на второй вход блока 15.

Импульс на третьем выходе блока 2 закрывает элементы И 4 и 5. Сигнал с седьмого выхода блока 21 сбрасывает триггер 8, который запрещает прохождение импульсов Н через элемент И 3. Уровни блока 15 описываются системой управлений

Y - КИР X-jXftXuX- Q Y КПР X XgXgX o ; Y 2 КПР XjXgXjg ;

4 КПР ;

КПР X

to

где

YI - YS логические уровни сиг0

5

5

0

5

0

5

налов на шестом седьмом, восьмом и девятом выходах соответственно;

XTX

10 9

X

ю

- логические

уровни сигналов на прямых и инверсных выходах седьмого, восьмого, девятого и десятого разрядов счетчика 6.

При появлении единичного уровня на одном из выходов блока 15 в адаптивном усекателе 16 открывается со- ответствукщая пара наборов ключей (фиг.З) 40 и 36, или 39 и 35, или 38 и 34, или 37 и 33, и выбранные таким образом семь старших значащих разрядов кода Р числа импульсов F, накопленного в счетчике 6 (фиг.1) за время Тр , а также те же семь разрядов кода Q, хранившиеся в буферном регистре 11, поступают на третий и первый входы микропроцессора 22. Если код Р настолько мал, что ни в одном из четырех старших разрядов счетчика 6 нет единицы, то сигнал Y 1, что приводит к вспыхиванию светодио- да. В микропроцессоре 22 усеченный код QNJC вместе с признаком КПР поступают на вторые ШКН20-ШКН27 входы интерфейса 58 (фиг.5). Микропроцессор 22 непрерывно проверяет значение КПР. Дпя этого через интерфейс 58, шину 71 данных и регистр щины данных на входы ШДО-и1Д7 центргшьного процессора 64 подаются код и признак КПР. Если КПР О, то Q-jic сбрасывается и

проверка условия КПР 1 повторяется, если КПР 1, то через шины первого и четвертого входов на вход интерфейса принимаются усеченный код Рх(С и старший бит кода R числа импульсов С, сосчитанных в счетчике 7. Эти данные поступают в центральный процессор 64 по тому же пути, что и Q,j(. Если старший разряд равен нулю, что возможно при Yj 1, когда ни один из наборов ключей 33-40 (фиг.З) не откроется, то микропроцессор 22 останавливается. Для повторного запуска нулшо выключить и снова включить преобразователь, предварительно обеспечив достаточную ве- личину интервала между импульсами С и проверив наличие импульсов F заданной частоты на выходе генератора 1, Если код Р нормальный, то процессор вводит остальные разряды кода с четвертых входных шин через входы ШКНЗО интерфейса 58 и вычисляет L по приведенной формуле. Результаты счета выводятся из центрального процессора 64 в виде трех восьмибитовых слов, которые через входы/выходы ШДО- ВД7, регистр 60 шины данных, шину 71 данных и соответствующие выходы интерфейса 59 последовательно выдаются в буферные регистры 12-14 (фиг.1). Коды L - Lj, хранящиеся в этих регистрах, преобразуются преобразователями 17-19 и представляются на блоке 20.

Генератор 63 вырабатывает двухфазные синхроимпульсы С1ТТЛ, С2ТТЛ, С1 и С2, поступакщие в центральный процессор 64, блоки 66 сброса и 68 готовности и блок 67.

Блок 66 сброса позволяет установить микропроцессор 22 в начальное состояние.

Блок 68 готовности выдает на вход ГОТ центрального процессора 64 сигнал готовности ГТ. До получения этого сигнала центральный процессор 64 находится в состоянии ожидания и вы-, дает сигнал ОЖ на вход блока 68 готовности. По сигналу готовности процессор 64 снимает сигнал ОЖ. Центральный процессор 64, выполнив один цикл работы, возвращается в режим ожидания. На вход центрального процессора 64 снова поступает сигнал готовности.

Блок 67 управляющих сигналов в начале каждого цикла работы центрального процессора 64 принимает с него с входа/выхода ШДО-ЩД7 управляющее слово, которое хранится в нем до прихода следующего управляющего слова. От центрального процессора 64 поступают сигналы с (синхронизация), ПМ (р азрешение приема с шины 71 данных). БД (признак выдачи данных на шину 71

данных J и ОЖ (ожидание). При этом формируются сигналы ЧТВВ (чтение с ..устройства ввода) и ЧТЗУ. (чтение даи- i ных ЗУ).

Буферный регистр 60 увеличивает

5 нагрузочную способность входа/выхода данных центрального процессора 64. Данные через этот регистр могут двигаться в одном из двух направлений в зависимости от уровня сигнала ПМ. При

Q вводе данньт в центральный процессор

64ПМ имеет высокий уровень, а при выводе - низкий.

Буферный регистр 61 шины адреса увеличивает нагрузочную способность

5 адресного выхода центрального процессора 64.

Буферный блок 62 повьш1ает нагрузочную способность блока 65. При низком уровне сигнала ЧТЗУ код инструк0 ции, хранящийся в одной из ячеек блока 65, проходит через блок 62 на шину 71 данных и поступает через регистр 60 данных в центральный процессор 64 на вход/выход 1ЗДО-ШД7. Блок

65принимает от центрального процессора 64 с выходов 111АО-ША15 через регистр 61 шины адреса и шину 72 адреса адрес выбираемой инструкции и выдает эту инструкцию через буферный

Q блок 62, шину 72 данных и регистр 60 шины данных на вход/выход ШДО-ВД7 центрального процессора 64,

Интерфейс 58 работает в режиме О и обеспечивает ввод данных в центральный процессор 64. Этот интерфейс имеет три входных канала. Через вый канал ШКН10-ШКН17 принимаются код Рх(с и старший разряд кода R, через второй канал ШКН20-ШКН27 - код

Q vfc и признак КПР, через третий канал ШКНЗО-ШКН37 - восемь младших разрядов кода R. Запись данных, поступающих на эти три входа, осуществляется без стробирования во внутренние буферные регистры интерфейса 58. Если интерфейс 58 выбран процессором 64, который выдал на шину 72 адреса ее адрес ,8, то данные из кана-, ла, соответствующего двум мпадшим

5

45

55

разрядам ,lj адреса, по сигналу ЧТВВ передаются на шину 71 данных, а откуда поступают в центральный процессор 64,

Интерфейс 59 работает в режиме 0 и обеспечивает вывод результатов счета из микропроцессора 22. Выбор этого интерфейса и одного из трех выходных каналов з нем производится по яд ресу так же, как описано для интерфейса 58. Данные выдаются в период, когда управляющий сигнал ЗПВВ имеет низкий уровень.

Сигналы выбора интерфейсбв 58 и 59 формируют дешифраторы 69 и 70 соответственно, на входы которых поступают старшие разряды адреса ,8. Выбор интерфейса 59 происходит в момент, когда счет результата преобразования окончен. Поэтому выходной сигнал дешифратора 70 используется в блоке 21, куда он поступает с третьего выхода микропроцессора 22. Этот сигнал сбрасывает счетчик 7 и триггер 9. Кроме того, сигнал от микропроцессора 22 проходит через блок 21 и попадает на шестой выход блока 21. Этот сигнал сбрасывает счетчик 6.

После вывода результата преобразования L, который производится так же, как и вывод результатов самопроверки по эталонным значениям Р, и Rgf, процессор 64 возвращается к проверке условия КПР 1.

На преобразователь приходя т начальный импульс Н, серия импульсов С и конечный Импульс К. Каждый интервал между импульсами С равен одному и тому же значению М части преобразуемой величины. Всей преобразуемой величине соответствует интервал времени между импульсами Н и К, в котором укладываются некоторое целое число интервалов между импульсами С и некоторая доля такого интервала, заключенная между последним импульсом С, появившимся перед импульсом К, и самим импульсом К.

Вычисление результата преобразования преобразователь выполняет по формуле

L M(R -1 + ),

где М - часть значения преобразуемой величины, соответствующая интервалу между двзтя соседними импульсами С; R - число импульсов С.

Преобразователь интервалов времени в код подсчитывает число R импульсов С, уложившееся между импульсами Н и К, а также определяет, каждую долю целого интервала Тр между соседними импульсами С составляет интервал Т„ между импульсом С, предшествующим импульсу к, и самим импульсом К. С

этой целью этот интервал заполняется импульсами F от отдельного генератора. Число Q этих импульсо в подсчитывается. Кроме того, подсчитывается число импульсов F, поместившееся иа

интервале Тр между импульсом С, возникшим перед К, и следующим импульсом С. Частота импульсов F выбирается так, чтобы обеспечить необходимую разрешающую способность при определении доли, которую составляет интервал между С и К от интервала между двумя соседними импульсами С. Эта

доля определяется вычислением

Таким образом, при выборе частоты импульсов F нужно ориентироваться на самый короткий интервал времени Тр межу импульсами С, на котором должно помещаться минимально необходимое

число импульсов F.

Формула изобретения

1. Устройство для преобразования

интервалов времени в цифровой код, содержащее генератор импульсов, первый, второй, третий, четвертый элементы И, двоичный счетчик, первый триггер, блок элементов И, микропроцессор, первый, второй, третий, четвертый регистры, первый, второй, третий преобразователи кода, блок регистрации, блок управления, выход генератора импульсов соединен с первым

входом первого элемента И, выходы блока элементов И соединены с входа- a первого регистра, второй вход первого элемента И соединен с первым выходом блока управления, вход установки первого триггера соединен с

вторым выходом блока управления, прямой выход первого триггера соединен с входом второго элемента И, выход второго элемента И соединен с первым

входом блока управления, выход третьего элемента И соединен со счетным входом двоичного счетчика и с вторым входом блока управления, выход четвертого элемента И соедин ;н с третьим входом блока управления, входы третьего и четвертого элементов И соединены с третьим выходом блока управления , четвертьй выход блока управления соединен с входом сброса двоичного счетчика, пятый выход блоки управления соединен с управляющими входами блока элементов И, первый, второй, третий выходы микропроцессо- pa соединены соответственно с входами второго, третьего и четвертого регистров, выходы которых соответственно соединены с входами первого, второго, третьего преобразователей кода выходы которых соответственно соединены с входами блока регистрации, четвертый.выход микропроцессора соединен с четвертым входом блока управления, выход двоичного счетчика сое- динен с четвертым входом микропроцессора, отличающееся тем, что, с целью расщирения функциональных возможностей и повышения надежности, в него введены второй триггер второй двоичньй счетчик, блок определения порядка кода, адаптивный усека- тель, при этом выход первого элемента И соединен со счетным входом второго двоичного счетчика, шестой вы- ход блока управления соединен с бхо- дом сброса второго двоичного счетчика, седьмой выход блока управления соединен с входом установки второго триггера, четвертый выход блока уп- равления подключен к входу сброса второго триггера, прямой выход второго триггера соединен с первым входом блока определения порядка кода и

2. Устройство по П.1, отличающееся тем, что блок определения порядка кода состоит из первого, второго, третьего, четвертого, пятого, шестого двухвходовых, одного трехвходового и первого, второго че- тырехвходовых элементов И, первьй вход блока определения порядка кода соединен с четвертым входом первого четырехвходового элемента И, второй вход - с четвертым входом второго четырехвходового элемента И, третий вход соединен с третьими входами первого и второго четырехвходовых элементов И, четвертьй вход соединен с третьим входом трехвходового элемента И, пятьй вход - с вторыми входами первого и второго четырехвходовых и трехвходового элемента И, шестой вход соединен с вторым входом первого двухвходового элемента И, седьмой вход соединен с первыми входами пер-з вого и второго четырехвходовых, трехвходового и первого двухвходового элементов И, восьмой вход соединен с первым входом шестого двухвходового элемента И, кроме того, выходы первого двухвходового, трехвходового, второго и первого четырехвходовых элементов И соединены соответственно с первыми входами пятого, четвертого, третьего и второго двухвходовых элементов И, выходы второго, третьего, четвертого, пятого, шестого двухвходовых элементов И являются соответственно первым, вторым, третьим, четвертым, пятым выходами блока определения порядка кода, а вторые входы

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1234971A1 |

| Адаптивная цифровая система управления электроприводом | 1985 |

|

SU1315938A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для записи информации | 1978 |

|

SU907535A1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2012 |

|

RU2486581C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Резервированная вычислительная система | 1989 |

|

SU1691991A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

Изобретение относится к импульсной технике и служит для расширения функциональных возможностей устройства и повышения его надежности. Устройство содержит генератор 1 импульсов, элементы И 2-5, двоичный счетчик 6, триггер 8, блок 10 элементов И, регистры 11-14, тфеобразователи кода 17-19, блоки 20 и 21 регистрации и управления и микропроцессор 22. Введение двоичного счетчика 7, триггера 9, блока 15 определения порядка, кода и адаптивного усекателя 16 уменьшает нестабильность частоты следования импульсов. В описании приве- деШл примеры реализации блоков 15 и 21 определення порядка кода я управления, адаптивного усекаТеля 16 и микропроцессора 22. 2 з.п. ф-лы, 5ил.

с вторым входом микропроцессора, пер- 40 которых объединены и являются первым

выи выход второго двоичного счетчика соединен с информационным входом блока элементов И, второй, третий, четвертый, пятый выходы второго двоичного счетчика соединены соответственно с вторым, третьим, четвертым, пятым входами адаптивного усекателя, шестой выход второго двоичного счетчика соединен с вторым входом блока определения порядка кода, первый, второй, третий, четвертый выходы блока определения порядка кода соответственно соединены с шестым, седьмым, восьмым, девятым входами адаптивного усекателя, первый выход которого соединен с первым входом микропроцессора, а второй выход соединен с третьим входом микропроцессора.

входом блока определения порядка кода.

овышения надежности, адаптивный усе- катель содержит первый, второй,, третий, четвертый, пятый, шестой, седьмой и восьмой наборы ключей, первый вход адаптивного усекателя содержит

девять шин, причем шины с первой по седьмую соединены с входами первого набора ключей, шины с второй по восьмую соединены с входами второго набора ключей, шина с третьей по девятую

соединены с входами третьего набора ключей, шины с четвертой по десятую соединены с входами четвертого набора ключей, информационные входы пятоГо набора ключей являются пятым вхо- Дом адаптивного усекателя, информа- :Ционные входы шестого набора ключей Являются четвертым входом адаптивно о усекателя, информационные входы седьмого набора ключей являются третьим входом адаптивного усекателя, информационные входы восьмого набора ючей являются вторым входом адапИ1вного усекателя, управляющие входы четвертого и восьмого наборов ключей объединены и образуют шестой вход адаптивного усекателя, управляющие иходы четвертого и восьмого наборов слючей объединены и образуют шестой

г:: I

фиг..

вход адаптивного усекателя, управляющие входы третьего и седьмого наборов ключей объединены и образуют седьмой вход, управляющие входы второго и шестого наборов ключей объединены и образуют восьмой вход, управляющие входы первого и пятого наборов ключей объединены и образуют

девятый вход, выходы ключей первого, второго, третьего, четвертого наборов соединены поразрядно и образуют первый выход, выходы пятого, шестого, седьмого, восьмого наборов ключей

объединены поразрядно и образуют второй выход.

tl

t:

П

П

ФигЗ

Яил1-1

JULktMJL-js.

ft/. 5

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1234971A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-07-23—Публикация

1985-12-13—Подача