(54) ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА -В КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1977 |

|

SU669374A1 |

| Преобразователь угла поворота вала в код | 1978 |

|

SU771115A2 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Двухотсчетный преобразователь углового перемещения в цифровой код | 1977 |

|

SU651389A2 |

| Двухотсчетный преобразователь углапОВОРОТА ВАлА B КОд | 1979 |

|

SU840995A1 |

| Преобразователь угол-код | 1979 |

|

SU801020A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU732955A1 |

| Преобразователь угла поворота вала в код | 1976 |

|

SU643937A1 |

| Двухотчетный преобразователь углового перемещения в цифровой код | 1975 |

|

SU526932A1 |

| Преобразователь угла поворотаВАлА B КОд | 1979 |

|

SU813487A1 |

Изобретение относится к автоматике и вычислительной технике, может быть использовано для преобразования угла поворота вала в код. Известен преобразователь углового положения вала в цифровой код, содержащий врапдающийся трансформатор, соединенный со входами сумматоров, выходы которых через фазочувствительные выпрямители подключены к первым входам вентилей, вт.орые входы которых подключены к выходу генератора импульсов, а выходы соединены через реверсивный счетчик и преобразователь «код-напряжение 1. Недостатком этого устройства является малая точность. Наиболее близок к предлагаемому преобразователь угла поворота вала в код, содержащий преобразователь напряжения в частоту, три формирователя синусоидального сигнала, фазовый синхронный детектор, задающий генератор, выход которого подключен ко входам двух делителей частоты, выход первого делителя частоты соединен со входом первого дещифратора, два выхода которого через формирователи синусоидального сигнала подключены ко входам синусно-косинусного вращающегося трансформатора, выход блока управления подключен ко входу реверсивного счетчика, выход которого соединен со входом блока ввода кода, выход блока ввода кода подключен ко второму входу второго делите т частоты, выход которого соединен со входом второго дещифратора, выход первого делителя частоты через формирователь импульса ввода кода подключен к управляющему входу блока ввода кода 2|. Недостаток устройства - низкая точность преобразования угла поворота вала в код и низкая разрещающая способность преобразователя, которые объясняются нелинейностью преобразования, температурной нестабильностью элементов и трудностью реализации работы преобразователя с высокой частотой задающего генератора. Цель изобретения - повыщение точности и разрещающей способности преобразователя угла поворота вала в код. Согласно изобретению поставленная цель достигается тем, что в устройство введены интегратор, четвертый формирователь синусоил,.1,;1ьного CHiH;i..i;i, 6:i()K с|1 1В11ения, и: онраге.1ЬН1)1Й уси,:1ИГ(.1ь, порогошяи , yiipaiiляемый ;и 1Нге..1ь игшря/кония, iipcHJnjja.uHui тс,1ь «код- 1апряжен.не, амплитудный синхронный легект()|1 II суммируюник блок, нериый выход второсо лен1ис()рат))а че)еи г 5гтий фо)мир()вате,11 синусоида.и)Н()1Ч) напряжения подк.мючен к 11е)В()му нхолх суммнруюнкмО блока, второй выход второго ден(ифрагора через четвертьн (|)())мнр()вате/1ь ениуеоидального сигнала соединен с первым входом преобразователя «код --напряжение, второй вход которого нодк.люче.н к выходу младших разрядов реверсивного счетчика, а выход преобразователя «код- напряжение нодключен ко второму входу суммнруюнимч) блока, В111ход которого че)ез унрав.пяемый де.мнтель нан|)яже1Н1я 11одклн)Ч1Ч1 к нервому входу блока сравнения, второй вход блока сравнения, нодключен к выходу синусно-косинусного враи1аю цегося трансформатора, выход блока сравнения через избиратель 1ый усилитель подключен ко входам фазового и амплитудного cHHxpo}iHi ix детекторов, выход фазового сппхропного детектора подк.почен ко входам н| еобразователя напря/кепня в частоту н норогового б.юка, выходы которых нодк.почепы ко входам б.юка ун)ав.1ения, выход .П1тудно1Ч) синхрогнюго детект())а через ннтеграто) соединен ео вто|)ым входом унрав,1яемо1о де,1ите.1я панряж(чн1я, третий н четвер1Ы11 1я 1ход| | ргго|К)го дении( ратора нодк.почены ко вторым входам амнлнтудпого и с|)азового сннхрон1и 1х дегекто)ОВ.

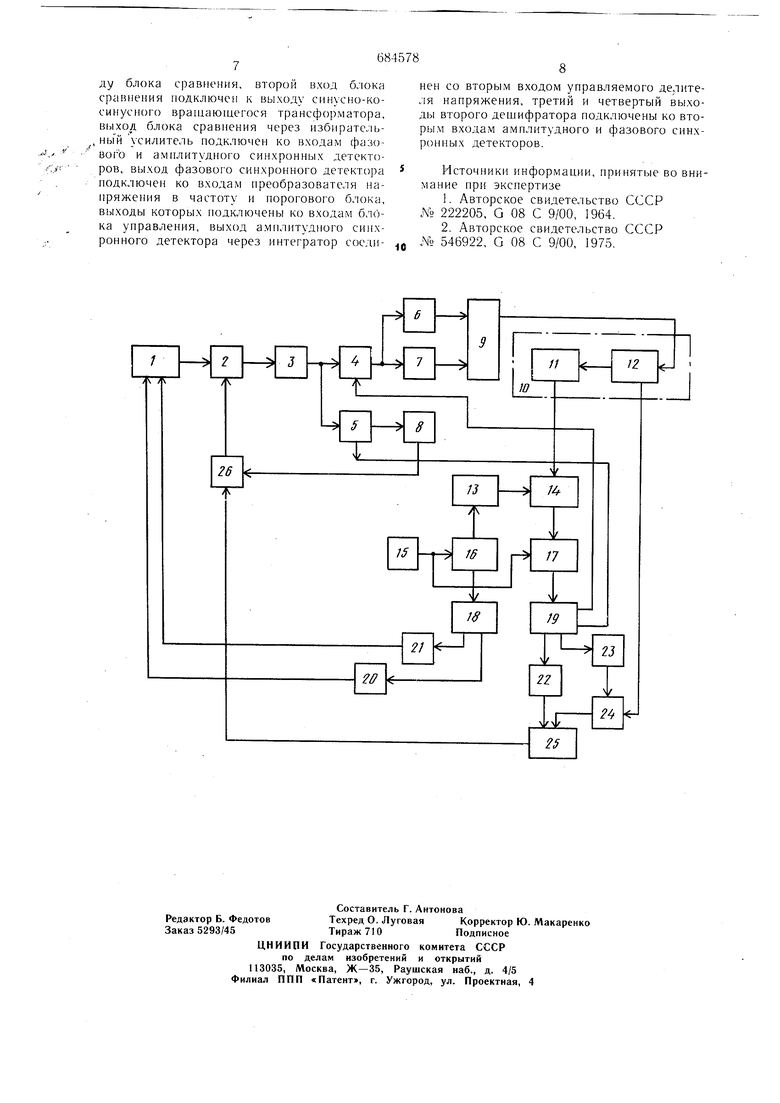

Па чертеже приведена структурная лектрнческая схема устройства. ГТреобразователь содержнт сннусно-косннусный враи1ак)1цийся трансформатор (СКВТ) 1, блок сравнення 2, нзбирате.чыняй усилитель 3, с)азоВ1)1Й синхронный детектор 4, амплитудный еинхронный детектор 5, преобразователь напряжения в частоту 6, пороговый блок 7, интегратор 8, блок 9 управления реверснвtn iM счетч11ком 10 со старнп1ми и младпиши разрядами 11 н 12 соответственно, формирователь 13 импульса ввода кода, блок 4 ввода кода, задающий генератор 15, делители частоты 16 и 17, дешифраторы 18 и

19,формирователи синусоидальных сигналов 20-23, преобразователь «код-напряжение 24, суммирующий блок 25, управляемый делитель напряжения 26.

Выход задаюн 1его генератора 15 подключен ко входам делителей частоты 16 и 17, выход делителя 16 через дешифратор 18 н формирователи синусоидального сигна:1а

20,21 нодключен ко входам синусно-косинусного вращающегося трансформатора 1.

Выход блока сравнения 2 через реверсивный счетчик 10, блок ввода кода 14 и делитель частоты 17 соединен со входом дешифратора 19.

В1з1ход делителя частоты 16 через формирс ватель импульса ввода кода 13 подключен к унравляюп;ему входу блока ввода кода 14. Первый выход деп нфратора 19 че()ез формирователь синусоидального напряжения 22 подключен к первому входу суммируюп1его блока 25, второй выход де1пнфратора 19 через формирователь синусоидального сигнала 23 соединен с одним из входов преобразователя «код-напряжение 24, второй вход которого нодключен к выходу младншх разрядов 12 реверсивного счетчика 10, а вход нреобразователя «код-няпрежние 24 нодключен ко второму входу сумм11руюн1его блока 25, выход последнего через управ.1яемый делитель напряжения 26 нодключен к одному из входов блока сравнения 2.

Второй вход блока сравнения 2 подключен к выходу еинусно-коеинусн(Ло вращаюН1ег()ся трансформатора 1, а выход блока сравне(П1я 2 через избирательный усилитель 3 подк„1ючен ко входам синхронных детекторов 4 и 5. Выход фазов(;го синхронного детектора 4 подключен ко входам преоб|)азовате.1я напряжения в частоту 6 н порогового блока 7, а их выходы подключены ко входам блока управления 9. Выход амплитудного синхронного детектора 5 через интегратор 8 соединен со вторым входом унравляеMoio делителя напряжения 26. Третий н чет Нртый выходы ден1ифратора 19 подключены ко вторым входам синхронных детекторов.

Устройство работает с.чедчющим образом.

СКВТ 1 иреобразует у1ол поворота вала в напряжение, фазовый сдвиг которого пропор 1нонален углу поворота ва:1а. Напряжение с выходной обмотки СКВТ I поступает на блок сравнения 2, в котором складывается в противофазе с комненсируюп1им сигналом, вырабатывае.мы.м совокунностью блоков 10-26. В результате сложения выделяется и усиливается первая гармоника напряжения питания СКВТ 1, несущая информапию как о фазовом, так и об амплитудном разбалансе сравниваемых напряжений. Избирательный усилитель 3 в цепи выделения рассогласования по фазе определяет постоянную времени, характеризующую динамическую характеристику преобразорателя, которая до некоторых пределов линейно зависит от скорости изменения угла ротора СКВТ и исключается раснп-фением динамического диапазона нреобразователя напряжения в частоту 6.

Выделенная и усиленная в результате сравнения первая гармоника, равная частоте питания, попадает на фазовый и амплитудный синхронные детекторы 4 и 5. Следует отметить, что онорные напряжения для детекторов фор.мируются из компенсирующего канала, жестко связаны с ним но фазе, а друг относительно друга сдвинуты на 90°. Детектор 5 выделяет напряжение, пронорциональное величине рассог,:1асован1 я по фазе, знак н ве.шчина его оире;1е.1ян)т режим раб(т1)1 АЦПУ, т. е. с.южение или вычитание имнульеов от иреобразователя напряжения в чаетотч (i. Пороговый блок 7 в совокупности с блоком унрав.лепня 9 вырабатывают команды режима работы реверсивного счетчика 10. Амплитудный сипхро.чпый детектор 4 1 ыделяет напряжение, пронорпнона.чьное ве.чичнпе амплитудного разбаланса сравинваемых напряжений, которое через интегратор 8 подается на управляющий вход управляемого делителя напряжения 26.

Заполнение реверсивного счетчика 10 иродолжается до тех нор, пока фазовый сдвиг между напряжениями в блоке сравнения не станет равным 180. По мере уменьишния ())азового разбаланса уменьп1ается частота запо.тнения счстчика К), а ко.кюательный режим у по,1ожения равновесия исключается с помощью nopoiOBoro б.юка 7, порог чувствительности которого лолжеп быть равН1)1м половине цепы м,1адп1его разряда. От задаюн1его генератора 15 импульсы пост нают на делители частоты 16 п 17 с одинаковыми коэффициентами дсччеиия. Информация с трех последних разрядов делителей частоты поступает на ден1ифраторы 18 и 19, которые формируют времешиле участки.

Синусоидальный сигнал формируется путе.м кусочно-линейной аппроксимации. Сфор.мироваипые и усиленпые напряжения с формирователей еинусоидального сигнала 20 и 21 подаются на первичные (статорные) обмотки СКВТ 1.

Фаза компенсационного напряжения изменяется путем ввода начального числа в делитель частоты 17 (один раз за период формируемого сигнала). Число, записанное в старших разрядах реверсивного счетчика 10, через блок ввода кода 14 записывается в делитель частоты 17 в момент, когда в делителе частоты 16 все триггеры переходят из состояния «1 и «О. Данный момент фиксируется формирователе.м и.мпульса ввода кода 13, который вырабатывает короткий импульс для записи числа в делитель частоты 17. Дешифратор 19 и формирователи синусоидального сигнала 22 н 23 работают аналогично узлам 18, 20, 21. Квадратурная составляющая, снимаемая с формирователя синусоидального сигнала 23, подается на преобразователь «код-напряжение 24, амплитуда сигнала с которого определяется числом, записанным в младших разрядах 12 реверсивного счетчика 10. На выходе суммируюш,его блока 25 после сложения получается напряжение, фаза которого зависит от числа, записанного в реверсивном счетчике.

При изменении числа в младших разрядах 12 счетчика 10 происходят малые изменения фазы компенсирующего напряжения.

сппмае. с суммируюпкмо о/ияч;; 2о. 115менение же числа в старпп1 рал)ядах хотя бы па еди1П1цу скачкоопразпое нз.менепие фазы KOMiiei;ciii ) напряж ПИЯ. Ами,1итудпьп1 ciiiixiioiiH:, детектор 5 выделяет напряжение, npnniipuiiona.ibnoe велпчппе амплптудного 1/азГ)а.1апса, которое через интегратор 8 подается на нрав.)П1 делитель напряжения 2(), KOTo|) измспяе; амплитуду компенсирукмцего напряжения, пс)етупаюп1его па один из вхо.юв б.кжа сравнения 2. Комненсапня сигнала, гцюпорпионального а 1плитудпому разбалапсу ипформацпонного и компенсационного нанряжений, в тракте выяв.чення фазового разбаланса между указанными напряжениями нозволяет повысить разреп1аю1цую способность и точность аналого-цифрового нреобразователя.

Формула изобретения

Преобразователь упа новорота вала в код, содержащий преобразователь напряжения в частоту, три формирователя синусоидального сигна,1а, фазовый синхронный детектор, задающий генератор, выход которого подключен ко входам двух де,1ите,тей частоты, выход первого делителя частоты соединен со входом первого дешифратора, два выхода которого через формирователи синусоидального сигнала подключены ко входам сипусно-косинусного вращающегося трансформатора, выход блока управления подключен ко входу реверепвпого счетчика, выход которого соединен со входом реверсивного счетчика, выход которого соединен со входом второго делителя частоты, выход которого соединен со входом второго дешифратора, выход первого делителя частоты через формирователь импульса ввода кода подключен к управляющему входу блока ввода кода, отличающийся тем, что, с целью повышения его точности и разрешающей способности, в него введены интегратор, четвертый формирователь синусоидального сигнала, блок сравнения, избирательный усилитель, пороговый блок, управляемый делитель напряженпя, преобразователь «кодпапряжение, амплитудный синхронный детектор и суммирующий блок, первый выход второго дещифратора через третий формирователь синусоидального напряжения подключен к первому входу суммирующего блока, второй вы.ход второго дещифратора через четвертый формирователь синусоидального сигнала соединен с первым входом преобразователя «код-напряжение, второй вход которого подключен к выходу младших разрядов реверсивно1о счетчика, а выход преобразователя «код-напряжение подключен ко второму входу сумм}1руюшего блока, выход которого через yпpaвляe ПзIЙ делитель напряжения подключен к первому входу блока сравнения, второй вход блока срав 1ения подключен к выходу синусно-косинуеного вращаюшегчхя трансформатора, выход блока сравнения через нзбиратель, ный усилитель подключен ко входам фазового и амнлитудногч) синхронных детекторов, выход фазового синхронного детектора подключен ко входам преобразователя нанряження в частоту и порогового блока, выходы которых подключены ко входам блока управления, выход амплитудного синхронного детектора через интегратор соединен со вторым входом управляемого делите.1я напряжения, третий и четвертый выходы второго дешифратора подключены ко вторым входам амплитудного и фазового синхронных детекторов.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-09-05—Публикация

1977-03-11—Подача