1

Устройство относится к области автоматики и вычислительной техники.

Известны устройства для приема информации, содержащие триггеры, элементы «И- НЕ, «ИЛИ 1.

Однако такие устройства сложны и имеют низкую надежность.

Наиболее близки.м по технической сущности к изобретению является устройство для приема последовательного кода, содержащее первый и второй элементы «И-НЕ, выход каждого из которых подключен к перво.му входу другого и к соответствующему входу первого разряда регистра сдвига, второй вход второго элемента «И-НЕ подключен к шине тактовых импульсов, соединенной с соответствующим входом каждого разряда регистра сдвига 2.

Однако в таком устройстве, если импульс информации опережает импульс сдвига, то первый же импульс информации до при.хода импульса сдвига записывается в первый разряд и с приходом первого импульса сдвига переписывается во второй. Таким образом, для данного случая следует подавать импульс сдвига на один меньше, чем импульсов информации. Тот же эффект имеет место в случае потенциальной передачи информации.

Это создает определенные трудности при проектировании аппаратуры цифровой обработки информации в быстродействующих системах, где разные длины линий связи между абонентами и аппаратурой синхронизации создает условия разного временного соотношения между импульсами информации и сдвига, тем более, что учет этого временного рассогласования на этапе конструирования очень затруднен. Разные временные соотношения между импульсами информации и сдвига приводят к

тому, что для разлнчны.х условий одной н той же аппарат}ры необходимо разное количество импульсов синхронизации (сдвигов).

Цель изобретения - упрощение устройства и повышение надежности его работы.

Это достигается тем, что в нредлагае.мое устройство введены элементы «И-НЕ, «НЕ, «2И-4И-2ИЛИ-НЕ и /-/(-триггер, разряд регистра сдвига выполнен на /-/(-триггере, причем информационный вход

устройства соединен с первыми входами третьего элемента «И-НЕ, первого элемента «И элемента «2И-4И-2ИЛИ-НЕ, шина тактовых импульсов подключена к С-входу /-Ктриггера, инверсный выход которого соединен

соответственно с вторым входо.м первого и первым входом второго элементов «И элемента «2И-4И-2НЛИ-НЕ, прямой выход /-/(-триггера подключен к второму входу третьего элемента «И-НЕ, выход которого

соединен с S-входом /-/(-триггера первого

разряда регистра, шина установки в ноль нодключена к второму входу второго элемента «И элемента «2Й-4И-2ИЛИ--Н1:;, к / входам /-К-тркггера и /-/С-трнггеров каждого разряда регистра, выходы первого и второго элементов «И-НЕ присоединены соответственно к /(-входу /-/(-триггера и третьему входу второго элемента «И элемента «2И-4И-2ИЛИ-НЕ, выход которого через элемент «НЕ подключен к четвертому входу второго элемента «2И-4И-2ИЛИ-НЕ, выход элемента «2И-4И-2ИЛИ-НЕ соединен с вторым входом первого элемента «И- НЕ, выходы первого и второго элементов «И-НЕ подключены соответственно к / и /(-входам /-/(-триггера первого разряда регистра, прямой и инверсный выходы /-/(триггера каждого разряда регистра соединены соответственно с У и /(-входами /-/(-триггера последующего разряда регистра.

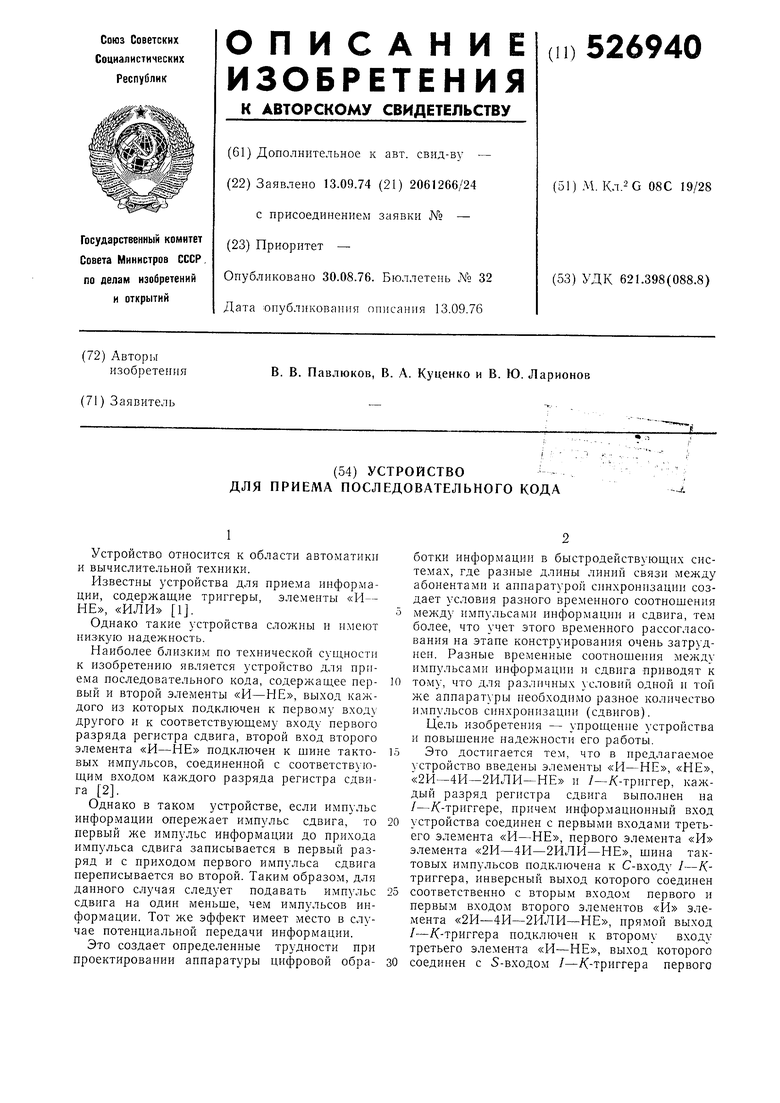

На фиг. 1 показана блок-схема предлагаемого устройства, где 1 - элемент «Pi-НЕ, 2 - элемент «2И-4И-2ИЛИ-НЕ, 3 - элемент «НЕ, 4 - /-/(-триггер, 5 - элемент «И-НЕ, 6 - второй элемент «И-НЕ, 7 - вход устройства, 8- шина установки в нуль, 9 - шина тактовых импульсов, 10 - выход элемента «Н-НЕ 1,11- выход элемента «2И-4И-2ИЛИ-НЕ, 12- прямой выход /-/(-триггера, 13 - инверсный выход /-/(-триггера, 14 - выход элемента 5 «И- НЕ, 15 - выход элемента 6 «И-НЕ, 16 - прямой выход первого разряда /-/(-триггера, 17 - прямой выход второго разряда /-/(триггера.

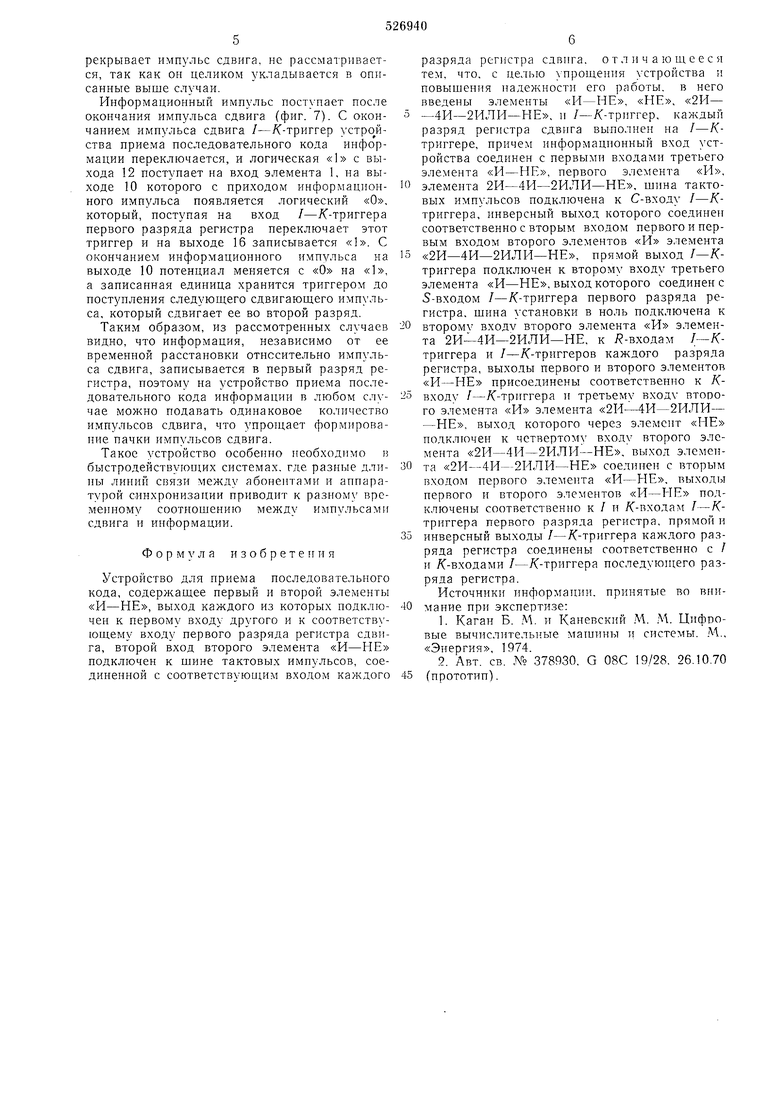

На фиг. 2-7 приведены временные диаграммы работы.

Исходным состоянием устройства принимается нулевое состояние триггеров сдвигаюидего регистра. В этом случае на единичных выходах 12, 16, 17, а на выходе 14 присутствует логический «О (низкий уровень потенциала), а на выходах 10, 11, 13, 15- логическая «1 (высокий уровень потенциала). Информационные импульсы положительной полярности поступают на вход 7 устройства приема последовательного кода информации, а импульс сдвига той же полярности на вход 9.

Рассмотрим несколько случаев приема информации.

Информационный импульс поступает и заканчивается до прихода импульса сдвига (фиг. 2). С входа 7 информация поступает на вход элемента «И элемента «2Й--4И - -2ИЛИ-НЕ, на выходе 11 при этом появляется логический «О, а на выходе 14 - логическая «1. С окончанием информационного импульса такое состояние элемента сохраняется. Оно изменяется только с появлением импульса сдвига. Нричем с его началом на выходе 15 появляется логический «О, на выходе 11 - логическая «, а с окончанием /-/Стриггер первого разряда регистра переключается, записывая на выходе 16 логическую на выходе 12 также появляется «1. Записанная информация с приходом следуюихего импульса сдвига переписывается во второй разряд.

Информационный импульс поступает до начала импульса сдвига, а заканчивается до окончания последнего (фиг. 3).

Ииформациоиный импульс вызывает появление на выходе 11 логического «О, а на выходе 14 - логической «1. С приходом сдвнгового импульса потенциалы этих выходов не меняются, а на выходе 15 появляется логический «О. С окончанием информационного импульса потенциал на выходе 11 меняется с «О на «1, с окончанием сдвигового импульса

на выходах 12, 15 появляется логическая «1, на выходе 14 - логический «О, на выходе 16 - логическая «I.

Импульсы сдвига иерекрывают ииформациоииый импульс по переднему и заднему

фронтам (фиг. 4).

Информационный имиульс поступает на вход 7, на выходе 11 ноявляется логический «О, который подается на вход элемента «И-НЕ 5, вызывая появление на входе 14

логической «1, а на выходе 15 - логического «О. Но окончании имнульса сдвига переключается триггер первого разряда регистра, т. е. появляется на выходе 16 - логическая «1.

Триггер на элементах 5, 6 по окончании импульса сдвига возвраш,ается в первоначальное состояние.

Информационный имнульс С01и1адает с импульсом сдвига (фиг. 5).

С приходом информационного и сдвигового имнульсов на выходе 11 появляется логический «О, который подается на вход элемента «И-НЕ 5, на выходе 14 появляется логическая «1, а на выходе 15 - логический «О.

Вследствие этого по окончании импульса сдвига в иервый разряд регистра записывается поданная информация.

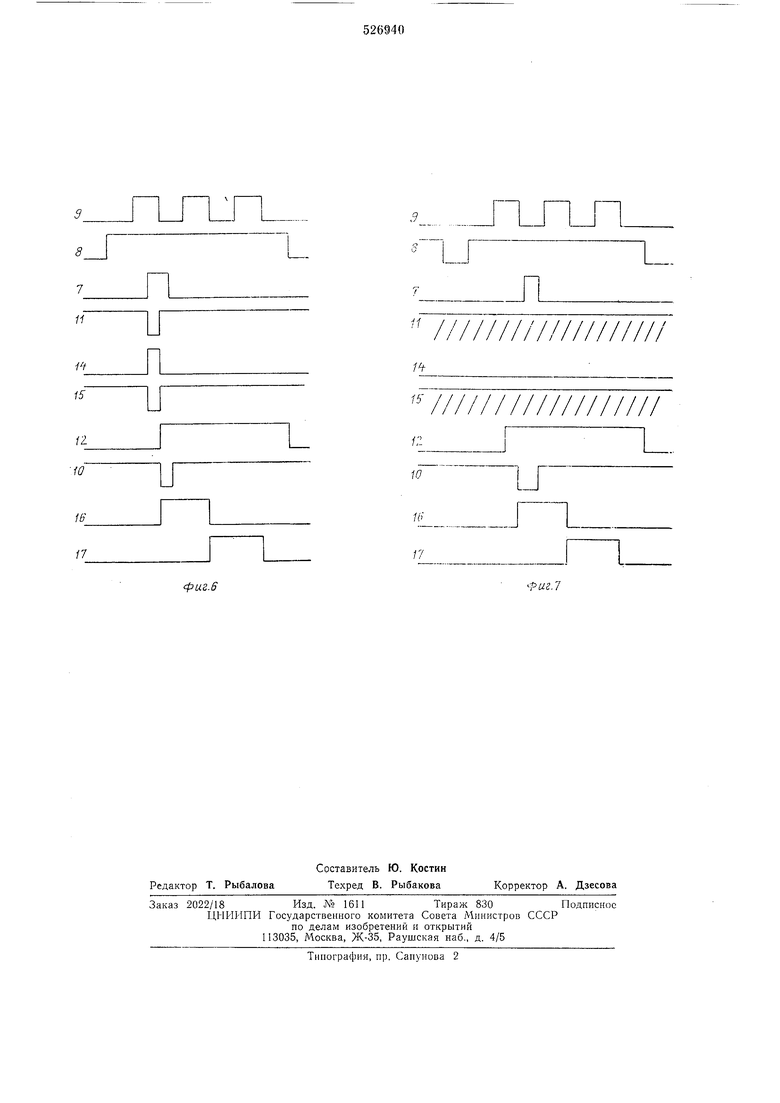

Информационный имнульс поступает после начала импульса сдвига, а заканчивается но

окончании имнульса сдвига (фиг. 6).

На выходе 11 логический «О появляется с приходом информационного импульса и вызывает появление на выходе 14 логической «Ь, а на выходе 15 - «О. По окончании сдвигового импульса переключаются триггер первого разряда регистра (на выходе 16 записывается «1) и /-/(-триггер схемы приема информации. Логический «О с выхода 13 поступает на вход элемента «И элемента «2И-

-4И-2ИЛИ-НЕ и несмотря на то, что информация присутствует на входе 7, на выходе 11 появляется логическая «1. В результате элементы 5, 6 возвращаются в первоначальное состояние. Логическая «1 с выхода 12

поступает на вход элемента «И-НЕ 1. Появившийся на выходе 10 логический «О присутствует до окоичания импульса информации и подтверждает «1, записанную в первом разряде регистра.

Случай, когда информационный импульс перекрывает импульс сдвига, не рассматривается, так как он целиком укладывается в описанные выше случаи.

Информационный имиульс поступает после окончания импульса сдвига (фиг. 7). С окончанием импульса сдвига /-К-триггер устр йства приема последовательного кода информации переключается, и логическая «1 с выхода 12 поступает на вход элемента 1, па выходе 10 которого с приходом информационного импульса появляется логический «О, который, поступая на вход /-/С-триггера первого разряда регистра переключает этот триггер и на выходе 16 записывается «1. С окончанием информационного импульса на выходе 10 потенциал меняется с «О на «1, а заиисанная единица хранится триггером до поступления следующего сдвигающего импульса, который сдвигает ее во второй разряд.

Таким образом, из рассмотренных случаев видно, что информация, независимо от ее временной расстановки относительно импульса сдвига, записывается в первый разряд регистра, поэтому на устройство приема последовательного кода информации в любом случае можно подавать одинаковое количество импульсов сдвига, что упрощает формировапие пачки импульсов сдвига.

Такое устройство особенно необходимо в быстродействуюншх системах, где разные длины линий связи между абонентами и аппаратурой синхронизапии приводит к разному временному соотношению между импульсами сдвига и информации.

Ф о р м } л а изобретения

Устройство для приема последовательного кода, содержащее первый и второй элементы «И-НЕ, выход каждого из которых подключен к первому входу другого и к соответствующему входу первого разряда регистра сдвига, второй вход второго элемента «И-НЕ подключен к шине тактовых импульсов, соединенной с соответствуюишм входом каждого

разряда регистра сдвига, отличающееся тем, что, с целью упрощения устройства и повышения надежности его работы, в него введены элементы «Н-НЕ, «НЕ, «2Н-

-4И-2ИЛИ-НЕ, и /-/(-триггер, каждый разряд регистра сдвига выполнен на /-Ктриггере, причем информационный вход устройства соединен с первыми входами третьего элемента «И-НЕ, первого элемента «И.

элемента 2И-4И-2ИЛИ-НЕ, шина тактовых импульсов подключена к С-входу /-Ктриггера, инверсный выход которого соединен соответственно с вторым входом первого и первым входом второго элементов «И элемента

«2И-4И-2ИЛИ-НЕ, прямой выход I-Kтриггера подключен к второму входу третьего элемента «И-НЕ, выход которого соединен с 5-входом /-/С-триггера первого разряда регистра, шина установки в ноль подключена к

второму входу второго элемента «И элемента 2И-4Н-2ИЛИ-НЕ, к / -входам 1 -Ктриггера и /-/С-триггеров каждого разряда регистра, выходы первого и второго элементов «И-НЕ присоединены соответственно к Квходу /-/С-триггера и третьему входу второго элемента «И элемента «2Н-4И-2ИЛИ- -НЕ, выход которого через элемент «НЕ подключен к четвертому входу второго элемента «2И-4И-2ИЛИ-НЕ, выход элемепта «2И-4И-2ИЛИ-НЕ соединен с вторым входом первого элемента «И-НЕ, выходы первого и второго элементов «РТ-НЕ подключены соответственно к / п /С-входам /-Ктриггера первого разряда регистра, прямой и

инверсный выходы /-К-триггера каждого разряда регистра соединены соответственно с / и К-входами /-К-триггера последующего разряда регистра.

Источники информации, принятые во внимание при экспертизе:

1.Каган Б. М. и Каневский М. М. Цифровые вычислительные машины и системы. .М., «Энергия, 1974.

2.Авт. св. № 378930. G 08С 19/28. 26.10.70 (прототип).

10

11

2

{

Л

17

1

16

if

fuz.i

Риг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема последовательного кода | 1977 |

|

SU705494A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОТКАЗОВ В ШАГОВОМ ЭЛЕКТРОПРИВОДЕ | 1992 |

|

RU2037264C1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| Устройство для приема последовательного кода | 1980 |

|

SU907569A1 |

| Способ измерения частоты вращения и устройство для его осуществления | 1986 |

|

SU1451601A1 |

| Преобразователь кодов | 1980 |

|

SU917340A1 |

| Регистр сдвига | 1979 |

|

SU858108A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

7 //

П

10

/

fUZ.

ftUZ.f

IT

n и

/7

Фиг.6

TL

1 t1Ь

10

1о 17

puг.

Авторы

Даты

1976-08-30—Публикация

1974-09-13—Подача