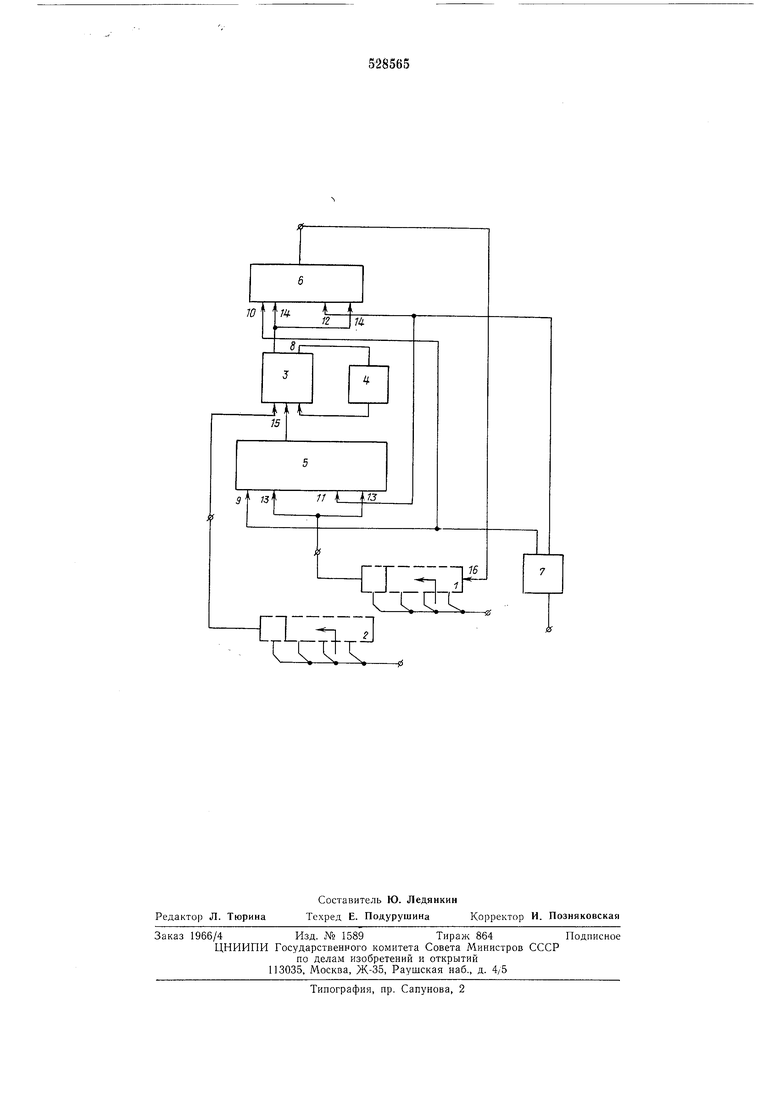

но с выполнением онсрации вычитания чисел, когда в процессе суммирования уменьшаемого и обратного кода вычитаемого требуется вырабатывать сигнал управления и «единицу к младшему разряду, что означает неравноценность операций сложения и вычитания как по времени, так и по управлению. С другой стороны, если вычитаемое поступает из внешпего устройства на второй регистр, то необходимо осуществлять дополнительные операции по ю иерекоммутацни кодов операпдов так, чтобы вычитаемое оказывалось во втором регистре, а уменьшаемое - в первом. Тогда для получения разности двух чисел вычитаемое с помощью входного коммутатора можно обратить и 15 сложить с прямым кодом уменьшаемого. А это снижает коэффициент использования оборудовапия в целом, так как из-за отсутствия коммутатора на втором входе приходится нерационально использовать весь сумматор. Вве- 20 дение дополнительного коммутатора по второму входу приводит к увеличению оборудования. Целью изобретения является повышение коэффициента использования оборудования. 25 В описываемом устройстве это достигается тем, что оно содержит триггер и выходной коммутатор, два управляющих входа которого попарно объединены с двумя соответствующими унравляющими входами входного комму- 30 татора и подключены соответственно к прямому и инверспому выходам триггера, входы которого подключены к входным управляющим шипам устройства, информационный выход сумматора соединен с прямым и инверсным 35 входами выходного коммутатора, выход которого соединен с соответствующим входом первого регистра. На чертеже показана схема описываемого устройства.40 Оно содержит первый 1 и второй 2 регистры для хранения и сдвига кодов операндов, причем разрядные шины первого и второго регистров подключены к первой и второй группам входных шин, сумматор 3 с линией 45 задержки 4 на один такт, входной 5 и выходной 6 коммутаторы, которые могут быть выполнены в виде схем «2И и «2И-НЕ, объедипеппые по выходу схемой «2ИЛИ, триггер 7, выход 8 сумматора 3. Управляющие входы 50 9, 10 и 11, 12 входных и выходных коммутаторов 5 и 6 попарно объединены и соединены с прямым и инверсным выходами триггера 7, а информационные входы 13 и 14 входных и выходных коммутаторов 5 и 6 соединены со- 55 ответственно с выходом первого регистра 1 и информационным выходом сумматора 3. Выход входного коммутатора 5 соединен со вторым входом 15 сумматора 3, а выходного - со входом 16 первого регистра 1, первый вход GO сумматора соединен с выходом второго регистра 2 непосредственно. При работе устройства в режиме сложения два числа, записанные в дополнительном коа,е в первом 1 и втором 2 регистрах, сдвига- G5 ются младшими разрядами вперед. Тогда на входы сумматора 3 числа поступают из первого регистра 1 в коде представления через входной коммутатор, а из второго регистра 2 тоже в коде представления - непосредственно. При этом триггер 7 по управляющим входам 9 и 11 открывает прямые коммутаторы входного и выходного коммутаторов 5 и 6, осуществляя передачу числа В в сумматор, а результата В через ипформационный выход - из сумматора в коде представления чисел в регистрах 1 и 2. Пример. В первом регистре 1 хранится в дополнительном коде слагаемое 0.100, а во втором регистре 2 - в дополнительном коде второе слагаемое С -3/8 1.101. В результате сложения получается число В также в коде представления В ::-: 0.100 с 1.101 В -0.001 -+1/8 При работе устройства в режиме вычитания два числа в дополнительном коде сдвигаются младшими разрядами вперед. На второй вход 15 сумматора 3 поступает уменьшаемое В из первого регистра 1 в инверсном коде через коммутатор 5, а вычитаемое С из регистра 2- непосредственно на первый вход сумматора 3. При этом триггер 7 управляющими входами 10 и 12 открывает инверсные входы входных и выходных коммутаторов 5 и 6 и осуществляет передачу уменьщаемого В в сумматор, а результат В из сумматора в обратном коде (т. е. В и Б соответственно) по отношению к коду представления и результату суммирования. Пример. В регистре 1 хранится в дополнительном коде уменьшаемое .100, а в регистре 2 в дополнительном коде вычитаемое С .101. Вычитание двух чисел, представленных в дополнительном коде, осуществляется путем суммирования уменьшаемого в обратном коде с вычитаемым в прямом коде. Полученный результат, после обращения, дает разность чисел В и С в дополнительном коде, т. е. В В-С. .100 , В 1.011 .101 .101 В 1.000 . Таким образом, описываемое устройство, реализующее новый алгоритм вычитания чисел, представленных в дополнительном :оде, повышает коэффициент использования оборудования, поскольку практически не имеет значения в каком регистре находится уменьшаемое и вычитаемое. Устройство управления в известном аналогичном устройстве 2, построенное на триггерах в виде графа автомата, вершины котоporo однозначно онределяют вид выполняемой операции, должно иметь не менее трех вершин: одну - для выполнения операции сложения двух чисел в коде представления; вторую - для сложения двух чисел, одно из которых (уменьшаемое) в прямом, а другое (вычитаемое) в обратном коде с прибавлением «1 в первом такте сложения младших разрядов числа; третью - для сложения чисел (по операции, определяемой второй вершиной) в течение п-1 такта сложения двух ft-разрядных чисел, но без прибавления «1. В отличие от него в описываемом устройстве достаточно двух состояний, определяемых первой и третьей вершинами. При этом оборудованне устройства управления, без которого работа как известного, так и описываемого устройства невозможна, относится к одному разряду сумматора, и оно значительно превышает расход оборудования на один выходной коммутатор в описываемом устройстве.

Если предлагаемое последовательное устройство имеет связи, описанные выше, граф автомата имеет три состояния, позволяюшие реализовать оба алгоритма вычитания чисел, представленных дополнительным кодом: известный алгоритм, когда складывают уменьшаемое в прямом коде с вычитаемым в обратном коде и прибавляют единицу к младшему разряду числа; предлагаемый алгоритм, когда складывают уменьшаемое в обратном коде с вычитаемым в прямом и обращают полученную сумму; управление входными и выходными коммутаторами разделено, а второй регистр связан с регистром числа ОЗУ, то независимо от того, где находятся и откуда поступают уменьшаемое и вычитаемое, операция вычитания выполняется за один цикл, равный по длительности п тактам для «-разрядных чисел. Если, например, вычитаемое хранится в первом регистре, а уменьшаемое поступает из ОЗУ, тогда отрабатывается известный алгоритм, по которому вычитаемое обрашается входным коммутатором и в первом такте сложения прибавляется «1. Если из вновь полученной разности, поступившей в первый регистр, надо вычесть число, постунаюшее в сумматор из ОЗУ через второй регистр, тогда известное устройство не работает. Однако, если автомат устройства управления последовательно возбуждает два состояния, реализуюшие работу устройства, т. е. обращение кода уменьшаемого (на выходе первого регистра), сложение с прямым кодом вычитаемого (из второго регистра) и обращением кода полученного результата, то устройство выполняет нредписанную операцию. В противном случае потребовалась бы дополнительпая перекоммутация кодов операндов: уменьшаемое из первого регистра переслать во второй регистр (т. е. нужен коммутатор), вычитаемое из ОЗУ записать в первый регистр (нужен коммутатор или необходимо установить входной коммутатор между вторым регистром и первым входом сумматора), однако при этом автомат устройства управления также должен был бы иметь дополнительное состояние, определяющее операцию вычитания известным способом, когда уменьшаемое может находиться в первом или во втором регистрах.

Технико-экономический эффект заключается в повышении коэффициента использования оборудования, вследствие его универсальности, так как, независимо от того, где хранится вычитаемое и уменьшаемое, за один цикл (с числом микротактов, равным значносги кодов операндов) можно выполнять операцию вычитания, реализуя устройством управления тот или иной алгорнтм вычитания. Описываемое устройство содержит входной коммутатор по второму входу сумматора, который связан с выходом регнстра результата сумматора (как в известных 1, 2 устройствах), а взамен первого входного коммутатора 1, расширяемого по числу подключаемых к нему регистров, введен выходной коммутатор, который соединен только с выходом результата сумматора.

Все это не только повышает коэффициент использоваппя оборудования, но даже сокращает его.

Формула изобретения

Последовательное арифметическое устройство, содержащее первый регистр, разрядные входы которого подключены к первой группе входных шин, а выход соединен с информационными входами входного коммутатора, второй регистр, входы которого подключены ко второй группе входных шин, а выход соединен с первым входом сумматора, второй вход которого подключен к выходу входного коммутатора, а третий - к выходу элемента задержки, вход которого соединен с выходом переноса сумматора, отличающееся тем, что, с целью повышения соэффициента использования оборудования, оно содерл ит триггер и выходной коммутатор, два управляющих входа которого попарно объединены с двумя соответствующими управляющими входами в.ходного коммутатора и подключены соответсчвенно к прямому и инверсному выходам триггера, входы которого подключены ко входным управляющим шинам устройства, информационный выход сумматора соединен с прямым и инверсным входами выходного коммутатора, выход которого соединен с соответствующим входом первого регистра.

Источники информации, принятые во внимание при экспертизе:

1.Рабинович 3. Л. Элементарные операции в вычислительных машинах. К-, Техника, 1966, с. 258, рис. 64,а.

2.Карцев М. А. Арифметика цифровых машин. М., Наука, 1969, с. 294.

W

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Устройство для умножения чиселВ дОпОлНиТЕльНыХ КОдАХ | 1978 |

|

SU822181A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

Авторы

Даты

1976-09-15—Публикация

1974-07-16—Подача