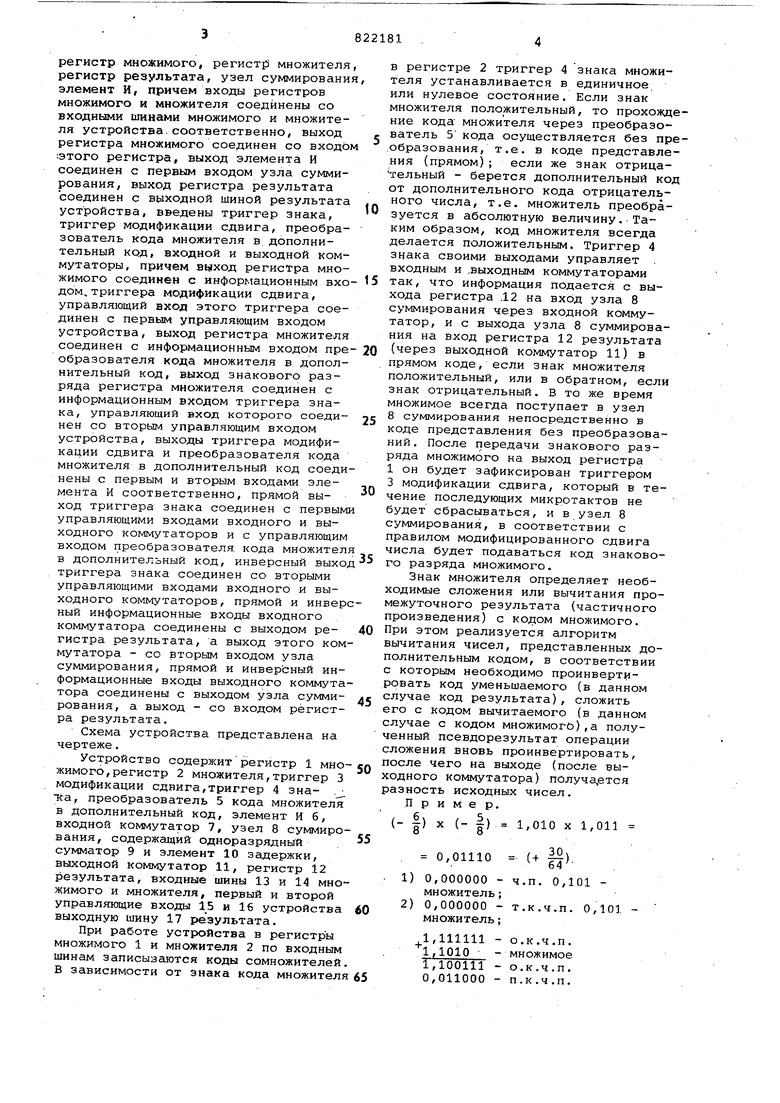

(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В ДОПОЛНИТЕЛЬНЫХ КОДАХ регистр множимого, регистр) множителя, регистр результата, узел суммирования элемент И, причем входы регистров множимого и множителя соединены со входными шинами множимого и множителя устройства.соответственно, выход регистра множимого соединен со входом :этого регистра, выход элемента И соединен с первым входом узла суммирования, выход регистра результата соединен с выходной шиной результата устройства, введены триггер знака, триггер модификации сдвига, преобразователь кода множителя в дополнительный ко-д, входной и выходной коммутаторы, причем регистра множимого соединен с информационным вхо дом, триггера модификации сдвига, управляющий вход этого триггера соединен с первым управляющим входом устройства, выход регистра множителя соединен с информационным входом пре образователя кода множителя в дополнительный код, выход знакового разряда регистра множителя соединен с информационным входом триггера знака, управляющий вход которого соединен со BToptJM управляющим входом устройства, выходы триггера модификации сдвига и преобразователя кода множителя в дополнительный код соеди нены с первым и вторым входами элемента И соответственно, прямой выход триггера знака соединен с первым управляющими входами входного и выходного коммутаторов и с управляющим входом преобразователя, кода множител в дополнительный код, инверсный выхо триггера знака соединен со вторыми управляющими входами входного и выходного коммутаторов, прямой и инвер ный информационные входы входного коммутатора соединены с выходом регистра результата, а выход этого ком мутатора - со вторым входом узла суммирования, прямой и инверсный информационные входы выходного коммута тора соединены с выходом узла суммирования, а выход - со входом регистра результата. Схема устройства представлена на чертеже. Устройство содержит регистр 1 мно жимо го, регистр 2 множителя,триггер 3 модификации сдвига,триггер 4 зна- . ка, преобразователь 5 кода множител в дополнительный код, элемент И 6, входной коммутатор 7, узел 8 суммиро вания, содержащий одноразрядный сумматор 9 и элемент 10 задержки, выходной коммутатор 11, регистр 12 результата, входные шины 13 и 14 мно я имого и множителя, первый и второй управлягющие входы 15 и 16 устройства выходную шину 17 результата. При работе устройства в регистры множимого 1 и множителя 2 по входным шинам записываются коды сомножителей В зависимости от знака кода множител регистре 2 триггер 4 знака множиеля устанавливается в единичное ли нулевое состояние. Если знак ножителя положительный, то прохождение кода множителя через преобразоатель 5 кода осуществляется без пребразования, т.е. в коде представления (прямом); если же знак отрицательный - берется дополнительный код от дополнительного кода отрицательного числа, т.е. множитель преобразуется в абсолютную величину. Таким образом, код множителя всегда делается положительным. Триггер 4 знака своими выходами управляет входным и .выходным коммутаторами так, что информация подается с выхода регистра ,12 на вход узла 8 суммирования через входной коммутатор, и с выхода узла 8 суммирования на вход регистра 12 результата (через выходной коммутатор 11) в прямом коде, если знак множителя положительный, или в обратном, если знак отрицательный. В то же время множимое всегда поступает в узел 8 суммирования непосредственно в коде представления без преобразований. После передачи знакового разряда множимого на выход регистра 1 он будет зафиксирован триггером 3 модификации сдвига, который в течение последующих микротактов не будет сбрасываться, и в узел 8 суммирования, в соответствии с правилом модифицированного сдвига числа будет подаваться код знакового разряда множимого. Знак множителя определяет необходимые сложения или вычитания промежуточного результата (частичного произведения) с кодом множимого. При этом реализуется алгоритм вычитания чисел, представленных дополнительным кодом, в соответствии с которым необходимо проинвертировать код уменьшаемого (в данном случае код результата), сложить его с кодом вычитаемого (в данном случае с кодом множимого),а полученный псевдорезультат операции сложения вновь проинвертировать, после чего на выходе (после выходного коммутатора) получается разность исходных чисел. Пример. (-|) X 1,010 X 1,011 . 0,01110 (+ ||). 1)0,000000 - ч.п. 0,101 множитель;2)0,000000 - т.к.ч.п. 0,101 множитель;Д,111111 - о.к.ч.п. 1,1010 - множимое 1,100111 - о.к.ч.п. 0,011000 - п.к.ч.п.

3)0,011000 п.к.ч.п. 0,101 множитель

4)0,011000 - т.к.ч.п. 0,101 множитель

1,100111 - о.к.п.ч. 1,111010 - множимое 1,100001 - псевдорезультат.

1,011110 - результат (+ ||)

где ч.п. - частичное произведение; O.K. - обратный код; п.к. - прямой код.

В приведенном примере реализуется умножение, начиная со старших разрядов множителя со сдвигом множимого вправо и с неподвижным частичным произведением. Возможна реалзация умножения, начиная с млгщших разрядов множителя.

Таким образом, устройство позволяет выполнять операцию умножения двоичных чисел в дополнительных кодах без коррекции с интерпретацией знаковых разрядов как числовых.

Введение двух дополнительных триггеров, преобразователя кода множителя и двух коммутаторов позволяет BjDtBoe сократить число циклов суммирования, при выполнении операций умножения чисел в дополнительных кодах без коррекции, так как отпадает необходимость расширения разрядной сетки сомножителей.

Это приводит к увеличению быстродействия предлагаемого устройства в 1,7-1,8 раз по сравнению с известным. Предлагаемое устройство позволяет совместить устройство для сложения (вычитания) чисел в дополнительных кодах с устройствам умножения, (деления) аналогичных чисел.

Формула изобретения

Устройство для умножения чисел в дополнительных кодах, содержащее регистр множимого, регистр множителя/

регистр результата, узел суммирования, элемент И, причем входы регистров множимого и множителя соединени со входными шинами множимого и множителя устройства соответственно, выход регистра множимого соединен со входом этого регистра, выход элемента И соединен с первым входом узла суммирования, выход регистра разуль- : тата соединен с выходной шиной результата устройства, отличающеoеся тем, что, с целью увеличения быстродействия, в устройство введены триггер знака, триггер модификации сдвига, преобразователь кода множителя в дополнительный код, входной и

5 выходной коммутаторы, причем выход регистра множимого соединен с информационным входом триггера модификации сдвига, управляющий вход этого триггера соединен с первым управ0 . ляющим входом устройства, выход регистра множителя соединен с информационным входом преобразователя кода множителя в дополнительный код, выход знакового разряда регистра множителя соединен с информационным

5 входом триггера знака, управляющий вход которого соединен со вторым управляющим входом устройства, выходы триггера модификации сдвига и преобразователя кода множителя в допол0нительный- код соединены с первым и вторымвходами элемента И соответственно, прямой выход триггера знака соединен с первыми управляющими входами входного и выходного ком5мутатора и с управляющим входом Преобразователя кода множителя в дополнительный код, инверсный выхо)ц триггера знака соединен со вторыми управляющими входами входного и

0 выходного коммутаторов, прямой и инверсный информационные входы входного коммутатора соединены с выходом регистра результата, а выход этого коммутатора - со вторым входом узла суммирования, прямой и инверс5ный информационные входы выходного коммутатора -соединены с выходом узла суммирования, а выход - со входом регистра результата .

1Z

ф ф ж ж ж

/1 Л Т ф

n

J.

1Ш1

/J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1978 |

|

SU813418A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU932489A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

Авторы

Даты

1981-04-15—Публикация

1978-08-21—Подача