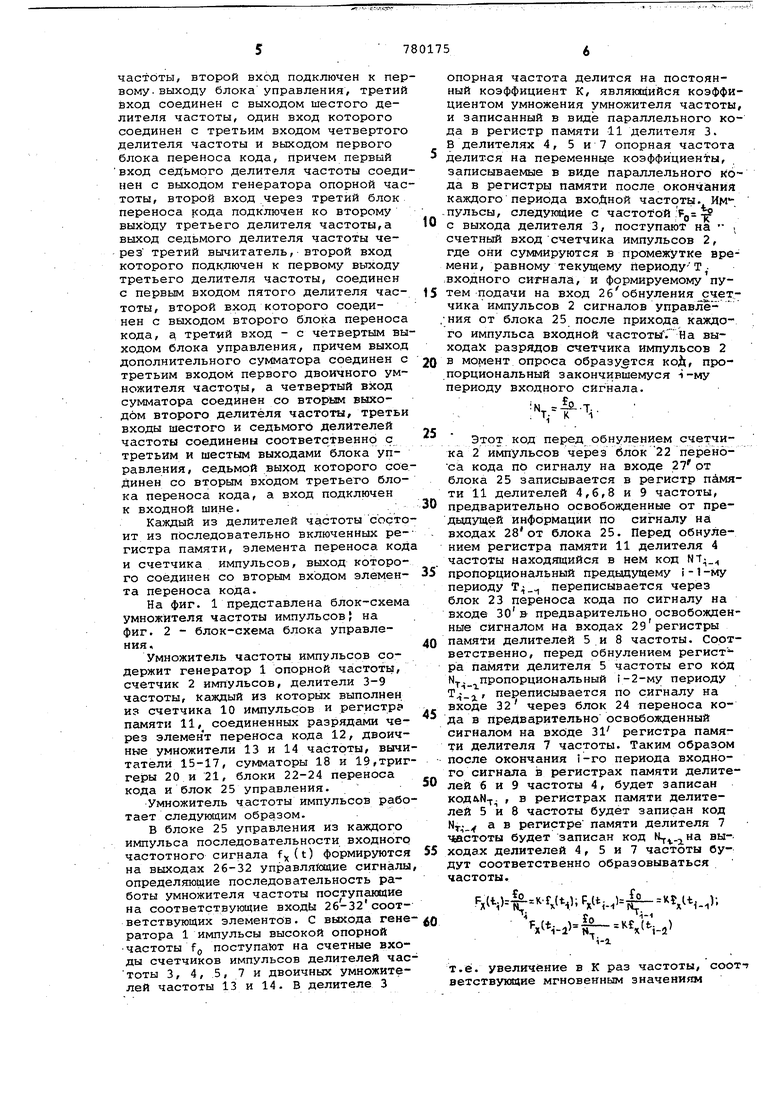

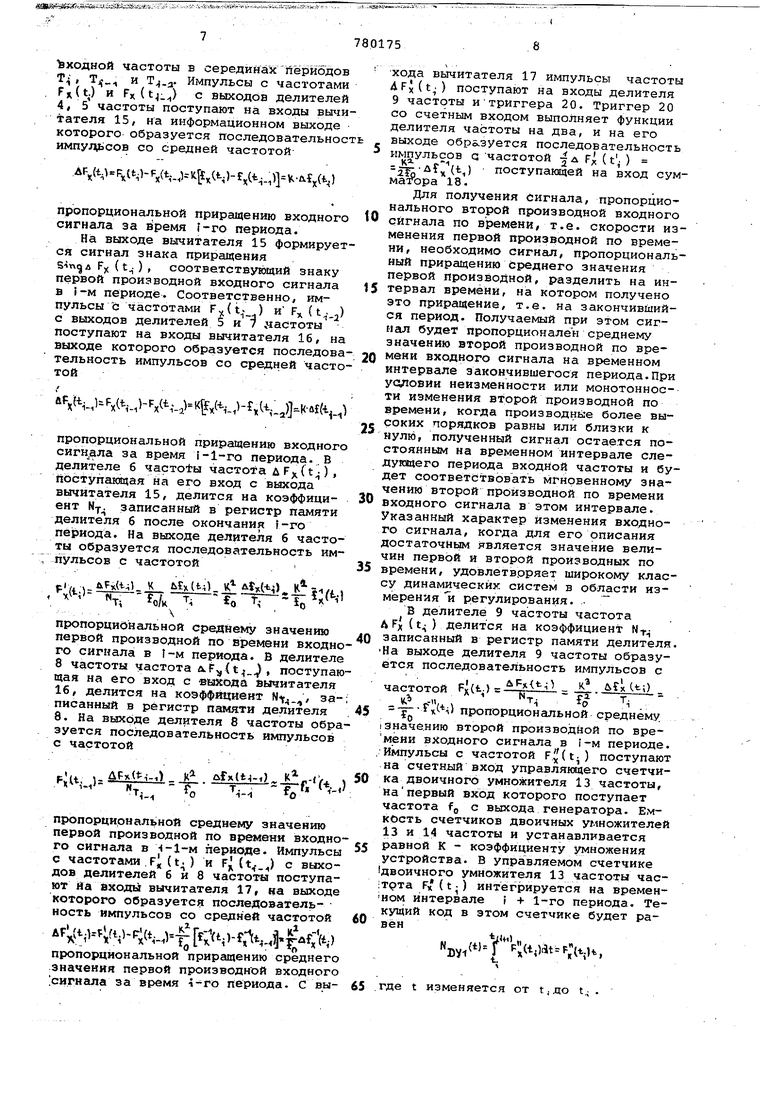

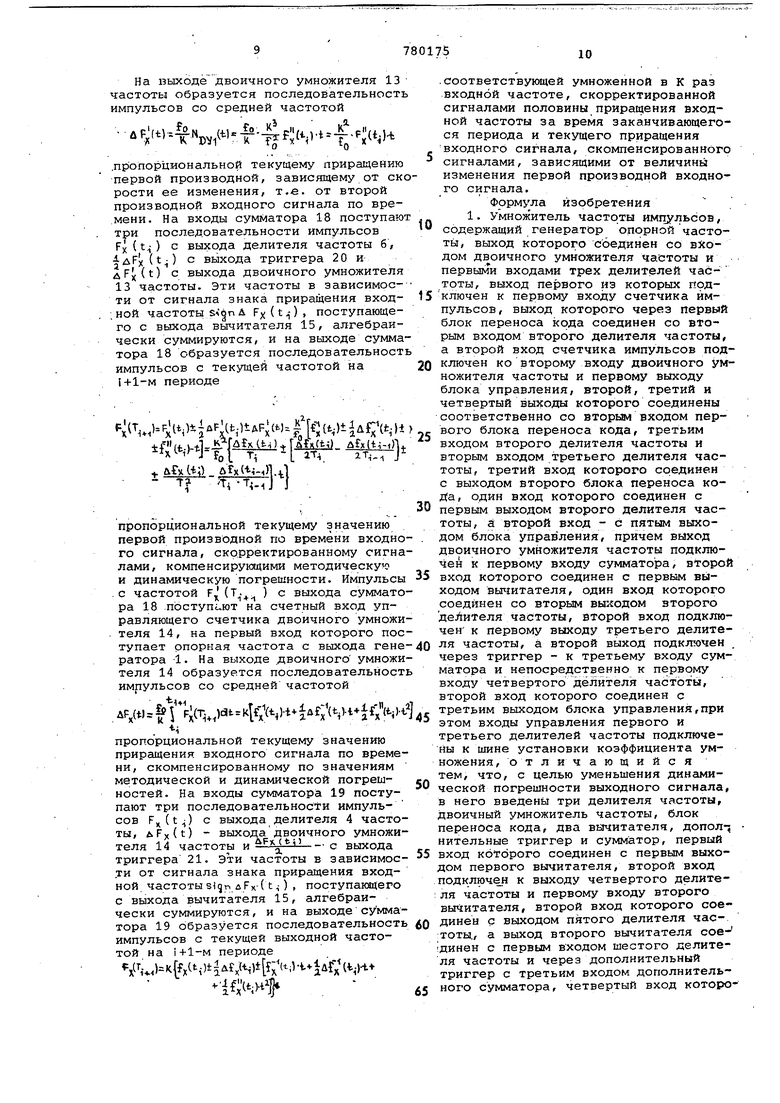

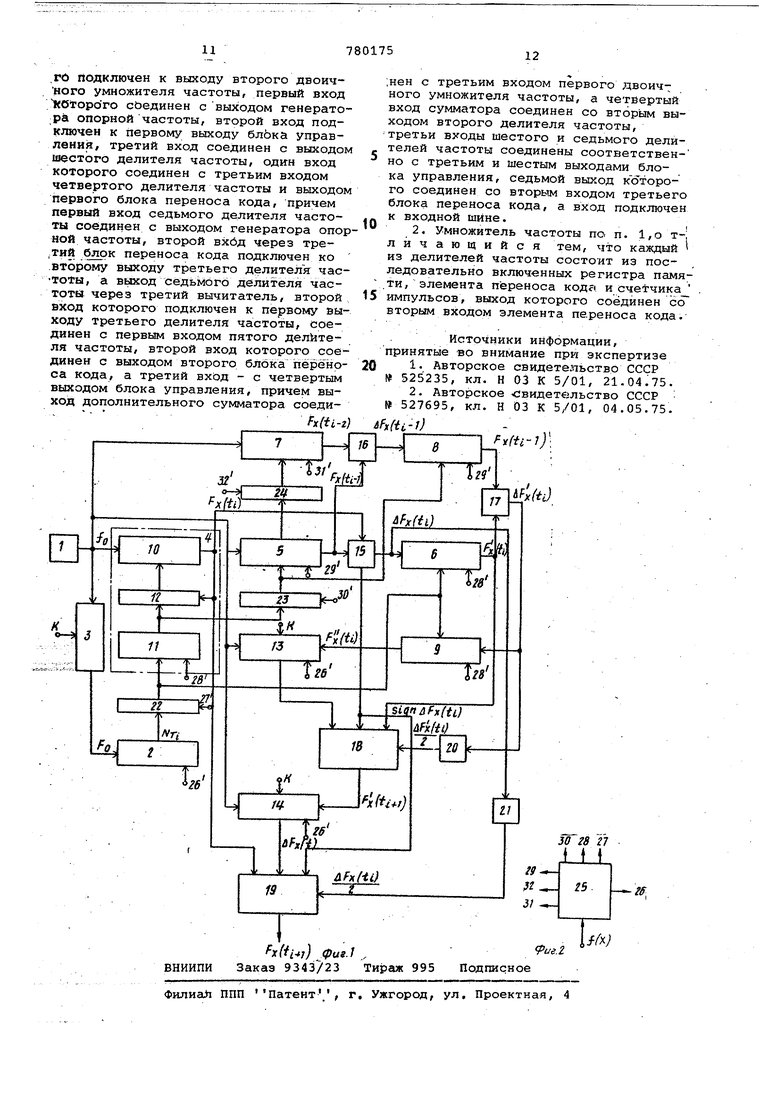

-текущее время в интер вале t. и t -начало и конец i + 1го периода Т... Сигнал, пропорциональный первой производной по времени входного сигнала, получается путем деления приращения сигнала, пропорционального входной частоте, на временной интервал, равный закончившемуся периоду .входной частоты, на котором получено приращение. Приращение же получается вычитанием двух частот, сформированных путем обратно пропорционально го преобразования двух соседних периодов входной частоты с коэффициентом прйпордиональности, РАВНЫМ К - коэффициенту умножения устройства. Благодаря введению корректирующих сигналов по половине приращения мгновенного значения входной частоты за время закончившегося периода и те кущего приращения входной частоты, пропорционального первой производной по времени входного сигнала, в известном устройстве удается уменьшить .динамическую погрешность преобразова ния, связанную с изменением входного сигнала. Получаемый при этом сигнал ,.;(v(.,M.t;v,.« о 1 . 1 О И 0 лишь приближенно пройорцйонаЛен первой производной по времёйй входного сигнала, так как интервал Т-, на котором получено приращение, может . быть достаточно большим, особенно в низкочастотном диапазоне, и йа нем первая производная может менять свое значение. Поэтому выражение (2) пред ставляет собой величину, пропорциональнук) среднему значению первой производной по времени в I-м периоде входного сигнала, которое необ54одимо по времени отнести к середине временного интервала Т. К моменту окон чания t-rp периода в случае изменени пйрвОй производной образуется методи ческая шшбка, равная половине прира щения первой производной за время 1-го периода. Кроме того, в прототипе на следующем временном интервале, равном. + 1-ому периоду Т .получен ный в конце i-го периода сигнал,пропорциональный первой производной, остается неизменным, тогда как производная в действительности меняется Таким образом. Известное устройство позволяет получить хорошие метрОлогичесКИё Х&рактернстики только для входных сигналов, изменяющихся линейно или монотонно во времени,что ограничивает область его применения. Для быстроменяющихся динамических процессов величина первой производной будет меняться в промежутке между двумя преобразователями (внутри периода входной частоты) , поэтому выходной сигнал в известном устройстве при этом будет иметь динамическую погрешность, зависящую от величины второй производной входного сигнала. Целью изобретения является уменьшение динамической погрешности выходного сигнала. . - . Поставленная цель достигается тем, что в умножитель частоты импульсов, содержащий генератор опорной частоты, выход которого соединен со входом . двоичного умножителя частоты и первыми входамитрех делителей частоты, выход первого Из которых подключен к первому входу счетчика импульсов, выход которого через первый блок переноса кода соединен со вторым входом второго делителя частоты, а второй вход счетчика импульсов подключен ко второму входу двоичного умножителя частоты и первому выходу блока управления, второй, третий и четвертый выходы которого соединены соответственно со вторым входом первого блока переноса кода, третьим входом второго делителя частоты и вторым входом третьего делителя частоты, третий вход которого соединен с выходом второго блока переноса кода, один вход которого соединен с первым выходом второго делителя частоты, а второй вход - с пятым выходом блока управления, причем выход двоичного умножителя частоты подключен к первому входу сумматора, второй вход которого соединен с первым выходом вычитателя, один вход которого соединен со вторым выходом второго делителя частоты, второй вход подключен к первому выходу третьего делителя частоты, а второй выход подключен через триггер к третьему входу сумматора и непосредственно к первому входу четвертого делителя частоты, второй вход которого соединен с третьим выходом блока управления, при этом входы управления первого и третьего делите- . лей частоты подключены к шине установки коэффициента умножения,введены три делителя частоты, двоичный умножитель частоты, блок переноса кода, два вычита теля, дополнительные триг- . гер и сумматор, первый вХод которого соединен с первым выходом первого вычитателя, второй вход подключен к выходу четвертого делителя частоты и первому входу второго вычитателя, второй вход которого соединен с выходом пятого делителя частоты, а выход второго вычитателя соединен с первым входом шестого делителя частоты и через дополнительный триггер - с третьим входом дополнительного сумматора, четвертый вход которого подключен к выходу второго двоичного умножителя частоты, первый вход которого соединен с выходом генератора опорной частоты, второй вход подключен к пер вому, выходу блока управления, третий вход соединен с выходом шестого делителя частоты, один вход которого соединен с третьим входом четвертого делителя частоты и выходом первого блока переноса кода. Причем первый вход седьмого делителя частоты соеди нен с выходом генератора опорной час тоты, второй вход через третий блок переноса кода подключен ко второму выхЬду третьего делителя частоты,а выход седьмого делителя частоты через третий вычитатель, второй вход которого подключен к первому выходу третьего делителя частоты, соединен с первым входом пятого делителя частоты, второй вход которого соединен с выходом второго блока переноса кода, а третий вход - с четвертым вы ходом блока управления, причем выход дополнительного сумматора соединен с третьим входом первого двоичного умножителя часто ы, а четвертый вход сумматора соединен со вторьвл выходом второго делителя частоты, третьи входы шестого и седьмого делителей частоты соединены соответственно с третьим и шестым выходами блока управления, седьмой выход которого сое динен со вторым входом третьего блока переноса кода, а вход подключен к входной шине. Каждый из делителей частоты состо ит из последовательно включенных регистра памяти, элемента переноса код и счетчика импульсов, выход которого соединен со вторым входом элемента переноса кода. На фиг. 1 представлена блок-схема умножителя частоты импульсов на фиг. 2 - блок-схема блока управления. Умножитель частоты импульсов содержит генератор 1 опорной частоты, счетчик 2 импульсов, делители 3-9 частоты, каждый из которых выполнен из счетчика 10 импульсов и регистра памяти 11, соединенных разрядами через элемент переноса кода 12, двоичные умножители 13 и 14 частоты, вычи татели 15-17, сумматоры 18 и 19,триг геры 20 и 21, блоки 22-24 переноса кода и блок 25 управления. Умножитель частоты импульсов рабо тает следующим образом. В блоке 25 управления из каждого импульса последовательности входного частотного сигнала fx(t) формируются на выходах 26-32 управляющие сигналы определяющие последовательность работы умножителя частоты поступающие на соответствующие входУ 26-32 соответствующих элементов. С выхода гене ратора 1 импульсы высокой опорной частоты fj, поступают на счетные входы счетчиков импульсов делителей час тоты 3, 4, 5, 7 и двоичных умножителей частоты 13 и 14. В делителе 3 опорная частота делится на постоянный коэффициент К, являющийся коэффициентом умножения умножителя частоты, и записанный в виде параллельного кода в регистр памяти 11 делителя 3. В делителях 4, 5 и 7 опорная частота делится на переменные коэффициен гы, записываемые в виде параллельного кода в регистры памяти после окончания каждого периода вхоДной частоты. Им-пульсы, следуквдие с частотой :FQ с выхода делителя 3, поступают на - . счетный вход счетчика импульсов 2, где они суммируются в промежутке времени, равному текущему периоду , входного сигнала, и формируемому путем подачи на вход 2бобнуления счетчика импульсов 2 сигналов управле-ния от блока 25 после прихода каждого импульса входной частоты . На выходах разрядов счетчика импульсов 2 в момент опроса образуется коД, пропорциональный закончившемуся i-му периоду входного сигнала. ;ы -IS-.T . К Ч Этот код перед обнулением счетчика 2 импульсов через блок 22 переноса кода по сигналу на входе 27 от блока 25 записывается в регистр пАмяти 11 делителей 4,6,8 и 9 частоты, предварительно освобожденные от предыдущей информации по сигналу на входах блока 25. Перед обнулением регистра памяти 11 делителя 4 частоты находящийся в нем код NT пропорциональный предыдущему i-1-му периоду Т Переписывается через блок 23 переноса кода по сигналу на входе ЗОв предварительно освобожденные сигналом на входах 29регистры памяти делителей 5.и 8 частоты. Соответственно, перед обнулением регист ра памяти делителя 5 частоты его код N, пропорциональный i-2-му периоду тД, переписывается по сигналу на входе 32 через блок 24 переноса кода в предварительно освобожденный сигналом на входе 31 регистра памяти делителя 7 частоты. Таким образом после окончания i-ro периода входного сигнала в регистрах памяти делителей б и 9 частоты 4, будет записан кодлЫ тц S регистрах памяти делителей 5 и 8 частоты будет записан код NT, регистре памяти делителя 7 частоты будет записан код Н.на вы-, ходах делителей 4, 5 и 7 частоты будут соответственно образовываться частоты. F,(t.).- -K-yt 5;F,tt,-.,)Kyt.); ( i-г т.е. увеличение в К раз частоты, соотт ветствуквдие мгновенным значениям Ъходной частоты в серединах периодов 4 4-1 и Т.д. Импульсы с частотами Fx(t) и Fx(t4) с выходов делителей 4, З частоты поступают на входы вычитателя 15/ на информационном выходе которого образуется последовательност импудьсов со средней частотой ,--;--4«x bfxt -i-i)( пропорциональной приращению входного сигнала за время i-ro периода. На выходе вычитателя 15 формируется сигнал знака приращения Sing л Fy (t.) соответствукядий знаку первой производной входного сигнала в i-M периоде. Соответственно, импульсы с ча1стотами Fv(t ) и F (.j) с выходов делителей 5 и 7 частоты поступают на входы вычитателя 16, на выходе которого образуется последовательность импульсов со средней частотой.l-Fx(-,)-Fx(--abK x(4,bfx -J-Nf(i.,V пропорциональной приращению входного сигнала за время i-1-го периода. В делителе б частоты частота дF(t), поступаквдая на его вход с выхода вычитателя 15, делится на коэффициент N-J-. записанный в регистр памяти делите шя б после окончания -го периода. На выходе делителя 6 частоты образуется последовательность импульсов с частотой . t/, л uFx(i. Miil-Ji: :± zfci}..l Лч(--м: -у -т: д т, -, пропорциональной среднему значению первой производной по времени входно го сигнала в 1-м периода. В делителе 8 частоты частота л. F(t| , поступаю щая на его вход с выхода йычитателя 16, делится на коэффициент NY, записанный в регистр памяти дел ителя 8. На выходе делителя 8 частоты обра зуется последовательность импульсов с частотой .;,,,.М -.Ц.,Г пропорциональной среднему значению первой производной по времени входно го сигнала в периоде. Импульсы с частотами . Fi (t ) и F (t.) с выходов делителей б и 8 частоты поступают иа входы вычитателя 17, на выходе которого образуется последовательность импульсов со средней частотой ,.)-f;ft.)-F;(t,.,).)-f,1t,.,|.f,) пропорциональной приращению среднего значения первой производной входного ;сигнала за время периода. С вы8хода вычитателя 17 импульсы частоты AFx() поступают на входы делителя 9 частоты итриггера 20. Триггер 20 со счетным входом выполняет функции делителя частоты на два, и на его выходе образуется последовательность импульсов а частотой F(t) (tj поступающей на вход сумматора 18. Для получения сигнала, пропорционального второй производной входного сигнала по времени, т.е. скорости изменения первой производной по времени, необходимо сигнал, пропорциональный приращению Среднего значения первой производной, разделить на интервал времени, на котором получено это приращение, т.е. на закончившийся период. Получаемый при этом сигнал будет пропорционален среднему значению второй производной по времени входного сигнала на временном интервале закончившегося периода.При уоповии неизменности или монотонности изменения второй производной по времени, когда производные более высоких порядков равны или близки к нулю, полученный сигнал остается постоянньм на временном интервале следующего периода входной частоты и будет соответствовать мгновенному значению второй производной по времени входного сигнала в этом интервале. Указанный характер изменения входного Сигнала, когда для его описания достаточньш является значение величин первой и второй производных по времени, удовлетворяет широкому классу динамических систем в области измерения и регулирования. В делителе 9 частоты частота А Fj (t ) делится на коэффициент N-r записанный в регистр памяти делителя. На выходе делителя 9 частоты образуется последовательность импульсов с частотой FX) . V f,. , т ip i пропорциональной Среднему (Значению второй производйой по времени входного сигнала в i-м периоде. .Импульсы с частотой (t.) поступают на счетный вход управляющего счетчика двоичного умножителя 13 частоты, напервый вход которого поступает частота fg с выхода генератора. Емкость счетчиков двоичных умножителей 13 и 14 частоты и устанавливается равной К - коэффициенту умножения устройства. В управляемом счетчике двоичного умножителя 13 частоты час:т9та FX (t ) интегрируется на временном интервале i + 1-го периода. Текущий код в этом счетчике будет равенВУ1 ГИ(, .где t изменяется от t j до t . На выходе двоичного умножителя 13 чгастоты образуется последовательность импульсов со средней частотой -fefy H - x t H .пропорциональной текущему приращению первой производной, зависящему от ско рости ее изменения, т.е. от второй производной входного сигнала по времени. На входы сумматора 18 поступают три последовательности импульсов pj(t) с выхода делителя частоты 6, AFx{t4) с выхода триггера 20 и uFJ((t) с выхода двоичного умножителя 13 частоты. Эти частоты в зависимоети от сигнала знака приращения вход, ной частоты Д Fx() поступающего с выхода вычитателя 15, алгебраически суммируются, и на выходе сумматора 18 образуется последовательность импульсов с текущей частотой на i+1-м периоде (,)tiaf;;V.)i if;4.,K..|{Mxi.M. M.Jli.)}, 1-MLM-uMLbll-U - т Тг-vJ 1 пропорциональной текущему значению первой производной по времени входно го сигнала, скорректированному сигна лами, компенсирукщими методическую и динамическую погрешности. Импульсы .с частотой F.(Т. ) с выхода сумматора 18 -поступг ют на счетный вход управляющего счетчика двоичного умножи. теля 14, на первый вход которого поступает опорная частота с выхода генератора -1. На выходе .двоичного умножителя 14 образуется последовательность импульсов со средней частотой Ayt) (T.,),)-t iuf;{t.,.).i5 . -ti пропорциональной текущему значению приращения входного сигнала по времени, скомпенсированному по значениям методической и динамической погрешностей. На входы сумматора 19 поступают три последовательности импульсов F(t.i) с выхода делителя 4 частоты, &F,((t) - выхода двоичного умножителя 14 частоты и bsJJEJJс выхода триггера 21. Эти частоты в зависимоети от сигнала знака приращения входной частоты , л Fx-(t.;), поступакяцего с выхода вычитателя 15, алгебраически суммируются, и на выходе сумматора 19 образуется последовательность импульсов с текущей выходной частотой на i+1-м периоде V,4.) . .соответствующей умноженной в К раз входной частоте, скорректированной сигналами половины приращения входной частоты за время заканчивающегося периода и текущего приращения входного сигнала, скомпенсированного сигналами, зависящими от величины изменения первой производной входного сигнала. Формула изобретения 1. Умножитель частоты импульсов, содержащий генератор опорной частоты, выход которого соединен со входом двоичного умножителя частоты и первыми входами трех делителей частрты, выход первого из которых подключен к первому входу счетчика импульсов, выход которого через первый блок переноса кода соединен со вторым входом второго делителя частоты, а второй вход счетчика импульсов подключен ко второму входу двоичного умножителя частоты и первому выходу блока управления, второй, третий и четвертый выходы которого соединены соответственно со вторым входом первого блока переноса кода, третьим входом второго делителя частоты и вторым входом третьего делителя частоты, третий вход которого соединен с выходом второго блока переноса кода, один вход которого соединен с первым выходом второго делителя частоты, а второй вход - с пятым ВЕЛХОдом блока управления, причем выход двоичного умножителя частоты подключен к первому входу сумматора, второй вход которого соединен с первым выходом выситателя, один вход которого соединен со вторым выходом второго деЛителя частоты, второй вход подключен к первому выходу третьего делителя частоты, а второй выход подключен через триггер - к третьему входу сумматора и непосредственно к первому входу четвертого делителя частоты, второй вход которого соединен с третьим выходом блока управления,при этом входы управления первого и третьего делителей частоты подключены к шине установки коэффициента умножения, отличающийся тем, что, с целью уменьшения динамической погрешности выходного сигнала, в него введены три делителя частоты, двоичный умножитель частоты, блок переноса кода, два вычитателя, дополнительные триггер и сумматор, первый вход которого соединен с первым выходом первого вычитателя, второй вход подключен к выходу четвертого делителя частоты и первому входу второго вычитателя, второй вход которого соединен с выходом пятого делителя частоты., а выход второго вычитателя соединен с первым входом шестого делителя частоты и через дополнительный триггер с третьим входом дополнительного сумматора, четвертый вход которо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифференцирования частотно-импульсных сигналов | 1978 |

|

SU742967A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1980 |

|

SU920722A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Число-импульсный функциональный преобразователь | 1982 |

|

SU1043645A1 |

| Число-импульсное устройство для вычисления обратного тригонометрического тангенса | 1983 |

|

SU1092498A1 |

| Система для передачи телеизмерительной информации | 1982 |

|

SU1113832A1 |

| УМНОЖИТЕЛЬ ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1972 |

|

SU355624A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Цифровой нуль-орган | 1978 |

|

SU798812A2 |

Авторы

Даты

1980-11-15—Публикация

1978-03-07—Подача