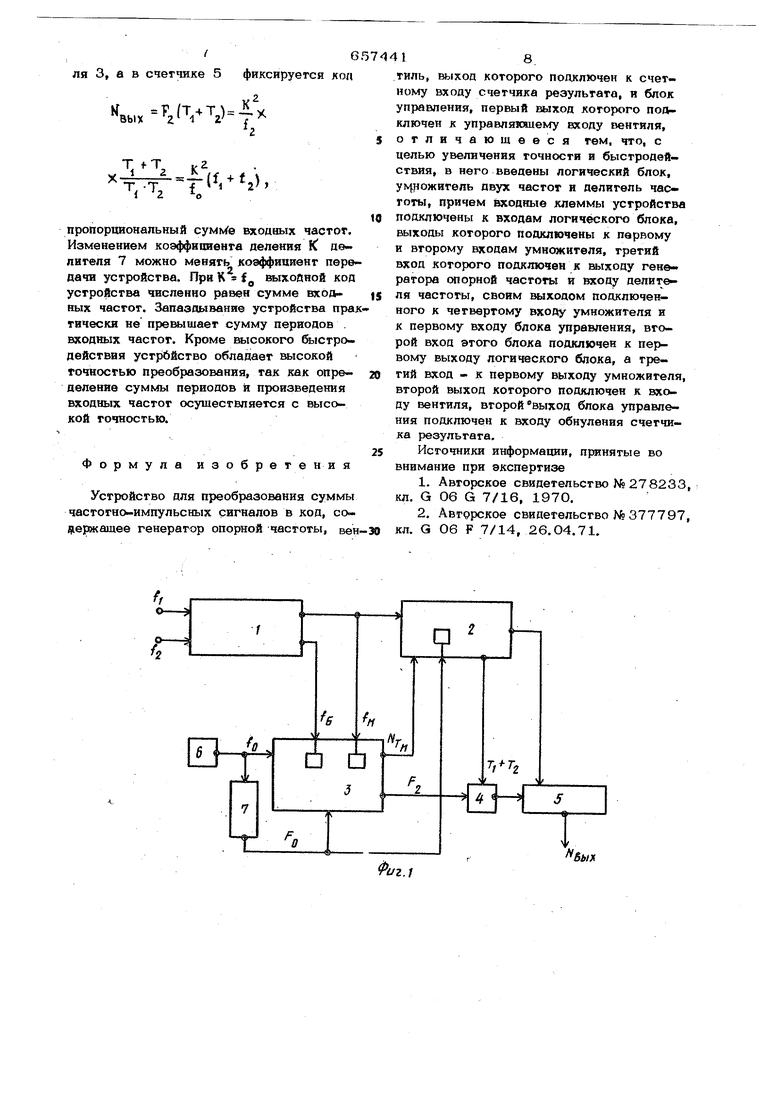

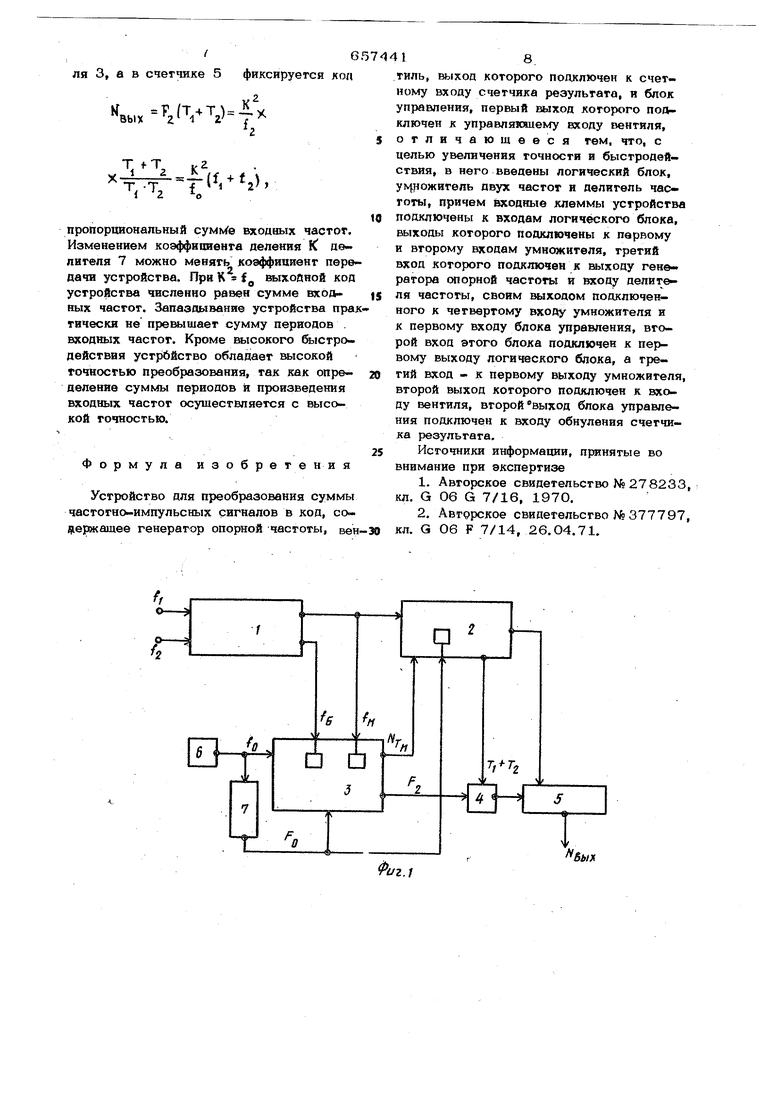

ключен к управляющему входу венгиля, введены логический блок, умножитель дву часгот и делитель частоты, причем входные клеммы устройства подключены к входам логического блока, выходы которого подключены к первому и второму входам умножителя, третий вход которого подключен к выходу генератора опорной частоты и входу делителя частоты, своим выходом подключенного к четвертому вхо ду умножителя двух частот и к первому входу блока управления, второй вход этого блока подключен к первому выходу логического блока, а третий вход - к первому выходу умножителя двух частот, второй выход которого подключен к входу вентиля, второй иыход блока управления подключен к входу обнуления счетчика результата. Цель изобретения увеличение точнос ти и быстродействия устройства. На фиг. 1 приведена блок-схема пред лагаемого устройства; на фиг. 2 - то же принципиальная схема. Устройство (фиг. 1/ содержит логический блок 1, блок 2 управления умножитель 3 двух частот, вентиль 4, счетчик результата 5, генератор 6 опорной частоты и делитель 7 частоты. Логический блок 1 (фиг. 2/ состоит из блока 8 вычитания, четырех вентилей 9-12, двух элементов ИЛИ 13, 14| блок 2 управления выполнен из элемента задержки 15, двух триггеров 16, 17, вычитающего счетчика 18, двух вентилей 19, 2О, блока управления счетчиком 21, группы вентилей 22 переноса кода и элемента ИЛИ 23; умножитель 3 двух часгот содержит два управляемых делителя 24, 25 частоты, каждый из которых выполнен из вычитающего счетчика 26 и регистра 27 памяти, и группы вентилей 28 переноса кода, два суммируюших счет чика 29, ЗО, две группы .вентилей 31, 32 и два блока 33, 34 управления. .Устройство работает следующим образом. Две импульсные последовательности с частотами ,f и f. поступают на входы логического блока 1, который, независимо от соотношения входных частот все да формирует на одном из своих выходов большую частоту а на другом - меньщую частоту, что позволяет безошибочн работать блоку управления независимо от соотношения частот-и фаз входных сигна лов. шим образом. Импульсы входных частот f. и (поступают на входы блока 8 вычитания, выполненного, например, по схеме из двух триггеров и двух вентилей. Наличие сигнала на одном из выходов схемы указывает на превышение по величине частоты, поступающей на соответствующий вход. Если f. f,, то выходом с блока 8 открываются вентили 9 и 12, при этом кмпульсь частоты .f.j через вентиль 9 и элемент ИЛИ 13 поступают на выход большая частота, а импульсы частоты f- через вентиль 12 и элемент ИЛИ 14 поступают на выход меньшая частота . Если , , то блок 8 вычитания открывает вентили 10 и 11, при этом импульсы частоты -f2 через вентиль 11 и элемент ИЛИ 13 поступают на выход большая частота , а импульсы частоты { через вентиль 10 и элемент ИЛИ 14 поступают на меньшая частота . Таким образом, независимо от того, какая из входных частот больше, на выходе элемента 13 всегда находится боль шая частота , а на выходе элемента 14 - меньшая частота . Так как блок 2 использует информацию от умножителя 3 двух частот, то рассмотрим сначала работу умножителя. С выхода генератора 6 импульсы высокой опорно.й частоты поступают на счетные входы неуправляемого делителя 7 с постоянным коэффициентом деления К и управляемого делителя 24 с переменным коэффициентом деления К , установленным в регистре 27 памяти. На выходе делителя 7 образуются импульсы, следующие с частотой . Импульсы с этой частотой поступают на счетные входы суммирующих счетчи- ков 29, 30 и вы читающегосчетчика 18 через вентиль 2О. В счетчиках 29, 30 эти импульсы суммируются во временных промежутках, равных соответственно периодам большей и меньшей частоты и формируемых сигналами управления с блоков 33 и з4 управления, поступающих на входы обнуления счетчиков 29, ЗО. В счетчике 29 в конце счетного интервала образуется код, пропорционяп периоду Т /К

а в счетчике 30 образуется код, пропорциональный периоду Т

.о

. ы -1т V к Б

Эти коды сигналами управления переносятся через группы вентилей 31 и 32 в регистры 27 управляем{ 1х делителей 24, 25 и являются их коэффициентами деления. Каждым импульсом с выхода вычитающего счетчика 26, поступающим через блок 33, код из регистра памяти 27 через открь1тую группу вентилей 28 записывается в вычитающий счетчик 26, После списания записанного в счетчик числа на его выходе появляется импульс, повторяющий процесс деления.

Последовательностью работы узлов умножителя управляют блоки 33, 34, работающие аналогично. На входы блока 33 поступают импульсы большая частота с логического блока 1. В промежутках между импульсами большая частота импульсы с выхода делителя 24 открывают группу венги:лей 28 и записывают в счетчик 26 код Kt хранящийся в регистре 27, При: поступлении очередного импульса больщая частота сигналом с блока 33 сначала обнуляется регистр 27, а затем че рез группу вентилей 31 переписывается новое значение кода ;N из счетчика 29, который после этого обнуляется. Если импульсы, поступающие на вход блока управления, совпадают во времени, то блок управления сдвигает процесс записи в регистр памяти нового кода во избежание ложной записи в счетчик 26 нулевого кода. Аналогичноработает и блок управления 34, формирующий сигналы управления из импульсов меньщая частота и импульсов с выхода управляемого делителя 25,

На выходе управляемого делителя 24 образуется частота

- t.-K

1

м

Импульсы этой частоты поступают на счетный вход второго управляемого целителя 25, на выходе которого образуется частота

м

Таким образом, выходная частота умножителя 3 пропорциональна произведе- нию входных частот. Такое построение

умножителя позволяет получать выходную частоту за один период меньшей из входных частот. Кроме того, применение промежуточной высокой частоты f позволя5 ет получить результат с высокой точностью и в широком диапазоне изменить входные частоты. Выходная частота умножителя не имеет флуктуаиий мгновенных значений. Все это увеличивает быстро0 действие, точность устройства и расширяет диапазон кзменения входных частог, Помимо этого, использование такого умножителя упрощает блок суммирования периодов, так как часть необходимой для

5 его работы информации образуется в умножителе.

Рассмотрим работу блока 2.

Первый импульс меньшая частота, 0. поступает на единичный вход триггера 17, открывающий вентиль 4. Триггер 16, установленный сигналом Пуск или налом окончания такта намерения через элемент ИЛИ 23 внулевое состояние, не . пропускает первый импульс меньшая частота через закрытый вентиль 19 на запускающий вход блока 21. Первый импульс меньщая частота, пройдя через элемент задержки 15, устанавливаег триггер. 16

в единичное состояние. Вентиль 19

0

открывается и второй импульс меньшая частота проходит через него и запускает блок 21, который последовательно закрывает вентиль 20, обнуляет счетчик 18, - открывает группу вентилей 22 переноса кода, переписывая через них значение ко да Kij пропорциойальное периодуболыией: частбты, из регистра 27 умножителя и, наконец, открывает вентиль 2О, чйрез который на счетный вычитаюншй вход счетчика начинают йоступать импульсы с выхода неуправляемого делителя 7 с частотой Гр , После постутагения - N импуль сов через время Т, равное периоду большей частоты, на выходе счетчика 18

5 появляется импульс, переводящий триггер 17 в нулевое состояние. Этим же импульсом, поступающим на блок 21,закрывается вентиль 2О и обнуляется счетчик

18 через элемент ИЛИ 23 триггер 16 устанавливается в нулевое состояние и обнуляется счетчик 5 результата. Блок 2 подготовлен к новому такту измерения, который начинается с приходом очередного импульса меньшей частоты. Время, на которое открывается вентиль 4, ра&но сумме периодов входных частот, 3а «это время в счетчик 5 проходити, импульсов частоты F с выхода умножнте

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| Устройство для суммирования частотно-импульсных сигналов | 1977 |

|

SU708361A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| Устройство для определения первой разности частотно-импульсного сигнала | 1982 |

|

SU1043675A1 |

| Многоканальный микропрограммный умножитель частоты | 1983 |

|

SU1144107A1 |

| Цифровой умножитель частоты следования периодических импульсов | 1987 |

|

SU1554124A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| Устройство для измерения и регулирования соотношения скоростей | 1985 |

|

SU1364993A1 |

| Устройство цифрового задания частоты следования импульсов | 1976 |

|

SU641455A1 |

Авторы

Даты

1979-04-15—Публикация

1976-08-02—Подача