(54) АНАЛОГОВОЕ ЗАПОМНИАЮШЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1978 |

|

SU769637A1 |

| Компенсатор дрейфа нуля интегратора | 1976 |

|

SU634301A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU729640A1 |

| УСТРОЙСТВО ДЛЯ СЖАТИЯ ИНФОРМАЦИИ | 1967 |

|

SU222908A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1401602A1 |

| Аналоговое запоминающее устройство | 1975 |

|

SU746738A1 |

| БЛОК ПОСТОЯННОГО ЗАПАЗДЫВАНИЯ | 1971 |

|

SU321820A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1136218A1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

1

Изобретенне относится к автоматике и вычислительной технике и может быть применено в аналоговых вычислительных машинах в качестве устройства долговременного хранения исходных данных и результатов моделированияг а также в следящих системах и задающих устройствах регуляторов и блоках импульсного интегрирования.

Известно аналоговое запоминающее устройство, содержащее интегратор, переключатель, устанавливающий режим работы, и блок коррекции, компенсирующий дрейф выходного сигнала интегратора в режиме запоминания / ij. Недостатками этого устройства являются сложность выполнения схемы блока коррекции, а также высокие требовагния, иредъяатяемые к стабильности частоты синхронизатора блока коррекции.

Наиболее близким к изобретению является анатоговое запоминающее устройство, содержащее переключатель и интегратор, в цепь обратной связи которого включен щиротно-импульсный модулятор, выходы которого подключены ко входам генератора илпульсов и yarta формирования импульсов

опроса соответственно, узел зшравления, выход которого соединен с одним из контакто переключателя, другой контакт переключателя подключен ко входу устройства, выход которого соединен со входом широтно нмпульсного модулятора и выходом интегратора, вход которого подсоединен к подвижному контакту переключателя, и триггер ( 2,

Это устройство не обеспечивает достаточно высокой точности и надежности из-за большого числа узлов в цепи обратной связи, которые имеют собственные дестабилизирующие факторы (временные и температурные), ограничивающие достижение высоких метрологическ11х. характеристик запоминающего устройства (времени запоминания и точности).

Целью nv3o6peTeHHH является повышение точности устройства.

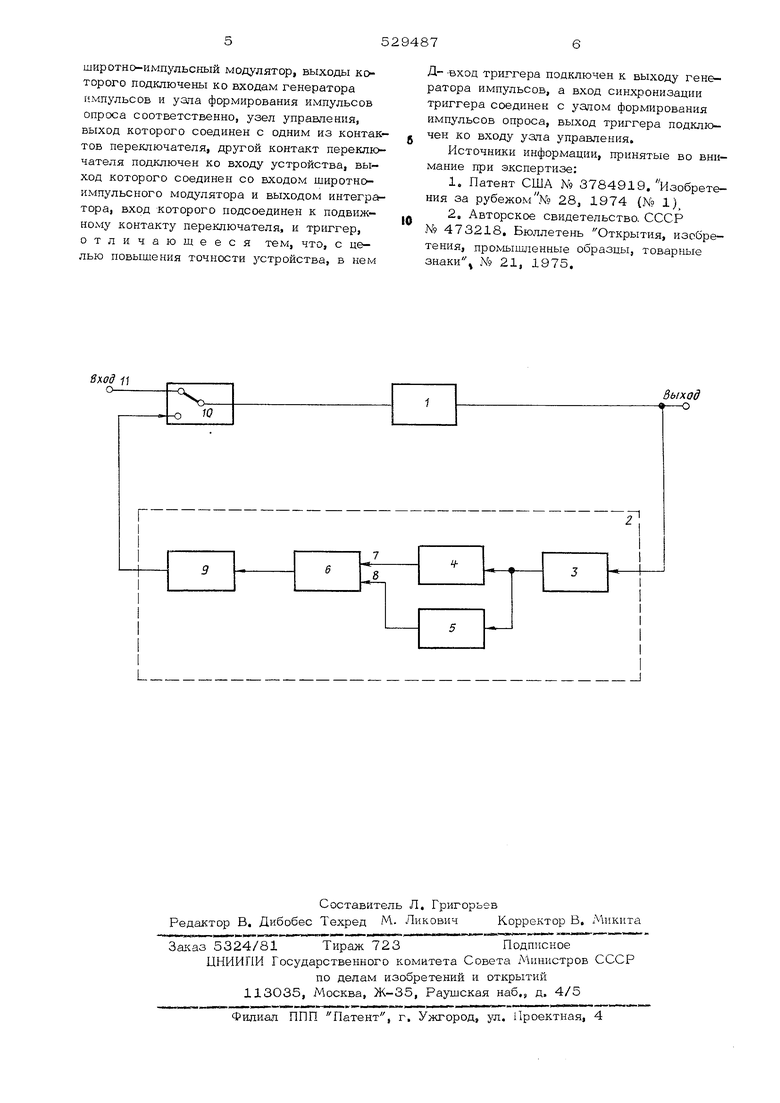

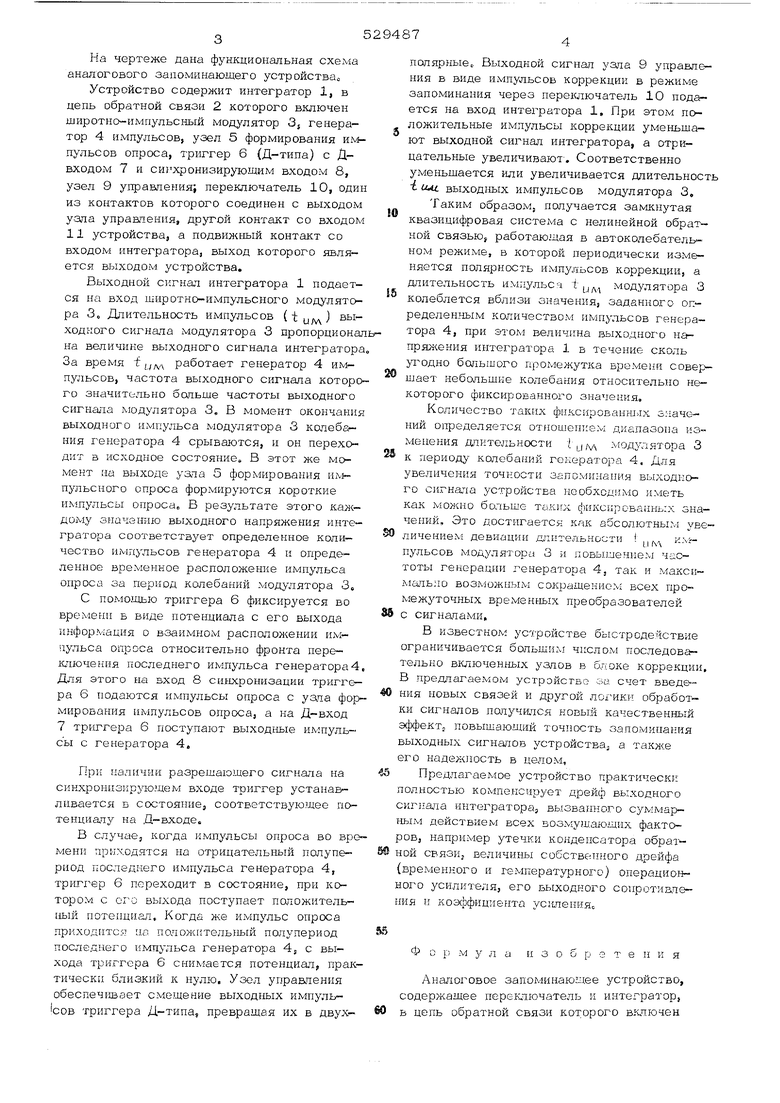

Для этого в предлагаемом устройстве Д-вход триггера подключен к выход} генератора импульсов, вход синхронизации трш гера соединен с ззлом формирования и пульсов опроса; вь1ход триггера подключен ко входу узла упрааления. На чертеже дана функциональная схема анапогового запоминающего устройствао Устройство содержит интегратор 1, в цепь обратной связи 2 которого включен широтно-импульсный модулятор 3j генератор 4 импульсов, узел 5 формирования импульсов опроса, триггер 6 (Д-типа) с Двходом 7 и синхронизирующим входом 8, узел 9 управления; переключатель 10, один из контактов которого соединен с выходом УЗла управления, другой контакт со входом 11 устройства, а подвижный контакт со входом интегратора, выход которого является выходом устройства. Выходной скгнач интегратора 1 подается на вход широтно-импульсного модулятора 3, Длительность импульсов (t u;v ходного сигната модулятора 3 пропорциона на величине выходного сигнала интегратора За время работает генератор 4 импульсов, частота выходного сигнала которо го значительно больше частоты выходного сигнала модулятора 3. В момент окончани выходного импульса модулятора 3 колебания генератора 4 срываются, и он переходит в исходное состояние. В этот же момент -ш выходе уата 5 формирования импульсного опроса формируются короткие импульсы опроса. В результате этого каждому значению выходного напряжения интегратора соответствует определенное количество импульсов генератора 4 и определенное временное расположение импульса опроса за период колебаний модулятора 3, С помощью триггера 6 фиксируется во времени в виде потенциала с его выхода информация о взаимном расположении импульса опроса относительно фронта переключения последнего импульса генератора 4 Для этого на вход 8 синхронизации триггера 6 подаются импульсы опроса с узла фор мирования импульсов опроса, а на Д-вход 7 триггера 6 поступают выход 1ые и.мпульсы с генератора 4. При наличии разрешающего сигнала на синхронизирующем входе триггер устанавливается Б состояние, соответствующее потенциапу на Д-входе« В случае, когда импульсы опроса во вр мени приходятся на отрицательнь й полупериод последнего импульса генератора 4, триггер 6 переходит в состояние, при котором с его выхода поступает положительHbui потенциал. Когда же импульс опроса приходится не положггтельный полупериод последнего импульса генератора 4, с выхода триггера 6 снимается потенциал, прак тически близкий к нулю. Узел управления обеспеч1-тает смещение выход Е-1ых импульICOB триггера Д-типа, превращая их в двухполярные Выходной сигнал узла 9 управления в виде импульсов коррекции в режиме запоминания через переключатель 10 пода-ется на вход интегратора 1, При этом положительные импульсы коррекции уменьшают выходной сигнал интегратора, а отрицательные увеличивают. Соответственно уменьшается или увеличивается длительность i iUi выходных импульсов модулятора 3. Таким образом, получается замкнутая квазицифровая система с нелинейной обрат ной связью, работающая в автоколебательном режиме, в которой периодически изменяется полярность импульсов коррекции, а длительность импульса t д,, модулятора 3 колеблется вблизи значения, заданного определенным количеством имнульсов генератора 4, при этом величина выходного напряи ения интегратора 1 в течение сколь угодно большого промежутка времени соверщает небольшие колебания относительно некоторого фиксированного значения. Количество таких фиксированных значений определяется отношегшем диапазона изменения длительности i модулятора 3 к периоду колебаний генератора 4. Для увеличения точности запоминания выходного сигнала устройства необходимо иметь как можно больше фиксированных значений. Это достигается как абсолютным увеличением девиации длительности i ил;- пульсов модулятора 3 и повышением частоты генерации генератора 4, так и максимально возможным сокращением всех про.межуточных временных преобразователей с сигналами, В известном устройстве быстродействие ограничивается большим числом последовательно включенных узлов в блоке коррекции, В предлагаемом устройстве за счет введения новых связей и другой логики обработки сигналов нолучился новый качественный эффект,, повышающий точность запоминания выходных сигналов устройства, а также его надежность в целом. Предлагаемое устройство практически полностью компенсирует дрейф выходного игьапа интегратора, вызванного суммарным действием всех возмущающих фактоов, например утечки конденсатора обратой СВЯЗИ; величины собстветпюго дрейфа (временного и температурного) операционого усилителя, его выходного соиротиапе- ИЯ и коэффициента усиления т е н и я м у л а Аналоговое запоминающее устройство, содержащее нереключатель и интегратор, в цепь обратной связи которого включен

широтно-импульсный модулятор, выходы которого подключены ко входам генератора импульсов и узла формирования импульсов опроса соответственно, узел управления, выход которого соединен с одним из контактов переключателя, другой контакт переключателя подключен ко входу устройства, выход которого соединен со входом широтноимпульсного модулятора и выходом интегратора, вход которого подсоединен к подвижному контакту переключателя, и триггер, отличающееся тем, что, с целью повышения точности устройства, в нем

Д- -вход триггера подключен к выходу генератора импульсов, а вход синхронизации триггера соединен с узлом формирования импульсов опроса, выход триггера подключен ко входу узла управления.

Источники информации, принятые во внимание при экспертизе:

N9 473218. Бюллетень Открытия, изобретения, промышленные образцы, товарные знаки № 21, 1975.

Авторы

Даты

1976-09-25—Публикация

1974-09-09—Подача