t

Изобретение относится к области ав тематики и вычислительной техники.

Известен блок коррекции аналогового запоминающего устройства, содержащий широтно-импульсный модулятор (ШИМ), узел запуска, узел сброса, генератор высокой частоты (ГВЧ), узел формирования импульсов опроса, триггеры, схемы совпадения и узел управления jjT .

Точность работы этого устройства ограничена, так как при большом числе устойчивых состояний системы даже незначительные изменения коэ(})фициента передачи ШИМ и частоты следования импульсов ГВЧ из-за воздействия помех и изменения питающих напряжений приводят к тому, что при напряжении на входе ШИМ, Соответствующем четному числу импульсов ГВЧ, фактическое число этих импульсов оказывается нечетным. При этом блок коррекции формирует напряже- ния с полярностью, противоположной по отношению к требуемой, вследствие чего

система переходит в соседнюю точку устойчивого равновесия. При многократном воздействии помех системы, последовательно переходя из одного устойчивого состояния в другое, теряет запомненную информацию.

Наиболее близким по технической сущности к предложенному является компенсатор дрейфу нуля интегратора, содержащий компаратор, первый вход которого подключен к выходу интегратора, а выход связан со входом интегрирующей RG-цепи и через первый ключ со входом интегратора 2|.

Недостаток этого устройства состоит в том, что полная компенсация дрейфа неосуществима из-за наличия сопротивления утечки интегрирующего конденсатора, входящего в схему корректирующего звена.

Целью изобретения является повышение точности компенсации.

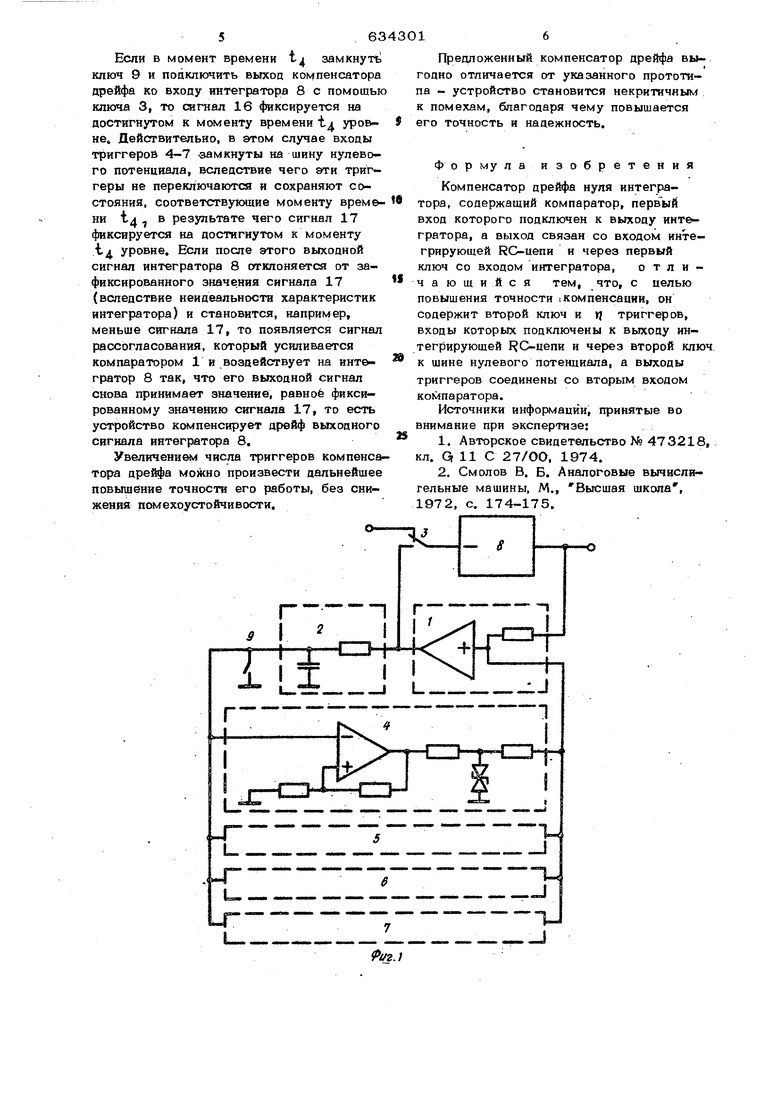

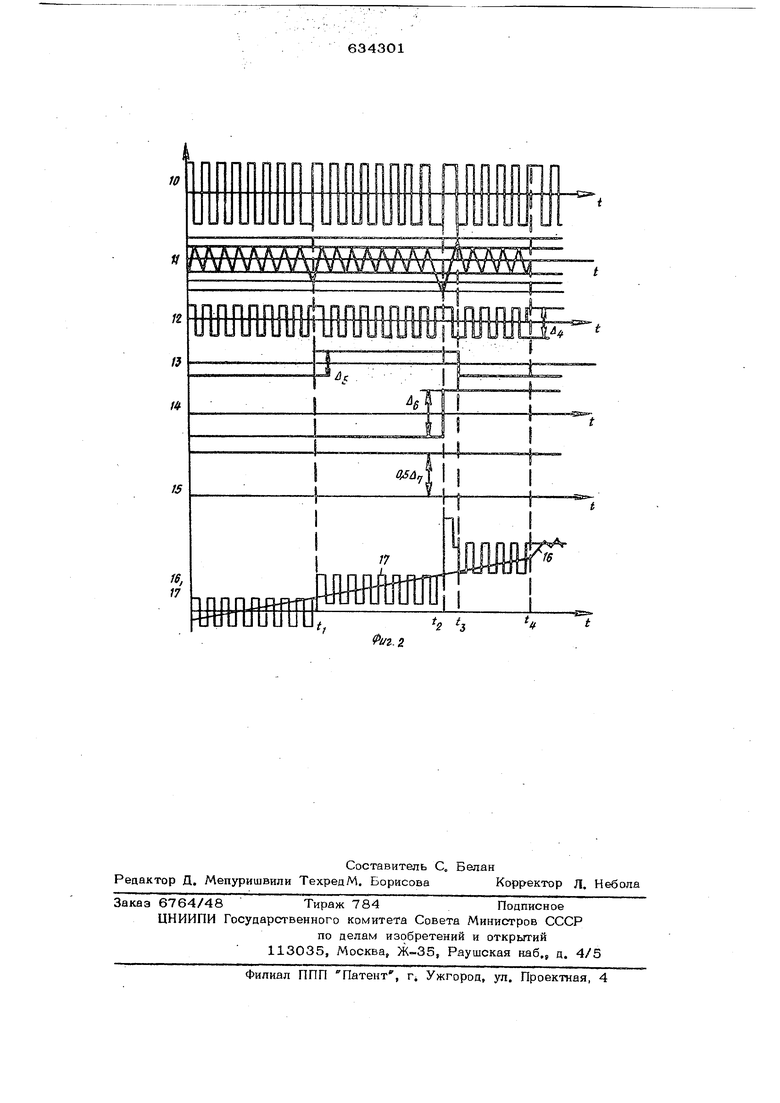

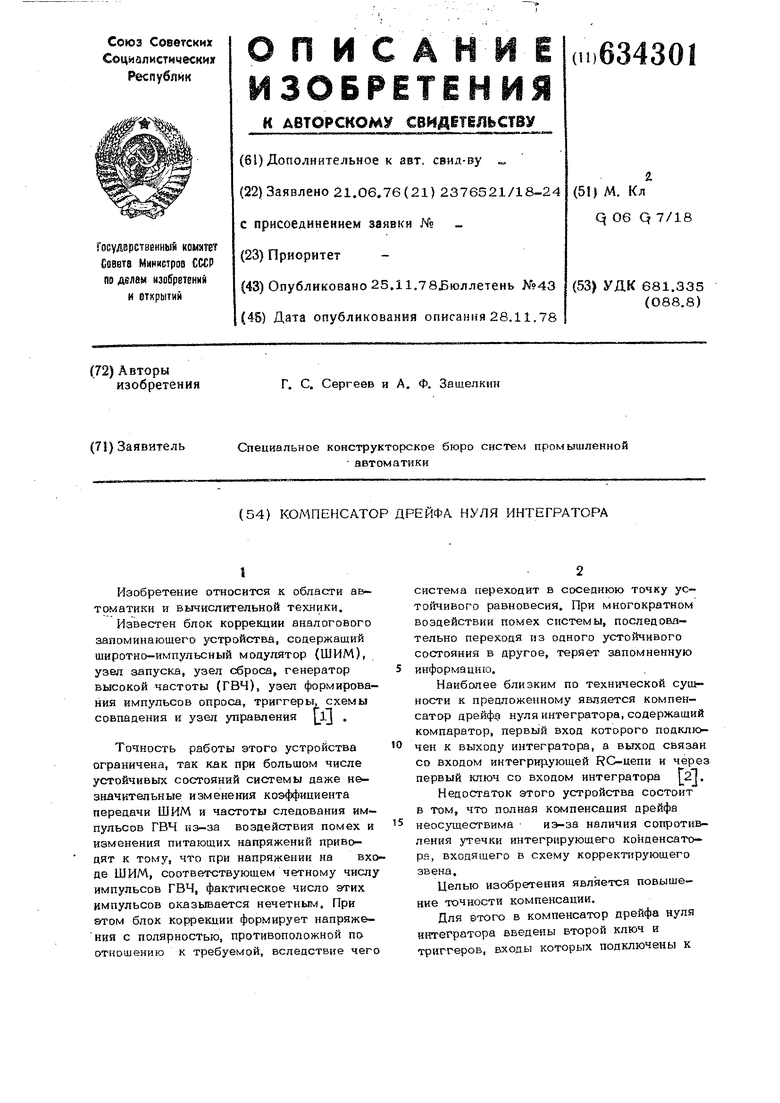

Для ВТОГО в компенсатор дрейфа нуля интегратора введены второй ключ и триггеров, входы которых подключены к выходу интегрирующей F C-цепи и через второй ключ к шине нулевого потенциала, а выхоцы триггеров соединены со вторым вхоаом компаратора. На фиг, 1 представлена блок-схема , компенсатора; на фиг. 2-временные диаграммы, поясняющие его работу. Компенсатор дрейфа нуля интегратора содержит компаратор 1, интегрирующую RO-uenb 2, первый ключ 3, триггеры 4-7, интегратор 8 и второй ключ 9. Первый вход компаратора 1 сое аинен с выходом интегратора 8, выход компаратора 1 соединен через ключ 3 со входом интегратора в и со входом интегрирующей 2, выход которой соединен со входами триггеров 4-7 и через ключ 9 с шиной нулевого потенциала, выходы триггеров соединены со вторым входом компаратора 1. Вход компенсатора подключается к выходу интегратора 8, выход устройства подключается через ключ 3 ко входу интегратора 8. Компаратор 1 служит для выявления знака алгебраической суммы сигналов, подаваемых на его входы со входа устро ства и с выходов триггеров 4-7. Выход ное напряжение компаратора 1 имеет предельное положительное или предельно отрицательное значение соответственно при положительной или отрицательной по лярности напряжения на его входе. Интегрирующая RC-цепь 2 служит дл формирования напряжения, плавно изменя ющегося таким образом, что его проиэводнак по времени имеет знак, совпадающий со знаком выходного напряжения компаратора 1. Триггеры 4-7 представляют собой двухпозипионные реле с гистерезисом, имеющие неодинаковые пороги срабатывания - соответственно1Гпор4...ипор7 выбираемые из следующего условия: Т10р4 триггеры 4-7 выполняют следующи-е функции: а) если напряжение на входах тригг& ров,увеличиваясь, последовательно проходит через значенияНрор ... И пор 7 то в Соответствующие моменты времени переключаются триггеры 4-7, вследстви чего суммарный выходной ток триггеров протекающий между их выходами и вторь входом компаратора 1, уменьшается ска ками - вначале на величину Д , за- причем тем на ыбором значений выходных токов триггеов 4-7 обеспечивается выполнение сл&ующих условий: Д &5, 7 4 б) если напряжение на входах триггеров, уменьшаясь, последовательно прохо дит через значения -11 пор 4 цорт то в результате переключения триггеров 4-7 суммарный выходной ток триггеров увеличивается вначале на величину Д 5 , Д 6 и Д затем на В качестве триггеров 4-7 могут быть использованы, например, интегральные операционные усилители, дополненные цепями положительных обратных связей. На фиг. 2 обозначены: 10 и 11 - выходные напряжения соответственно компаратора 1 и 1 С-цепи 2{ 12, 13, 14 и 15 - выходные токи соответственно триггеров 4, 5, 6 и 7| 16 - сигнал (напряжение или ток) на входе устройства, взятый с обратным знаком; 17 - суммарный выходной ток триггеров 4-7. Если ключ 9 разомкнут и выход компенсатора дрейфа отключен от входа интегратора 8 с помощью ключа 3, то, благодаря наличию следящей системы, состоящей из компаратора 1, ROЦ9пи 2 и триггеров 4-7, сигнал 17 сохраняется равным сигналу 16 с колебаниями с ма-. лой амплитудой, равной амплитуде колебаний сигнала 12, то есть О,5 А . Частота этих колебаний определяется постоянной времени RC-цепи 2, амплитуда колебаний выходного напряжения которого равнаТГпор 4- Если в момент времени tj; сигнал 16 становится больше сигнала 17, то напряжение 10 остается отрицательным до тех пор, пока напряжение 11 не достигнет значения - и пор и не переключится триггер 5, вследствие чего сигнал 13 и постоянная составляющая сигнала 17увеличиваются на величину Ду . При значительном увеличении сигнала 16 а момент времени i-g аналогично переключается триггер 6, увеличивая сигнал 14 и постоянную составляющую сигнала 17 на величину Дл . Если при этом сигнал 17 становится слишком большим, то напряжение 1О остается положительным до тех пор, пока в момент врем&ни tg не переключится обратно триггер 5, уменьшая постоянную составляй)щую сигнала 17 на величину Д . Если в момент времени t замкнуть ключ 9 и поцключить выход компенсатора дрейфа ко входу интегратора 8 с помошью ключа 3, то сигнал 16 фиксируется на достигнутом к моменту времени t j уровне. Действительно, в этом случае входы триггерой 4-7 замкнуты на шину нулевого потенциала, вследствие чего эти триггеры не переключаются и сохраняют состояния, соответствующие моменту врем t , в результате чего сигнал 17 фиксируется на достигнутом к моменту Ьд уровне. Если после этого выходной сигнал интегратора 8 отклоняется от фиксированного значения сигнала 17 (всятедствие неидеальности характеристик интегратора) и становится, например, меньше сигнала 17, то появляется сигнал рассогласования, который усиливается компаратором 1 и воздействует на инт&гратор 8 так, что его выходной сигнал снова принимает значение, равное фиксированному значению сигнала 17, то есть устройство компенсирует дрейф выходного сигнала интегратора 8. Увеличением числа триггеров компенса тора дрейфа можно произвести дальнейшее повышение точности его работы, без снижения помехоустойчивости. Предложенный компенсатор дрейфа выгодно отличается от указанного прототипа - устройство становится некритичнык к помехам, благодаря чему повышается его точность и надежность. Фор му лаизобретения Компенсатор дрейфа нуля интегратора, содержащий компаратор, первый вход которого подключен к выходу интегратора, а выход связан со входом интегрирующей КС-цепи и через первый ключ со входом интегратора, о т л и на ющийся тем, что, с целью повышения точности (Компенсации, он содержит второй ключ и j триггеров, входы которых подключены к выходу интегрирующей RC-цепи и через второй ключ к шине нулевого потенциала, а выходы триггеров соединены со вторым входом компаратора. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство № 473218, кл. Q 11 С 27/Оа, 1974. 2.Смолов В, Б. Аналоговые вычислиВысшая школа тельные машины, М,, 1972, с. 174-175.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ УПРАВЛЕНИЯ ИМПУЛЬСНЫМ СТАБИЛИЗАТОРОМ НАПРЯЖЕНИЯ | 2016 |

|

RU2621071C1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU729640A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Время-импульсный универсальный интегрирующий преобразователь напряжения с функцией широтно-импульсной модуляции | 2020 |

|

RU2731601C1 |

| Преобразователь сопротивления постоянному току в интервал времени | 1984 |

|

SU1237993A1 |

| Компенсационно-параметрический импульсный стабилизатор постоянного напряжения | 1987 |

|

SU1437845A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1559407A2 |

| АНАЛОГОВЫЙ ИНТЕГРАТОР НАПРЯЖЕНИЯ | 2014 |

|

RU2571614C1 |

| СПОСОБ УПРАВЛЕНИЯ ИМПУЛЬСНЫМ СТАБИЛИЗАТОРОМ НАПРЯЖЕНИЯ | 2012 |

|

RU2509337C1 |

| Аналоговый интегратор | 1983 |

|

SU1239730A1 |

Авторы

Даты

1978-11-25—Публикация

1976-06-21—Подача