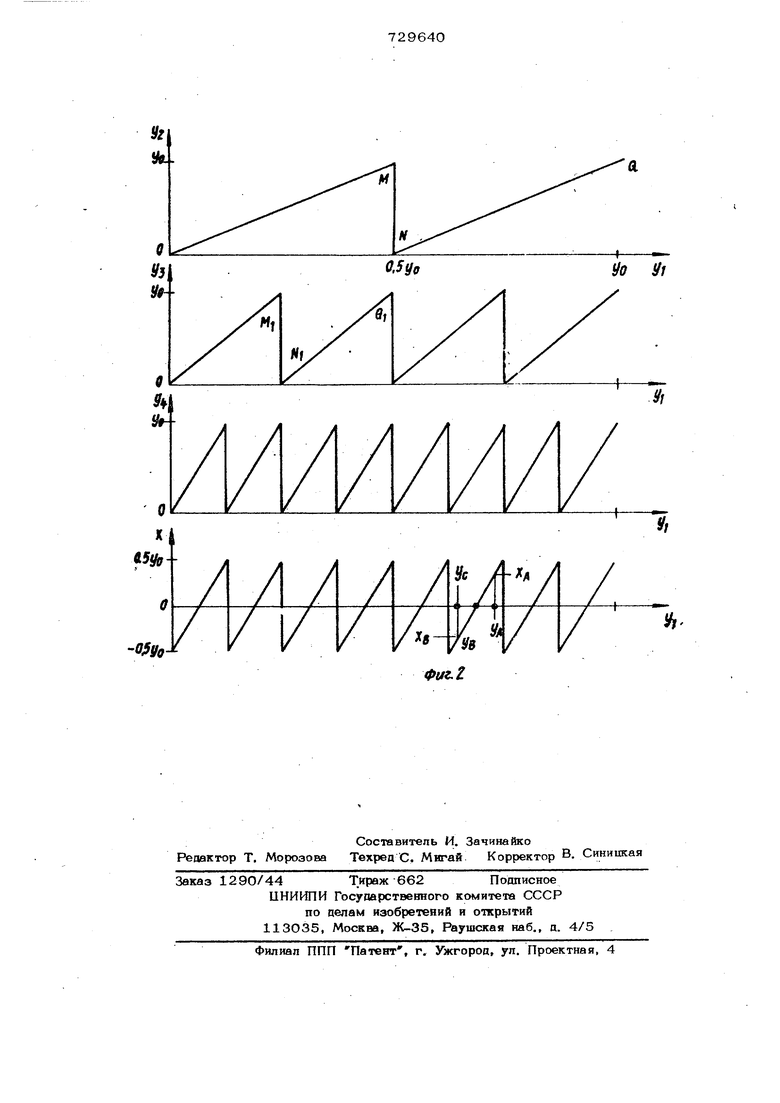

Изобретение относится к автоматике и вычислительной технике и может быть использовано для запоминания аналоговой информации и установках различного назначения. Известно аналоговое запоминающее устройство, содержащее интегратор l, Быстродействие этих устройств ограничено, так как в них процесс запоминания непрерывного сигнала включает в себя промежуточное преобразование напрвгжения в частоту или несколько циклов сравнения запоминаемого сигнала с суммой дискретных сигналов. Из известных устройств наиболее близ КИМ к предлагаемому по технической сущ ности является аналоговое запоминающее устройство, содержащее переключатель, интегратор, вход которого соединен с пер кидным контактом перислючателя, один из контактов которого соединен с входом устройства: между выходом интегратора и другим контактом переключателя включен блок коррекции, выполненный из широтно-импульсного модулятора (ШИМ), генератора выс(жой частоты (ГВЧ),двух триггеров, двух схем совпадения и узла управления 2 . Выходное напряжение интегратора преобразуется с помощью ШИМ в длительность импульсов. В начале каждого импульса ШИМ запускается ГВЧ. Число импульсов, генерируемых ГВЦ за время прохождения одного импульса ШИМ, пропорционально выходному напряжению интегратора. Если это число оказывается четным, то блок коррекции формирует напряжение отрицательной полярности, которое подается на вход интегратора и приводит к увеличению его выходного напряжения. Через некоторое время напряжение интегратора увеличивается настолько, что.число импульсов, генерируемых ГВЧ за время прохождения одного импульса ШИМ, увеличивается на единицу и становится нечетным, вследствие чего бпок коррекции формирует напряжение поожительной полярности, а выходное напряжение интегратора уменьшается. В ре372зультате повторения описанных процессов компенсируется црейф выхоциого напряжения интегратора и это напряжение остается постоянным с колебаниями с малой амплитудой,, а устройство остается в одном из устойчивых состояний, число которых раЬно числу импульсов, генерируемых ГВЧ за время прохождения одного импульса ШИМ. Точность работы этого устройства ограничена, так как при большом числе устойчивых состояний устройства даже незначительные изменения коэффициента пере дачи ШИМ и частоты следования импульсо ГВЧ из-за воздействия помех и изменения питаютаих напряжений приводят к тому, что при напряжении на входе ШИМ, соответствующем четному числу импульсов ГВЧ, фактическое число этих импульсов оказывается нечетным. При этом блок коррекции формирует напряжение с полярностью, противоположной по отношению к требуемой, вследствие чего система пе реходит в соседнюю точку устойчивого равновесия. При многократном воздействии помех система, последовательно пе реходя из одного устойчивого состояния в другое, теряет запомненную информацию. Быстродействие этого устройства так же ограничено, так как его принцип действия основан на преобразовании непреры ного сигнала в длительность импульсов. Целью изобретения является повышение точности и быстродействия аналогового запоминающего устройства. Для этого в аналоговое запоминающее устройство, содержащее ключ, первый вход которого соединен со входом устройства, интегратор, вход которого со динен с выходом ключа, а выход интегра тора соединен с выходом устройства, вве дены послеаова гельно соединенные преобразователи напряжения и блок восстанов-ленйя постоянной составляющей напряже ния, выход которого подсоединен ко второму входу ключа, выход интегратора со динен со входом первого преобразователя напряжения, выход последнего преобразователя напряжения соединен с входом бл ка восстановления постоянной составляю шей напряжения. На фиг. 1 noka3aHa функциональная схема предлагаемого устройства; на фиг. 2 - временная диаграмма работы устройства. Аналоговое запоминающее устройство содержит ключ 1, интегратор 2, блок, во тановления постоянной составляющей напряжения 3, преобразователи напряжения 4.1,4.2,4 . . .4п. Причем каждый преобразователь напряжения 4 выполнен, например, на операционном усилителе 5 и двухпозииионном реле 6. f На фиг. 2 приняты следующие обозначения переменных: V - сигнал на выходе интегратора 2 и входе преобраователя 4.1, Yg И Vi - соответствено сигналы на входах преобразователей 4,2 и 4.3, Yd - сигнал на выходе преобразователя 4.3 и на входе блока 3, X сигнал на выходе блока 3, подаваемый в режиме запоминания сигнала на вход интегратора 2 {с помощью ключа 1 );Ve. -наибольшее значение сигналов VjVp ..iVn В режиме интегрирования связь между выходом блока 3 и входом интегратора 2 разомкнута ключом 1, Двухпозиционное реле преобразовывает сигналов соответствии с выражением |Ь nPMY|$O,SY ASV п.мУ, q5Yp где - сигнал выходе двухпозиционнего реле и на втором входе операционного усилителя. В качестве двухпозиционного реле может быть использован компаратор, допол-- неннь1й входной цепью смещения и выходной цепью ограничения скг-нала. Операционный усипитель преобразо№ 1вает сигнал в соответствии с выражениемVui 2C/j-Zj) где сигналы соответственно на входе и выходе операционного усилителя. Подставив выражение (l) в выражение (2), получаем (IVjПРУ 0,3 Y р0.5М)пРи.0,5Х, График зависимости сигнала Vg от сигнала У, (см. фиг.2), построенный в соответствии с выражением (З) при -1 1, предстевлнет собой ломанную линию 0-М- N-Q. . Из этой характеристики следует, что при изменении сигнала у. от О. до VQ сигнал Ул пважцы изменяется по линейному закону от О по Vg и один раз - с1-:ачгтм от по О, Аналогично в соотве1х:тЕик с в фажением (З), при каждом кзменрнии сиг-нале 57 О по Y, , сигнал Y,, изменяется п линейному закону дважды от О до YQ и один раз - скачком от YQ до О (см., на пример, участок 0-Mj - fS. -Q. графика зависимости сигнала сигнала У ), и так далее. В результате при изменении сигггала от О до Y, сигналы У .Y.-.-. па №1ходах преобразоватепей 4.1, 4.2,...4„ изменяются по линейному закону от О по Чэ соответственно 2,4 .... 2 раз и 1,3...(2 -1) раз - скачком от О Блок восстановления постоянной составляющей напряжения 3, в качестве которого может быть использован суммирую щий усилитель постоянного тока, дополненный входной цепью смещения, преобразует сигнал в соответствии с выражением. rneYf,, иХ - сигналы соответственно на входе и выходе блока 3. На фиг. 2 приварен график зависимое ти сигнала X от сигнала V , построен ный в соответх;твии с выражением (З) и (4) для числа я преобразователей 4,1.. 4п, равного 3. Из рассмотрения этого графика следует, что при изменении выходного сигнала У интегратора 2 от О до УО сигнал X изменяется от - 0,5 Уд до O,5Yo по линейному закону 2 раз и от О.бУбДо -O,5Vo- скачком, (2 -1 раз. В соответствии с г-им графиком, если в момент времени, предшествующий .моменту переключения устройства из режима интегрирования в режим запоминания, сигнал V имеет значение, например, равное Уд , то сигнал в этот момент времени имеет значение, равное . Устройство работает следующим образом. Для переключения устройства из режима интегрирования в режим запоминания необходимо соединить вход интегратора 2 с выходом блока 3 с помощью ключа 1. При Этом на вход интегратора 2 подается сигнал X )д . имеющий положительную полярность, вслеаствие чего выходной сигнал У интегратора 2 уменьшается. По достижении сигналом V значения Vn сигнал V. становится равным нулю, сигнал V перестает изменяться. Если в дальнейшем (например, из-за воздействия помех) сигнал У изме 40 штся на некоторую величину, например, уменьшится до значения У. , то сигнал X становится отрицательным и равным -Х , что приведет к увеличению сигнала V, , т. е. восстановлению его значения YO . Таким образом, после переключения из режима интегрирования в режим запоминания устройство приходит в состояние устойчивого равновесия, при этом запоминается значение выходного сигнала У интегратора, равдое . В зависимости от значения сигнала Y., соответствующе-го моменту переключения из режима интегрирования в режим запоминания, устройство может прийти также и в любое другое устойчивое состояние, причем число этих состояний, определяемое числом изменения полярности сигнала X с отрипательной на положительную при изменении Y| от О до Уд , равно 2 . Точность запоминания сигнала повышается с увеличением числа устойчивых состояний, т. е. с увеличением числа преобразователей 4.1...4п устройства. Это увеличение- не приводит к потере устойчивости устройства в режиме запоминания, так как известно, что устойчивость замкнутой системы, составленной из одного интегратора и нескольких безинерционных звеньев преобразователей 4.1...4п и блока 3, не нарушается при увеличении числа безинерционных звеньев. .„ Устройство имеет достаточно высокую „о ехоустойчивсхзть:. j малейшем изменении выходного сигнала Vj интегратора 2 из-за воздействия помех в режиме запоминания на вход Этого интегратора немедленно поступает по замкнутому контуру усиленный сигнал ) отрицательной обратной связи, который восстанавливает прежнее значение сигнала V . Устройство имеет высокое быстродействие, так как все его блоки преобразователи 4.1...4пи блок 3, используемые для запоминания выходного сигнала интегратора, являются безинерционными. Использование новых блоков преобразователей и блока восстановителей постоянной составляющей напряжения в анаоговом запоминающем устройстве повышает его точность, |Пбмехоустойчивость н быстродействие. Формула изобретения Аналоговое запоминающее устройство, оаержащее ключ, первый пход которого

соециненсо входом устройства, интегратор, вход которого соединен с выходом ключа, а выход интегратора соединено выходом устройства, отпкчагоще е с я тем, что, с целью повыше ни я точности и быстроцейстш1я устройства, внего введены последовательно соединенные преобразователи напряжения и блок восстановления постоянной составляющей напряжения, выход которого подсоединен ко второму входу ключа, выход ин-Гегратора соединен со входом первого

преобразователя напряжения, вьтход послецнего преобразователя напряжения соединен со входом блока восстановления постоянной составляющей напряжения.

Источники информации, принятые во внимание при экспертизе

1. Патент США 3784919, ют, 328-127. опублик. 1974,

2, Авторское свидетельство СССР 473218, кл, G 11 С 27/ОО, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Компенсатор дрейфа нуля интегратора | 1976 |

|

SU634301A1 |

| Времяимпульсный квадратичный преобразователь | 1986 |

|

SU1406610A1 |

| Устройство для интегрирования сигнала | 1981 |

|

SU960853A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU681553A1 |

| Детектор квазиравновесия (его варианты) | 1981 |

|

SU1012191A1 |

| Калибратор напряжения | 1984 |

|

SU1244646A1 |

| Измеритель сдвига фаз | 1985 |

|

SU1298684A2 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ | 1984 |

|

SU1841014A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1316089A1 |

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

А5уо

Авторы

Даты

1980-04-25—Публикация

1977-11-24—Подача