(54) САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА РЕГУЛИРОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНАЯ СИСТЕМА СЛЕЖЕНИЯ ДЛЯ ОБЪЕКТОВ С ЗАПАЗДЫВАНИЕМ ПО УПРАВЛЕНИЮ | 2005 |

|

RU2294005C1 |

| Самонастраивающаяся система управления | 1985 |

|

SU1249478A1 |

| Устройство для регулирования натяжения материала в многосекционной непрерывно-поточной линии | 1988 |

|

SU1664712A1 |

| Самонастраивающаяся система управления | 1977 |

|

SU650053A1 |

| АДАПТИВНАЯ СИСТЕМА СЛЕЖЕНИЯ ДЛЯ ОБЪЕКТОВ С ЗАПАЗДЫВАНИЕМ ПО СОСТОЯНИЮ И УПРАВЛЕНИЮ | 2005 |

|

RU2294004C1 |

| Самонастраивающаяся система | 1981 |

|

SU1013910A1 |

| САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ НЕСТАЦИОНАРНЫМ ОБЪЕКТОМ | 2002 |

|

RU2230350C2 |

| Нелинейный адаптивный регулятор | 1985 |

|

SU1303994A1 |

| Самонастраивающаяся система | 1980 |

|

SU928302A1 |

| Устройство для функционального контроля систем управления | 1983 |

|

SU1145323A1 |

1

Изобретение относится к области автоматики, в частности к самонастраивающимся системам регулирования с эталонной моделью.

Известна самонастраивающаяся система регулирования, содержащая эталонную модель, первый блок деления и последовательно соединенные сумматор, усилитель и второй блок деления, выход которого соединен с входом объекта регулирования.

Недостатком известной системы является низкая точность работы при мультипликативных помехах, воздействующих на объект регулирования.

Предлагаемая самонастраивающаяся система регулирования отличается тем, что в ней установлены два блока упреждения, выход первого из которых через эталонную модель подключен к одному из входов первого блока деления, выход второго - к другому входу первого блока деления, выход которого соединен с одним из входов второго блока деления, а входы первого и второго блоков упреждения - соответственно к входу и выходу объекта регулирования.

Блок упреждения представляет собой два последовательно соединенных дифференцирующих звена.

Блок деления выполнен в виде последовательно соединенных первого определителя модуля, сравнивающего элемента и интегратора, выход которого соединен с одним из входов сравнивающего элемента через умножитель, а к одному из входов умножителя подключен второй определитель модуля. Между сравнивающим элементом и интегратором установлен второй умножитель, один из входов первого и

второго умножителей связан соответственное входом и выходом введенного дополнительно функционального генератора.

Интегратор изготовлен в виде последовательного соединения преобразователя напряжения в частоту, первого элемента И, цифрового счетчика и цифроаналогового преобразователя. Вход преобразователя напряжения в частоту через последовательно соединенные пороговое зстройство и второй элемент И

связан с одним из входов цифрового счетчика. Выход преобразователя напряжения в частоту подключен к одному из входов второго элемента И, а один из выходов порогового устройства - к одному из входов первого элемента И.

Такое построение функциональной схемы самонастраивающейся системы повыщает

точность регулирования при воздействии на объект регулирования мультипликативных помех.

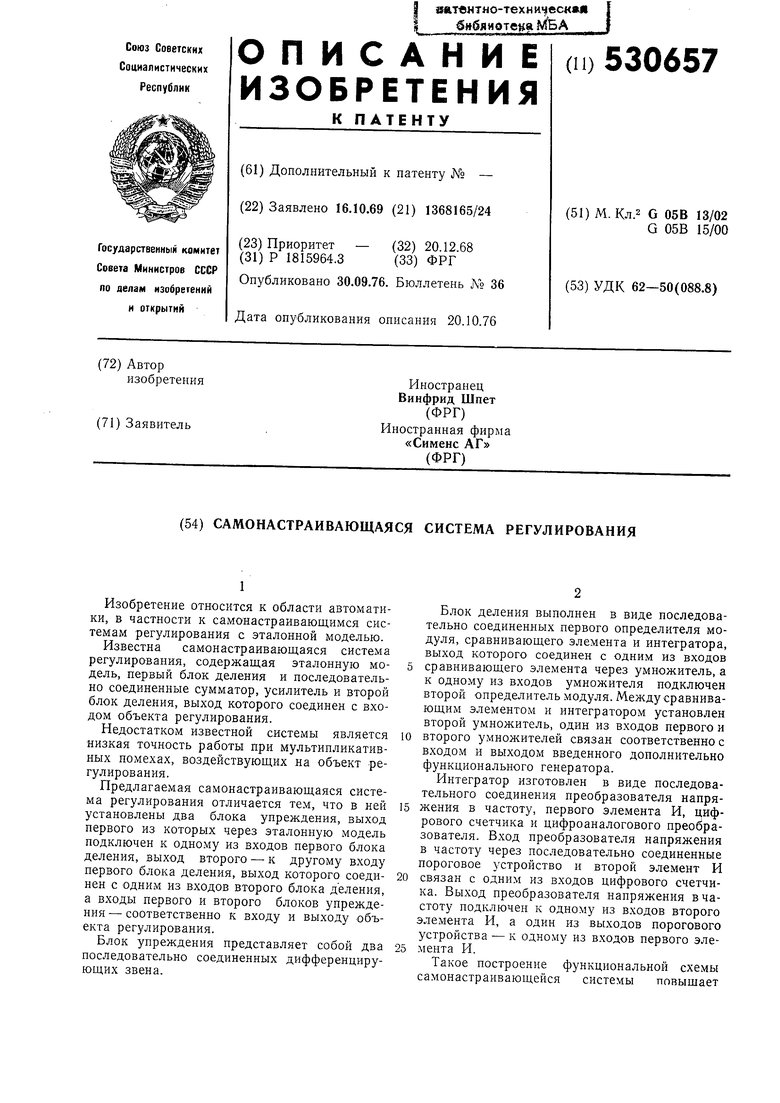

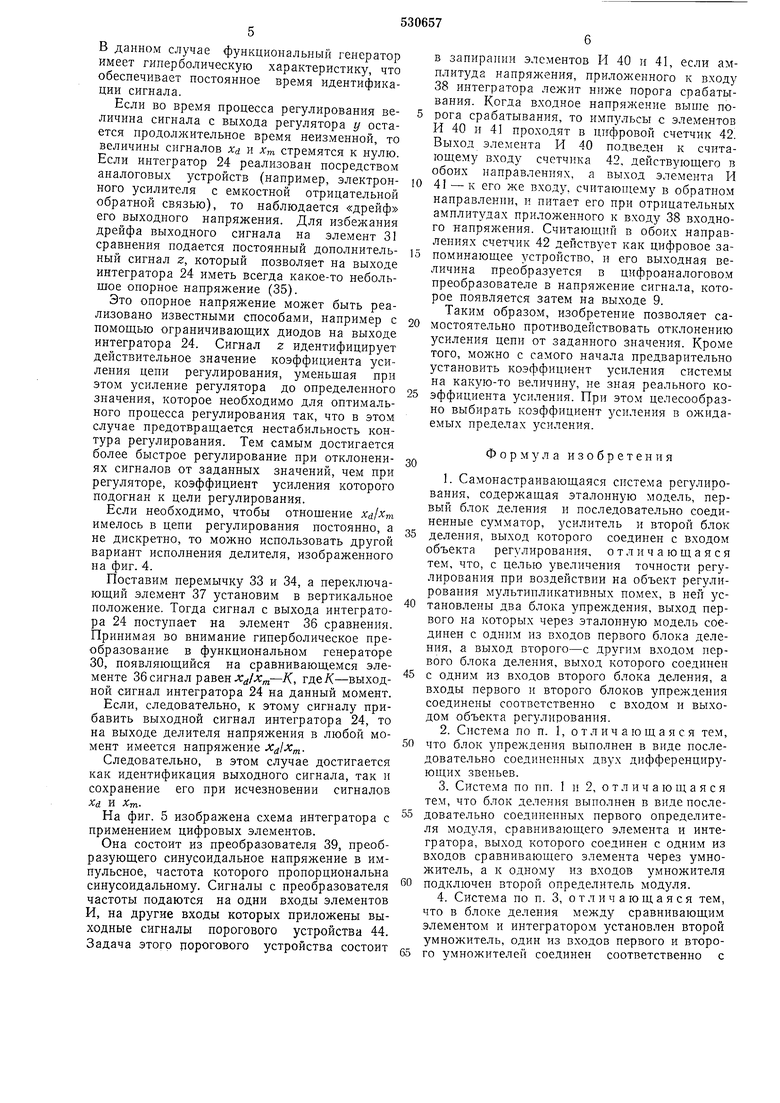

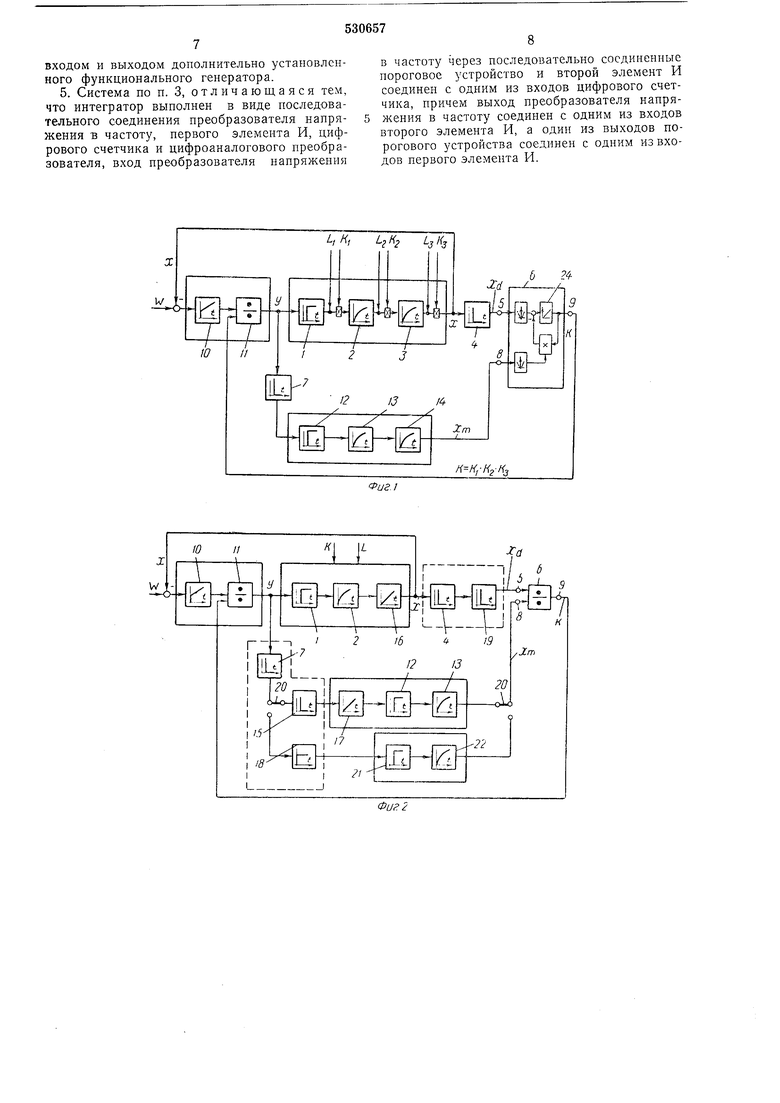

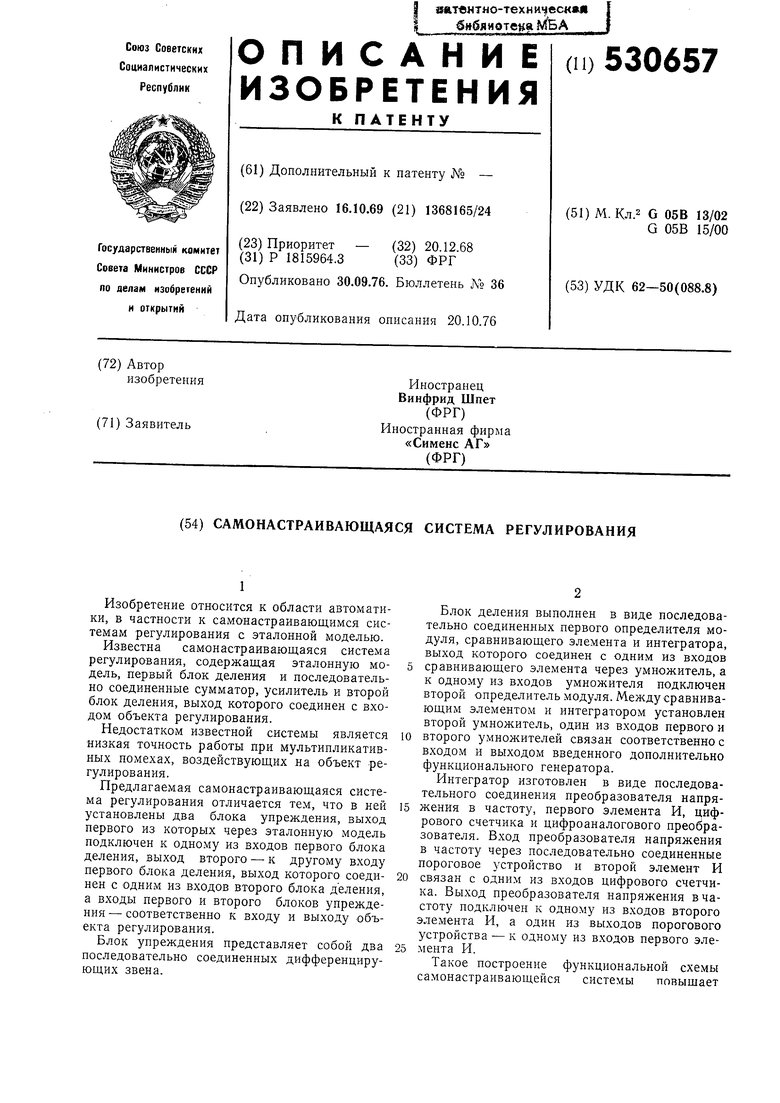

На фиг. 1 и 2 изображена функциональная схема системы регулирования; на фиг. 3, 4- блок деления; на фиг. 5-функциональная схема интегратора.

На схемах приняты следующие обозначения: W - сигнал регулирования; у - выходной сигнал регулятора; ха - сигнал с выхода объекта регулирования; Хт - сигнал с выхода эталонной модели; К - коэффициент усиления системы; К, Kz, Кз - мультипликативные цомехи; LI, LZ, LZ - аддитивные помехи; Z - постоянный дополнительный сигнал на входе блока деления. Система содержит следующие элементы, показанные на фиг. 1-5, где 1 - звено заназдывания объекта регулирования; 2, 3 - апериодические звенья объекта регулирования; 4 - блок упреждения; 5- вход блока деления; 6 - блок деления; 7- блок упреждения; 8 и 9-вход и )Д блока 6 деления; 10 - усилитель; И - блок деления; 12 - блок запаздывания эталонной модели; 13, 14 - анериодические звенья эталонной модели; 15 - блок упреждения; 16, 17-интеграторы; 18-пропорциональное звено; 19 - блок упреждения; 20 - переключающий элемент; 21-звено заназдывания эталонной модели; 22-апериодический блок эталонной модели; 23-элемент сравнения; 24- интегратор; 25-умножитель; 26-первый определитель модуля; 27 - второй определитель модуля; 28 и 29-вход и выход функционального генератора 30; 31-элемент сравнения; 32-умножитель; 33, 34-перемычка; 35-пороговое напряжение на выходе интегратора; 36-элемент сравнения; 37-переключающий элемент; 38-вход интегратора; 39-преобразователь напряжения в частоту; 40,41-элементы И; 42 - цифровой счетчик импульсов; 43-цифроаналоговый преобразователь; 44-пороговое устройство.

Самонастраивающая система работает следующим образом.

На вход регулятора подается сигнал регулирования, который сравнивается с сигналом X с выхода объекта регулирования, а на вход его поступает сигнал с выхода регулятора х. Кроме того, на объект регулирования непосредственно воздействуют аддитивно наложенные помехи LI, L2, LZ и мультипликативно наложенные помехи Ki, Kz и Кз, причем только последние изменяют усиление в прямой цени регулирования. Представим объект регулирования последовательно соединенными звеном 1 запаздывания и двумя апериодическими звеньями 2 и 3 (фиг. 1). Блок 4 упреждения не пропускает аддитивные помехи Li, LS, LS. Установка упреждающего блока 7 позволяет обеспечить одинаковые фазовые сдвиги сигналов Xd и Хт, отношение которых XdlXm

пропорционально произведению K Ki-K2Kz, которое необходимо скомпенсировать путем подачи на блок 11 деления отнощения

Xm/Xd.

На фиг. 2 представлен вариант вынолнения функциональной схемы системы регулирования, когда объект регулирования вместо одного анериодического звена 3 содержит интегратор 16, и соответствующее этому случаю выполнение блоков 4 и 7 упреждения, состоящих из последовательно соединенных дифференцирующих звеньев.

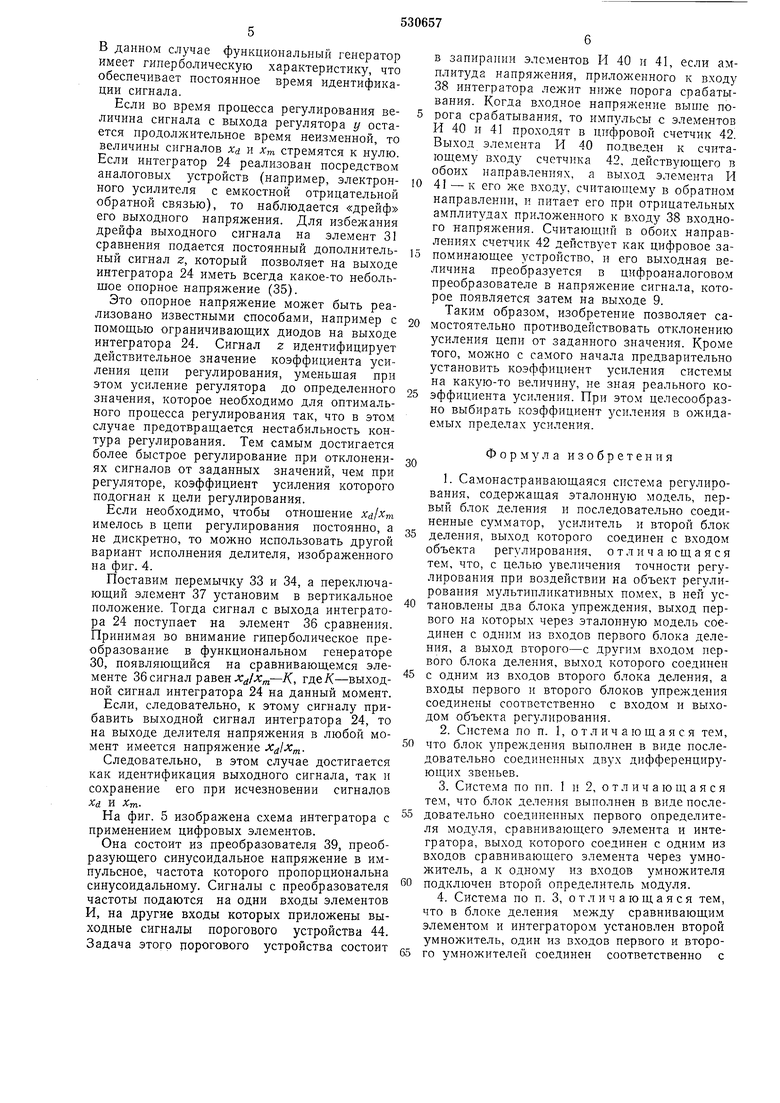

На фиг. 3 нредставлена схема блока 6 (И) деления. Сигналы Хт и Xd проходят соответственно через первый 26 и второй 27 определители модуля, умножитель 25. Интегратор 24

позволяет запомнить значение сигнала на выходе блока деления при исчезновении сигналов Xd и Хт.

На фиг. 4 изображена другая функциональная схема выполнения блока деления. Работа

его осуществляется следующим образом: сигнал с выхода объекта регулирования поступает в элемент 31 сравнения, затем через умножитель 32 подается в интегратор 24, а с выхода интегратора 24 через умножитель 25 поступает на элемент 31 сравнения, где сравнивается с дополнительным постоянным сигналом 2 и с выходным сигналом Xd.

На вход умножителя 25 поступает сигнал Хт с эталонной модели, а на вход умножителя

32 подается также сигнал Хт, но пропущенный через функциональный генератор 30. Наличие интегратора 24 в данной схеме, как и в схеме, изображенной и на фиг. 3, позволяет заномнить значение сигналов на выходе блока деления при исчезновении сигналов х, и Хт. В отличие от нредыдущей схемы блока деления, изображенной на фиг. 3, здесь на входной контур и на контур отрицательной обратной связи действуют не действительные

значения величин Xd и Хт, а алгебраические величины ±Xd и ±Хт с учетом знака. Поэтому в данном случае имеющаяся во входном сигнале высокочастотная составляющая щумовых номех подавляется интегратором 24, поскольку обратное значение времени интегрирования TI достаточно мало по отношению к имеющимся высокочастотным шумам, хотя последние, как правило, всегда имеют место. Так как сигналы Ха и Хт могут

иметь разные знаки, то при изменении знака сигнала Хт, которое происходит одновременно с изменением полярного сигнала ха (оба эти сигнала синфазны), изменяется и знак входного сигнала интегратора 24. Знак направления регулирования системы, состоящей из интегратора 24, умножителей 32 и 25, не меняется. Смена знака входного сигнала интегратора осуществляется с помощью функционального генератора 30.

Для обеспечения правильного направления регулирования функциональный генератор 30 должен был бы выполнять только функцию смены знака входного сигнала Хт и его характеристика могла бы быть линейной, например, как у инвертирующего усиления.

В данном случае функциональный генератор имеет гиперболическую характеристику, что обеспечивает постоянное время идентификации сигнала.

Если во время процесса регулирования величина сигнала с выхода регулятора у остается продолжительное время неизменной, то величины сигналов ха и Хт стремятся к нулю. Если интегратор 24 реализован посредством аналоговых устройств (например, электронного усилителя с емкостной отрицательной обратной связью), то наблюдается «дрейф его выходного напряжения. Для избежания дрейфа выходного сигнала на элемент 31 сравнения подается постоянный дополнительный сигнал г, который позволяет на выходе интегратора 24 иметь всегда какое-то небольшое опорное напряжение (35).

Это опорное напряжение может быть реализовано известными способами, например с помощью ограничивающих диодов на выходе интегратора 24. Сигнал z идентифицирует действительное значение коэффициента усиления цепи регулирования, уменьшая при этом усиление регулятора до определенного значения, которое необходимо для оптимального процесса регулирования так, что в этом случае предотвращается нестабильность контура регулирования. Тем самым достигается более быстрое регулирование при отклонениях сигналов от заданных значений, чем при регуляторе, коэффициент усиления которого подогнан к цели регулирования.

Если необходимо, чтобы отношение XdJXm имелось в цепи регулирования постоянно, а не дискретно, то можно использовать другой вариант исполнения делителя, изображенного на фиг. 4.

Поставим перемычку 33 и 34, а переключающий элемент 37 установим в вертикальное положение. Тогда сигнал с выхода интегратора 24 поступает на элемент 36 сравнения. Принимая во внимание гиперболическое преобразование в функциональном генераторе 30, появляющийся на сравнивающемся элементе 36 сигнал равенлг /л т--. гдеЯ-выходной сигнал интегратора 24 на данный момент.

Если, следовательно, к этому сигналу прибавить выходной сигнал интегратора 24, то на выходе делителя напряжения в любой момент имеется напряжение .

Следовательно, в этом случае достигается как идентификация выходного сигнала, так и сохранение его при исчезновении сигналов

Xd и Хт.

На фиг. 5 изображена схема интегратора с применением цифровых элементов.

Она состоит из преобразователя 39, преобразующего синусоидальное напряжение в импульсное, частота которого пропорциональна синусоидальному. Сигналы с преобразователя частоты подаются на одни входы элементов И, на другие входы которых приложены выходные сигналы порогового устройства 44. Задача этого порогового устройства состоит

6

в запирании элементов И 40 и 41, если амплитуда напряжения, прилол енного к входу 38 интегратора лежит ниже порога срабатывания. Когда входное напряжение выше порога срабатывания, то импульсы с элементов И 40 и 41 проходят в цифровой счетчик 42. Выход элемента И 40 подведен к считающему входу счетчика 42, действующего в обоих направлениях, а выход элемента И

41 - к его же входу, считаюп ему в обратном направлении, и питает его при отрицательных амплитудах приложенного к входу 38 входного напряжения. Считающий в обоих направлениях счетчик 42 действует как цифровое запоминающее устройство, и его выходная величина преобразуется в цифроаналоговом преобразователе в напряжение сигнала, которое появляется затем на выходе 9. Таким образом, изобретение позволяет самостоятельно противодействовать отклонению усиления цепи от заданного значения. Кроме того, можно с самого начала предварительно установить коэффициент усиления системы на какую-то величину, не зная реального коэффициеита усиления. При этом целесообразно выбирать коэффициент усиления в ожидаемых пределах усиления.

Формула изобретения

входом и выходом дополнительно установленного функционального генератора.

IV

Г т

-7 /2

и

-7

1213/4

Б

в частоту через последовательно соединенные пороговое устройство и второй элемент И соединен с одним из входов цифрового счетчика, причем выход преобразователя напряжения в частоту соединен с одним из входов второго элемента И, а один из выходов порогового устройства соединен с одним из входов первого элемента И.

/1 л;-лг-/г,

36 JS

Авторы

Даты

1976-09-30—Публикация

1969-10-16—Подача