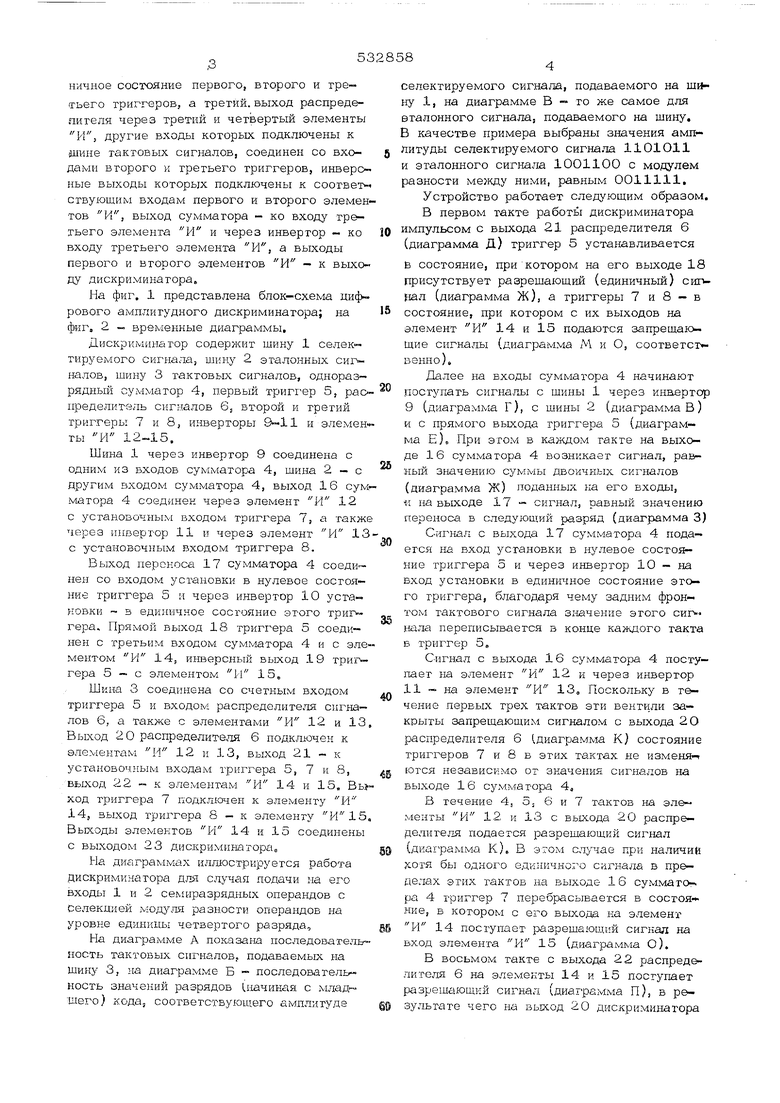

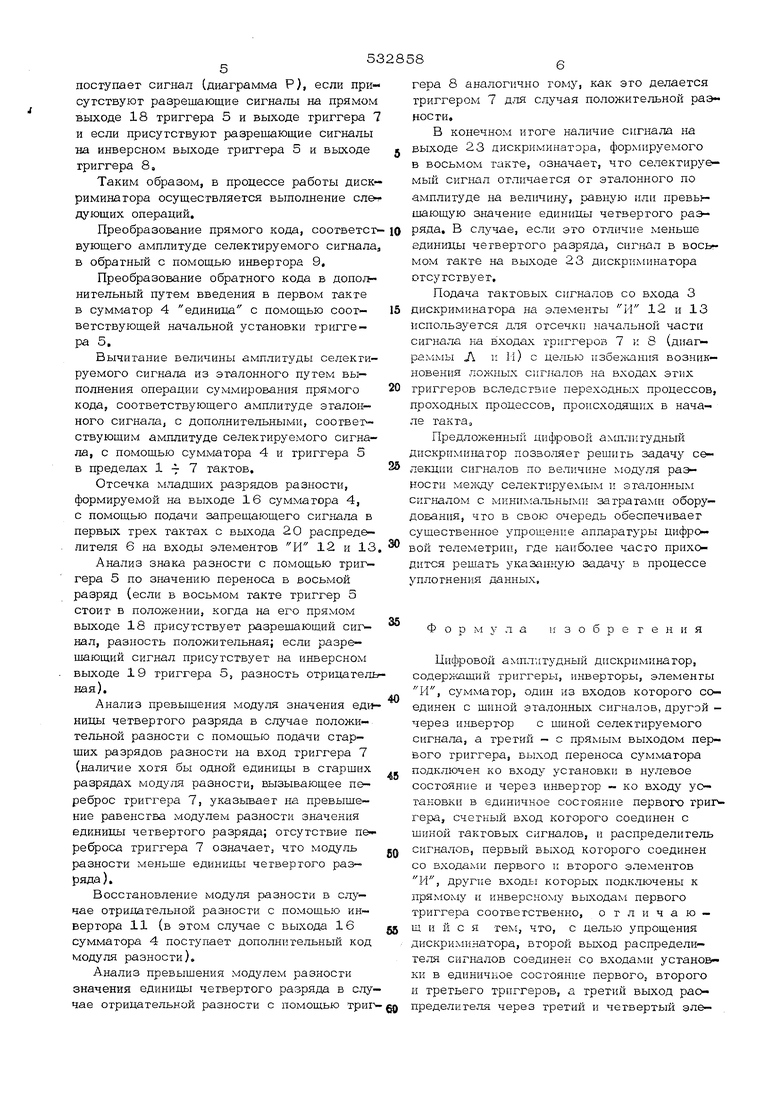

(54) ЦИФРОВОЙ А/ ШЛИТУДНЫЙ ДИСКРШлИНАТОР ничное состояние первого, второго и третьего триггеров, а третий.выход распредепитепя через третий и четвертый элементы И, другие входы которых подключены к 1шине тактовых сигналов, соединен со входами второго и третьего триггеров, инверсные выходы которых подключены к соответствующим входам первого и второго элемен тов И, выход сумматора - ко входу третьего элемента И и через инвертор - ко входу третьего элемента И, а выходы первого и второго элементов И - к выходу дискриминатора. На фиг, 1 представлена блок-схема цифрового амплитудного дискриминатора; на фиг, 2 - временные диаграммы. Дискриминатор содержит шину 1 селектируемого сигнала, шину 2 эталонных сигналов, шину 3 тактовых сигналов, одноразрядный сумматор 4, первый триггер 5, рас пределитель сигналов 6, второй и третий триггеры 7 и 8, инверторы и элемен ты И 12-15, Шина 1 через инвертор 9 соединена с одним из входов сумматора 4, шина 2 - с другим входом сумматора 4, выход 16 сум матора 4 соединен через элемент И 12 с установочным входом триггера 7, а такж через инвертор 11 и через элемент И 13 с установочным входом триггера 8. Выход нероноса 17 сумматора 4 соеди™ нен со входом установки в нулевое состояние триггера 5 и через инвертор 10 устаковки в единичное состояние этого триггера. Прямой выход 18 триггера 5 соединен с третьим входом сумматора 4 и с эле ментом И 14, инверсный выход 19 триггера 5 с элементом И 15« Шина 3 соединена со счетным входом триггера 5 и входом распределите.ш сигналов 6, а также с элементами И 12 и 13 Выход 20 распределителя 6 подключен к элементам И 12 и 13, выход 21 - к установочным входам триггера 5, 7 и 8, выход 22 -. к элементам И 14 и 15„ Вь ход триггера 7 подключен к элементу И 14, выход триггера 8 - к элементу И 15 Выходы элементов И 14 и 15 соединены с выходом 23 дискриминатора На диаграммах иллюстрируется работа дискриминатора д.ля случая подачи на его входы 1 и 2 семиразрядных операндов с Селекцией модуля разности операндов на уровне единины четвертого разряда. На диаграмме А показана последователь ность тактовых сигналов, подаваемых на Шину 3, на диаграмме Б - последователь ность значений разрядов (начиная с млад Шего) кода, соответствуюш,его амплитуде електируемого сигнала, подаваемого на шиу 1, на диаграмме В - то же самое для талонного сигнала, подаваемого на шину. качестве примера выбраны значения ампитуды селектируемого сигнала 1101011 эталонного сигнала 1001100 с модулем азности ними, равным 0011111, Устройство работает следующим образом, В первом такте работы дискриминатора мпульсом с выхода 21 распределителя 6 (диаграмма Д) триггер 5 устанавливается 8состояние, при котором на его выходе 18 присутствует разрешаюший (единичный) СИРЯал (диаграмма Ж), а триггеры 7 и 8 - в состояние, при котором с их выходов на элемент И 14 и 15 подаются запрещак щие сигналы (диаграмма М и О, соответственно). Далее на входы сумматора 4 начинают постуг ать сигналы с шины 1 через инвертор 9(диаграмма Г), с шины 2 (диаграмма В) и с прямого выхода триггера 5 (диаграмма Е), При этом в каждом такте на выходе 16 сумматора 4 возникает сигнал, равный значению суммы двоичных сигналов (диаграмма Ж) поданных на его входы, « на выходе 17 - сигнал, равный значению переноса в следующий разряд (диаграмма 3) Сигнал с выхода 17 сумматора 4 подается на вход установки в нулевое состояние триггера 5 и через инвертор 10 - на вход установки в единичное состояние этого триггера, благодаря чему задним фронтом тактового сигнала значение этого . нала переписывается в конце каждого такта Б триггер 5, Сигнал с выхода 16 сумматора 4 поступает на элемент И 12 и через инвертор 11 на элемент И 13, Поскольку в течение первых трех тактов эти вентили закрыты запрещающим сигналом с выхода 2 О распределителя 6 Диаграмма К) состояние триггеров 7 и 8 в этих тактах не изменя-ч ются независимо от значения сигналов на вь1ходе 16 сумма тора 4, В течение 4, о5 6 и 7 тактов на элементы И 12 и 13 с выхода 20 распределителя подается разрешающий сигнал (диаграмма К), В этом случае при наличии хотя бы одного единично.го сигнала в пределах этих тактов на выходе 16 сумматора 4 триггер 7 перебрасывается в состояние, в котором с его выхода на элемент И 14 поступает разрешающий сигнал на вход элемента И 15 (диаграмма О). В восьмом такте с вьхсда 22 распределителя 6 на элементы 14 и 15 поступает разрешающий сигнал (диаграмма П), в результате чего на вьрсод 20 дискриминатора

поступает сигнал (диаграмма Р), если присутствуют разрешающие сигналы на прямом выходе 18 триггера 5 и выходе триггера 7 и если присутствуют разрешающие сигналы на инверсном выходе триггера 5 и выходе триггера 8,

Таким образом, в процессе работы дискриминатора осуществляется выполнение сл&тдующих операций. Преобразование прямого кода, соответст- ю вующего амплитуде селектируемого сигнала в обратный с помощью инвертора 9, Преобразование обратного кода в дополнительный путем введения в первом такте в сумматор 4 единица с помощью соответствующей начальной установки триггера 5. Вычитание величины амплитуды селекти руемого сигнала из эталонного путем выполнения операции суммирования прямого кода, соответствующего амплитуде эталонного сигнала; с дополнительными, соответствующим амплитуде селектируемого сигна ла, с помощью сумматора 4 и триггера 5 в пределах 1-77 тактов. Отсечка младщих разрядов разности, формируемой на выходе 16 сумматора 4, с помощью подачи запрещающего сигнала в первых трех тактах с выхода 20 распределителя 6 на входы элементов И 12 и 13 Анализ знака разности с помощью триггера 5 по значению переноса в восьмой разряд (если в восьмом такте триггер 5 стоит в положении, когда на его прямом выходе 18 присутствует разрешающий сигнал, разность положительная; если разре- щающий сигнал присутствует на инверсном выходе 19 триггера 5, разность отрицател ная), Анализ превышения модуля значения еди ницы четвертого разряда в случае положительной разности с помощью подачи старших разрядов разности на вход триггера 7 (наличие хотя бы одной единицы в старших разрядах модуля разности, вызывающее переброс триггера 7, указьшает на превышение равенства модулем разности значения единицы четвертого разряда; отсутствие переброса триггера 7 означает, что модуль разности меньше единицы четвертого разряда). Восстановление модуля разности в случае отрицательной разности с помощью инвертора 11 (в этом случае с выхода 16 сумматора 4 поступает дополнительный код модуля разности). Алализ превышения модулем разности значения единицы четвертого разряда в слу чае отрицательной разности с помощью триг

гера 8 аналогично тому, как это делается триггером 7 для случая положительной раэности,

В конечном итоге наличие сигнала на выходе 23 дискриминатора, формируемого в восьмом такте, означает, что селектируемый сигнал отличается от эталонного по амплитуде на величину, равную или превышающую значение единицы четвертого раэряда, В случае, если это отличие меньше единицы четвертого разряда, сигнал в восьмом такте на выходе 23 дискриминатора отсутствует. Подача тактовых сигналов со входа 3 дискриминатора на элементы И 12 и 13 используется для отсечки 11ачальной части сигнала на входах триггеров 7 и 8 (диаграммы JV и М) с целью избей- ания возникновения лол-сных сигналов на входах этих триггеров вследствие переходных процессов, проходных процессов, происходяших в начале такта Предложенный цифровой амплитудный Дискриминатор позволяет решить задачу селекции сигналов по величине модуля разности мелоду селектируемым и эталонным сигналом с минимальными затратами оборудования, что в свою очередь обеспечивает существенное упрощение аппаратуры цифровой телеметрии; где наиболее часто приходится решать указанную задачу в процессе уплотнения данных. Ф о а м V л зобретения Цифровой амплитудный дискриминатор, содержащий триггеры, инверторы, элементы И, сумматор, один из входов которого соединен с шиной эталонных сигналов, другой через инвертор с шиной селектируемого сигнала, а третий - с прямым выходом перiBoro триггера, выход переноса сумматора подключен ко входу установки в нулевое состояние и через инвертор - ко входу установки в единичное состояние первого триггера, счетный вход которого соединен с шиной тактовых сигналов, и распределитель сигналов, первый выход которого соединен со входами первого и второго элементов И, другие входы которых подключены к прямому н инверсному выходам первого триггера соответственно, о т л и ч а ю - ш и и с я тем, что, с целью упрощения дискриминатора, второй выход распределителя сигналов соединен со входами установки в единичное состояние первого, второго и третьего триггеров, а третий выход раопределителя через третий и четвертый элеменгы И, другие входы которых подключены к шине гакговых сигналов, соединен со входами второго и третьего триггеров, ш-шерсные зыход.ь; которых подключены к соогветстБующим входам первого и второго Зочементов Il, выход сумматора -ко входу тоетьего элемента И и через инвертор ко входу четвертого элемента И, а вь5ходы первого и второго элементов И - к выходу дискриминатора.

ticTOHHHKH информации, принятые во внимание при экспертизе:

1.Чу Я. Организация ЭВМ и микропрограмтч/гирование, Нью-Джерси, 1972,

стр. 246-252.

2.Панернов А, А. Логические основы УВТ , М., Советское радио, 1972 г., стр. 187-293.

3.Патент США. № 381 ЮЗ9, класс 235-16Я от 14,02.74 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой амплитудный дискриминатор | 1982 |

|

SU1073769A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

| Устройство для считывания графической информации | 1984 |

|

SU1182553A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Функциональный преобразователь угла поворота вала в код | 1982 |

|

SU1080174A1 |

. г

Авторы

Даты

1976-10-25—Публикация

1973-06-15—Подача