Изобретение относится к области автоматики и вычислительной техники и может быть использовано для селекции сигналов по величине рАзности между амплитудами селектируемого и эталонного сигналов, например, при сжатии данных в телеметрии.

Известен цифровой амплитудный дискриминатор на базе двоичного логико-арифметического устройства, содержащий триггеры, инверторы, элементы И, сумматор и распределитель сигналов l .

Недостатком этого дискриминатора является его сложность и низкое быстродействие, что ограничивает возможность его использования в аппаратуре обработки данных для селекции сигналов, так как для выполнения каждой очередной операции необходим возврат результата предыдущей операции на вход устройства.

Наиболее близким по технической сущности к предложенномуявляется цифровой амплитудный дискриминатор содержащий триггеры, инверторы,элементы И, сумматор, один из входов которого соединен с шиной эталонных сигналов, другой - через инвертор с шиной селектируемого сигнала, а третий - с прямым выходом первого триггера, выход переноса сумматора подключен к входу установки в нулевое состояние и через инвертор к входу установки в единичное состояние первого триггера, счетный вход которого соединен с шиной тактовых сигналов, и распределитель сигналов первый выход которого соединен с входами первого и второго элементов И, другие входы которых подключены к прямому и инверсному выходам первого триггера соответственно, второй выход распределителя соединен с входами установки в единичное состояние первого, второго и третьего триггеров, а третий выход распределителя через третий и четвертый элементы И, другие входы которых подключены к шине тактовых сигналов , соединен с входами второго и третьего триггеров, инверсные выходы которых подключены к соответствующим входам первого и второго элементов И, выход сумматора - к входу третьего элемента И и через инвертор - к входу четвертого элемента И, а выходы первого и второго элементов И - к выходу дискриминатора.

Недостатком описанного дискриминатора является несимметричность селекции сигналов относительно эталонного, возникающая в .результате неполного восстановления модул разности при отрицательном значении

разности с потерей единицы младшего разряда модуля, что приводит к потере точности при селекции сигналов, когда допустимая разность между эталоном и селектируемым сигналами мала и сравнима со значением единиц младшего разряда.

Цель изобретения - повышение точности работы дискриминатора. I

Поставленная цель достигается

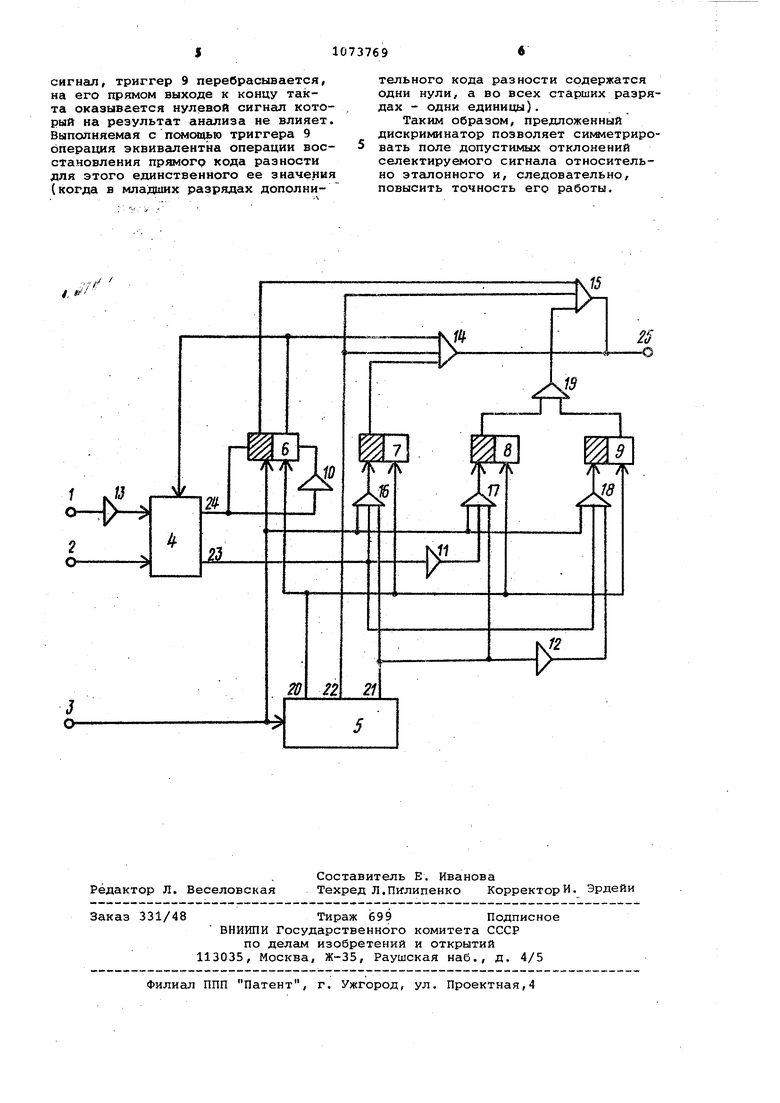

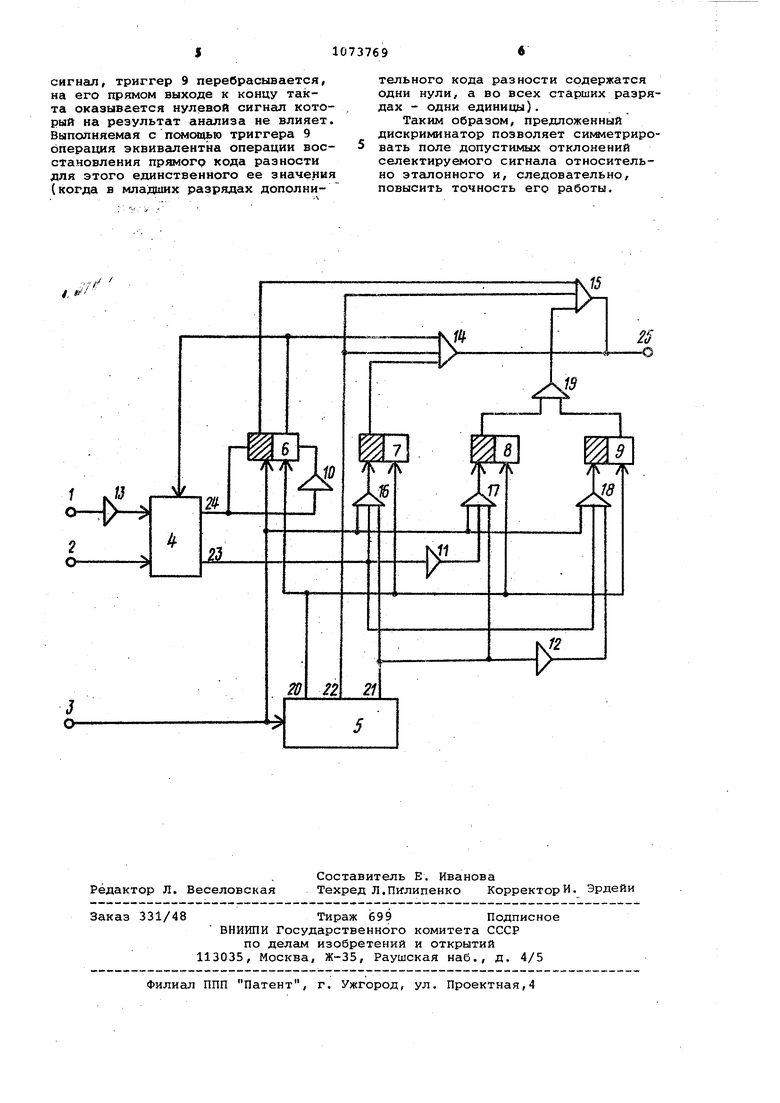

тем, что в цифровой амплитудный дискриминатор, содержащий распределитель импульсов, три триггера, три элемента НЕ, четыре элемента И, сумматор, один из входов KO.voporo соединен с шиной эталонных сигналов дискриминатора, другой через первый элемент НЕ - с шиной селектируемого сигнала дискриминатора, а третий с прямым выходом первого триггера, выхо;; переноса сумматора подключен к входу установки в нулевое состояние и через второй элемент НЕ к вхоДУ устёмовки в единичное состояние перзохо триггера, счетный вход которого соединен с шиной тактовых сигналов дискриминатора, выход сигнала считывания распределителя сигналов соединен с первыми входами первого и второго элементов И, вторые которых подключены соответственно к прямому и инверсному выходам первого триггера, выход начальной установки распределителя сигналов соединен с входами установки в единичное состояние первого, второго и третьего триггеров, выход блокировки распределителя сигналов соединен с первыми входами третьего и четвертого элементов И, вторые входы которых подключены к шине тактовых сигналов дискриминатора, выхо суммы сумматора соединен с третьими входдами третьего и через третий элемент НЕ четвертого элемента И, выходьл которых подключены к входам установки в О соответственно вторго и третьего триггеров, инверсный выход второго триггера соединен с третьим входом первого элемента И, выходкоторого подключен к выходу второго элемента И- и выходной шине дискриминатора, введены четвертые триггер и элемент НЕ, пятый элемент И и элемент ИЛИ, вход которого соединен с инверсными и прямыми выходами соответственно третьего и четвертого триггеров, а выход - с третьим входом второго элемента И, вход установки в единичное состояние четвертого триггера подключен к выходу начальной установки распределителя сигналов, а вход установ и в О - с выходом пятого элемента И, входы которого соединены соответственно с шиной тактовых сигналов дискриминатора, выходом суммы сумматора и через четвертый элемент НЕ с выходом блокировки распределителя сигналов. На чертеже представлена функцио нальная схема устройства. Дискриминатор содержит шины 1-3 суглматор 4, распределитель сигналов 5, триггеры 6-9, элементы НЕ 10-13, элементы И.14-18 и элементы ИЛИ 19. Дискриминатор работает следующим образом. По шине 3 на вход распределител сигналов 5 осуществляется подача тактовых сигналов, причем полный цикл работы дискриминатора состоит из числа тактов, на единицу больше го разрядности сравниваемых операн дов. При этом распределитель сигна лов 5 в пределах одного цикла формирует следующие сигналы: на выходе 20 сигнал в начальной части первого такта, осуществляющий установку в единичное состояние триг геров 6-9, на выходе 21 - сигнал, запираюпий в течение первых тактов элемен.гы И 16 и 17 и благодаря элементу НЕ 12 удерживающий в открытом состоянии в это же время эл мент И 18, на выходе 22 - сигнал, разрешающий на последнем такте цик ла отпирание элементов И 14 и 15 и считывание сигналов результата сра нения. Число п определяет максимальное значение модуля разности между селектируемым и эталонным сигналами, при котором эти сигналы признаются равными (например, при максимальное значение модуля разности составляет 111). I Начиная с первого такта в сумматор 4 синхронно с тактовыми сигналами поступают код селектируемого сигнала по шине 1 через элемент НЕ 13 и код эталонного сигнала по шине 2. Подача кодов осуществляется младшими разрядами вперед. Благодаря элементу НЕ 13 код селектируемого сигнала преобразуется в обратный код, а благодаря начальной установк триггера 6 в единичное состояние, вследствие чего на вход значения переноса сумматора 4 в первом такте поступает единичный сигнал, этот ко далее преобразуется в дополнительны в результате на выходе суммы 23 сум матора 4 в пределах цикла последова тельно формируется значение разност между эталонным и селектируемым сигналами. При этом значение перено са в следующий разряд записывается каждом такте в триггер 6 благодаря подаче на его управляющие входы сиг нала с выхода 24 переноса сумматора 4 и подаче на его счетный вход такт вых сигналов с шины 3. В процессе формирования значения разности на выходе 23 сумматора 4 возможны следующие ситуации. Селектируемый сигнал меньше эталонного сигнала. В этом случае на выходе 23 сумматора разность формируется в прямом коде, а к последнему такту триггер 6 оказывается в состоянии, при котором на его прямом выходе присутствует единичный сигнал. Если при этом величина модуля разности оказывается меньше допустимой, в тактах, следующих за п-м, единичные сигналы на выходе 23 сумматора не возникают и триггер 7 к концу цикла остается в состоянии, при котором на его инверсном выходе присутствует нулевой сигнал, удерживающий элемент И 14 в закрытом состоянии, и на последнем такте ника кие сигналы на вход 25 дискриминатора не поступают. Если величина модуля разности оказывается больше допустимой, в тактах, следующих за п-м, возникает хотя бы один единичный сигнал на выходе 23 сумматора 4, триггер 7 перебрасывается, открывая элемент И 14, ив последнем такте возникает сигнал на выходе 25 дискриминатора. Селектируемый сигнал больше эталонного сигнала. В этом случае на выходе 23 сумматора разность формируется в дополнительном коде, а к последнему такту триггер 6 оказывается в состоянии, при котором на его инверсном выхода присутствует единичный сигнал. Если при этом величина модуля разности оказывается больше допустимой, в тактах следующих за n-Ni, на выходе 23 сумматора 4 возникаетхотя бы один нулевой сигнал, преобразуемый в единичный элементом НЕ 11, триггер 8 перебрасывается, открывая через элемент ИЛИ 1 элемент И 15, и на выходе 25 дискриминатора в последнем такте возникает сигнал. Если величина модуля разности оказывается меньше допустимой, в тактах, следующих за п-м, нулевые сигналы на выходе 23 сумматора 4 не возникают и триггер 8 к концу цикла остается в состоянии, при котором на его инверсном выходе присутствует нулевой сигнал. Если же, однако, в пределах первых тактов на выходе 23 сумматора возникают одни нулевые сигналы, они не изменяют состояния триггера 9, в результате чего к концу такта на его приемном выходе сохранится еди- , ничный сигнал, что также приводит к отпиранию элемента И 15 и появлению сигнала на выходе 25 дискриминатора. Если же в пределах этих тактов на выходе 23 сумматора 4 возникает хотя бы один единичный

сигнал, триггер 9 перебрасывается, на его прямом выходе к концу такта оказывается нулевой сигнал который на результат анализа не влияет. Выполняемая с помощью триггера 9 операция эквивалентна операции восстановления прямого кода разности для этого единственного ее значения (когда в младших разрядах дополнительного кода разности содержатся одни нули, а во всех старших разрядах - одни единицы}.

Таким образом, предложенный дискриминатор позволяет си &1етрировать поле допустимых отклонений селектируемого сигнала относительно эталонного и, следовательно, повысить точность его работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой амплитудный дискриминатор | 1973 |

|

SU532858A1 |

| Устройство для считывания графической информации | 1984 |

|

SU1182553A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

ЦИФРОВОЙ АМПЛИТУДНЫЙ ДИСКРИМИНАТОР, содержащий распределитель импульсов, три триггера, три элемента НЕ, четыре элемента И, сумматор, один из входов которого соединен с шиной эталонных сигналов дискриминатора, другой через первый элемент НЕ - с шиной селектируемого сигнала дискриминатора, а третий - с прямым выходом первого триггера, выход переноса сумматора подключен к входу установки в нулевое состояние и через второй элемент НЕ к входу установки в единичное состояние первого триггера, счетный вход которого соединен с шиной тактовых сигналов дискриминатора, выход сигнала считывания распределителя сигналов соединен с первыми входами первого и второго элементов И, вторые входы которых подключены соответственно к прямому и инверсному выходам первого триггера, выход начальной установки распределителя сигналов соединен с входами установки в единичное состояние первого, второго и третьего триггеров, выход блокировки распределителя сигналов соединен с первыми входами третьего и четвертого элементов И, вторые входы которых подключены к шине тактовых сигналов дискриминатора, выход суммы сумматора соединен с третьими входами третьего и через третий элемент НЕ четвертого элемента И, выходы которых подключены к входам установки в О соответственно второго и третьего триггеров, инверсный выход второго триггера соединен с третьим входом первого элемента И, выход которого подключен к выходу второго элемента И и выходной шине дискриминатора, отличающийся тем, что, с целью повышения точности дискриминатора путем устранения несимметричности селекции сигналов (Л относительно эталонного путем полного восстановления модуля разности с при отрицательном значении разности, в него введены четвертые триггер и элемент НЕ, пятый элемент И и элемент ИЛИ, входы которого соединены с инверсным и прямыми выходами соответственно третьего и четвертого, триггеров, а выход - с третьим входом второго элемента И, вход устасо новки в единичное состояние четвертого триггера подключен к выходу -4 начальной установки распределителя о: сигналов, а вход установки в О с.выходом пятого элемента И,входы со которого соединены соответственно с шиной тактовых сигналов дискриминатора, выходом суммы сумматора и через четвертый элемент НЕ с выходом блокировки распределителя сигналов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3811039, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой амплитудный дискриминатор | 1973 |

|

SU532858A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1984-02-15—Публикация

1982-10-04—Подача