1

Изобретение отиосится к облаети вычислительной техники, в частности к устройствам для приема и передачи данных, и может быть использовано для построения гг-кратно резервированных систем передачи данных.

Известна дублированная система для приема и передачи данных, содержащая процессоры, коммутаторы и адаптеры. В этой системе процедура идентификации сигнала обращения адаптера к нроцессорам выполняется на основе использования межпроцессорного обмена или специального сравнивающего устройства.

Если процесс идентификации прощел неудовлетворительно, то процессоры должны выполнить либо повторное обращение к адаптерам, либо переходить в состояние диагностики, причем и то и другое требует программных затрат и значительного процессорного времени, что снижает производительность системы. Из-за значительных временных затрат на выполнение повторного обращения к адаптерам количество этих обращений может быть недостаточным, чтобы отделить отказовую ситуацию от нармальной, но связанной с текущим процессором выставления требования. В таком случае часто вызывается диагностическая программа в нормально функционирующей системе. Это является серьезным недостатком подобных систем.

Известна также дублированная си1 хронная система для приема и передачи данных, содержащая первый и второй процессоры связи, запросные входы которых соединены с запросными выходами блоков коммутации соответственно первой и второй групп, пнформационный и синхронизирующий выходы г-го блока кo iмyтaциII (i 2,...,n) первой, второй групп соединены с первымн информациоинымп и синхронизирующпми входами (;-1)-го блока коммутацпп соответственно первой и второй групп, запускающий выход г-го коммутации (,..., п-1) первой, второй групп соедипен с запускающим входом (()-го блока коммутации (,..., п-1) соответственно первой и второй групп, ииформационный вход первого и второго процессоров связи соединен с информационным выходом первого блока коммутации соответственно первой и второй групп, блоки сопряжения с каналами связи, первый и второй информационные выходы, первый и второй синхронизирующие выходы ;-го (,..., п) блока сопряжения с каналами связи соединены соответствеюш с вторым информационными и симхро11изирующимп входами /-х блоков коммутации (i 1,..., п) соответственно первой и Btopoii групп блоков коммутации. Первый и BTopoii запускающие входы г-го (i ,..., п) блока сопряжения с каналами связп соединены с вторыми запускающими выходами I-x (,..., п) блоков коммутации соответственно первой и ; торой групп, а группа входов - выходов каждого блока сопряжепия с каналами связи соединепа с соответствующей группой входов - выходов внещнего устройства.

Оба процессора имеют одпи и те же программы, которые выполняются приближенно синхронно, и выходная информация во внещние устройства выдается с частотой прерывания программ в фиксированные интервалы времени. В соответствии с обращением процессоров к заданному внещнему устройству последнее выдает в процессор и в устройство сравнения сигнал подтверждения принятого обращения. Сравнивающее устройство производит логическое сравнение принятых ответов. Если ответы не совпадают, то устройство сообщает об этом процессорам, которые в свою очередь организуют повторное обращение к внешнему устройству в том же такте прерывания (сканирования).

Известная система имеет ряд существенных недостатков. Наличие общего для дублированной системы устройства влечет за собой либо появление слабого звена в системе (если общее недублированное устройство выполнено на элементах той же надежности, что и другие устройства системы), либо для обеспечения требований по надежности необходимо значительное усложение сравнивающего устройства и связанных с ним устройств, а соответственно и увеличение аппаратуры. Введение третьей неунифицированной магистрали управления внещними устройствами со стороны устройства сравнения создает дополнительные неудобства в эксплуатации системы. Организация повторного обращения к внешним устройствам процессором снижает производительность системы в целом как из-за значительной продолжительности самой организации повторного обращения (многозвенная обратная связь внещнее устройство - процессор), так и из-за того, что это повторение выполняет сам процессор. Процедура установления отказовой ситуации при работе с внещними устройствами в программном плане является достаточно сложной.

Цель изобретения - повышение пропускной способности системы и сокращение оборудования путем упрощения идентификации синхронности параллельно работающих цроцессоров и выявления отказовой ситуации в случае нецодключения одного процессора к требуемому адаптеру, снижение нрограммных затрат, связанных с организацией обращения процессоров к адаптерам и диагностикой в случае установления неодноименного подключения их к последним.

Это достигается тем, что предлагаемая система содержит первый и второй блоки анализа возможности сеанса связи, причем синхронизирующий, сигнальный и информационный входы первого и второго блоков анализа возможности сеанса связи соединены с синхронизирующим, сигнальным и информационным выходами первого блока коммутации соответственно первой и второй групп, синхро.низирующий и сигнальный выходы первого и второго блоков анализа возможности сеанса связи соединены с синхронизирующим и сигнальным входами соответственно первого и второго нродессоров связи. Занускающие выходы первого и второго процессоров связи соединены с запускающими входами соответственно первого и второго блоков анализа возможности сеанса связи, запускающие выходы которых соединены с запускающими входами нервых блоков коммутации соответственно первой и

второй групп. Сигнальные выходы t-x (i 2,..., п) блоков коммутации первой и второй групп соединены с первыми сигнальными входами (i-1)-х (i 2,..., п) блоков коммутации соответственно нервой и второй групп. Сигнальные выходы i-го (,..., п) блока сопряжения с каналами связи соединены с вторыми

сигнальными входами г-х ,п) блоков

коммутации соответственно первой и второй групп.

,

Ьлок сопряжения с каналами связи содержит узел формирования признака неподключения процессора связи, первый, второй входы и первый, второй выходы которого соединены соответственно с первым, вторым запускающими входами и первым, вторым сигнальными выходами блока.

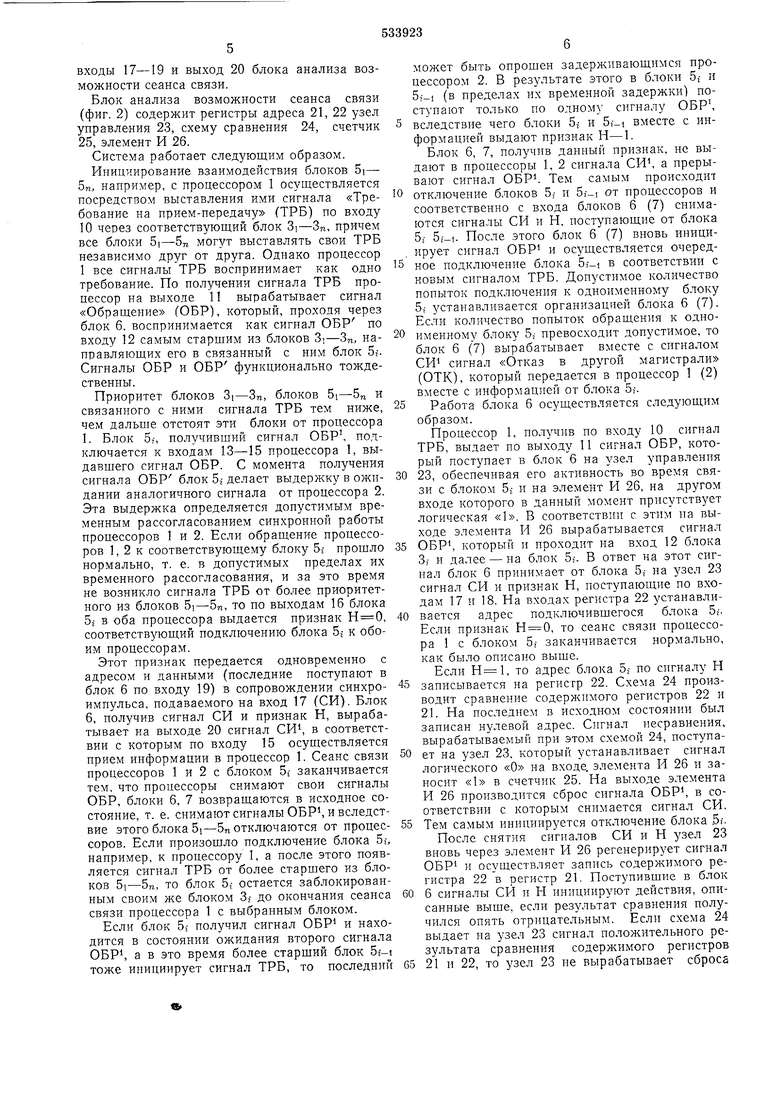

Блок анализа возможности сеанса связи содержит узел управления, элемент И, счетчик, первый и второй регистры, схему сравнения,

причем выходы узла управления с первого по пятый соединены соответственно с синхронизирующим и сигнальным выходами блока, с входом счетчика, с первыми входами первого регистра и элемента И. Входы узла управления с первого по пятый соединены соответственно с запускающим входом блока, с выходами счетчика и схемы сравнения, с синхронизирующим и сигнальным входами блока. Входы схемы сравнения соединены с выходом

первого и первым выходом второго регистров, второй выход второго регистра соединен с вторым входом первого регистра, запускающий выход, сигнальный, информационный н запускающий входы блока

соединены соответственно с выходом элемента И, с первым и вторым входами второго регистра и с вторым входом элемента И.

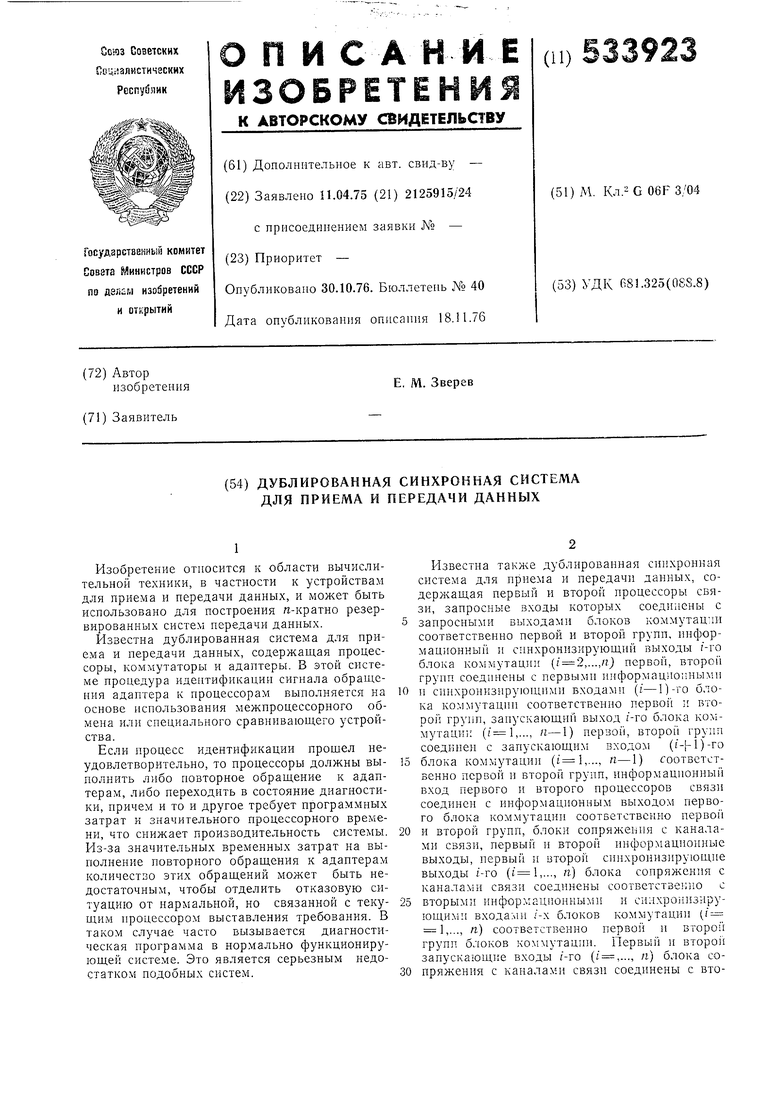

На фиг. 1 представлена блок-схема системы; на фиг. 2 - схема блока анализа возможности сеанса связи.

Схема содержит (фиг. 1), процессоры связи 1, 2, блоки коммутации 3i-Зп, 4i-4п, блоки сопряжения с каналами связи, блоки 6, 7 анализа возможности сеанса связи, первую и вторую группы 8, 9 блоков коммутации, запросный вход 10 процессора, выход 11 процессора, вход 12 блока коммутации, входы 13- 15 соответственно синхронизирующий, сигнальный и информационный процессора, выходы 16 блока сопряжения с каналами связи.

входы 17-19 и выход 20 блока анализа возможности сеанса связи.

Блок анализа возможности сеанса связи (фиг. 2) содержит регистры адреса 21, 22 узел управления 23, схему сравнения 24, счетчик 25, элемент И 26.

Система работает следующим образом.

Инициирование взаимодействия блоков 5i- 5п, например, с процессором 1 осуществляется посредством выставления ими сигнала «Требование на прием-передачу (ТРБ) по входу 10 через соответствующий блок 3i-Зп, причем все блоки 5|-5„ могут выставлять свои ТРБ независимо друг от друга. Однако процессор 1 все сигналы ТРБ воспринимает как одно требование. По получении сигнала ТРБ процессор на выходе 11 вырабатывает сигнал «Обращение (ОБР), который, проходя через блок 6. воспринимается как сигнал ОБР по входу 12 самым старшим из блоков 3i-Зп, направляющих его в связанный с ним блок 5,. Сигналы ОБР и ОБР функционально тождественны.

Приоритет блоков 3i-Зп, блоков 5i-5п и связанного с ними сигнала ТРБ тем ниже, чем дальше отстоят эти блоки от процессора I. Блок 5,-, получивший сигнал ОБР , подключается к входам 13-15 процессора 1, выдавшего сигнал ОБР. С момента получения сигнала ОБР блок 5 делает выдержку в ожидании аналогичного сигнала от процессора 2. Эта выдержка определяется допустимым временным рассогласованием синхронной работы процессоров 1 и 2. Если обращение процессоров 1, 2 к соответствующему блоку 5г прошло нормально, т. е. в допустимых пределах их временного рассогласования, и за это время не возникло сигнала ТРБ от более приоритетного из блоков 5i-5п, то по выходам 16 блока 5г в оба процессора выдается признак , соответствующий подключению блока 5i к обоим процессорам.

Этот признак передается одновременно с адресом и данными (последние поступают в блок 6 по входу 19) в сопровождении синхроимпульса, подаваемого на вход 17 (СИ). Блок 6, получив сигнал СИ и признак Н, вырабатывает на выходе 20 сигнал СИ, в соответствии с которым по входу 15 осуществляется прием информации в процессор 1. Сеанс связи процессоров 1 и 2 с блоком 5i заканчивается тем. что процессоры снимают свои сигналы ОБР, блоки 6, 7 возвращаются в исходное состояние, т. е. снимают сигналы ОБР , и вследствие этого блока отключаются от процессоров. Если произощло подключение блока 5г, например, к процессору 1, а после этого появляется сигнал ТРБ от более старшего из блоков 5i-5п, то блок 5t остается заблокированным своим же блоком 3,- до окончания сеанса связи процессора 1 с выбранным блоком.

Если блок 5; получил сигнал ОБР и находится в состоянии ожидания второго сигнала ОБР а в это время более старший блок Si-i тоже инициирует сигнал ТРБ, то последний

может быть опрощен задерживающимся процессором 2. В результате этого в блоки 5; и 5, (в пределах их временной задержки) поступают TOvibKo по одному сигналу ОБР ,

вследствие чего блоки 5, и вместе с информацией выдают признак Н-1.

Блок 6, 7, получив данный признак, не выдают в процессоры 1, 2 сигнала CW, а прерывают сигнал ОБРЧ Тем самым происходит

отключение блоков 5,- и 5, от процессоров и соответственно с входа блоков б (7) снимаются сигналы СИ и П, поступающие от блока 5; . После этого блок 6 (7) вновь инициирует сигнал ОБР1 и осуществляется очередное подключение блока 5;-i в соответствии с новым сигналом ТРБ. Допустимое количество попыток подключения к одноименному блоку 5,; устанавливается организацией блока 6 (7). Если количество попыток обращения к одноименному блоку 5,; превосходит допустимое, то блок 6 (7) вырабатывает вместе с сигналом СИ сигнал «Отказ в другой магистрали (ОТК), который передается в процессор 1 (2) вместе с информацией от блока Бг.

Работа блока 6 осуществляется следующим образом.

Процессор 1, получив по входу 10 сигпал ТРБ, выдает по выходу 11 сигнал ОБР, который поступает в блок 6 на узел управления

23, обеспечивая его активность во время связи с блоком 5,: и на элемент И 26, на другом входе которого в данный момент присутствует логическая «1. В соответствии с этим на выходе элемента И 26 вырабатывается сигнал

ОБР, который и проходит на вход 12 блока 3,- и далее - на блок Б,-. В ответ на этот сигнал блок 6 принимает от блока 5,- на узел 23 сигнал СИ и признак П, поступающие по входам 17 и 18. На входах регистра 22 устанавливается адрес подключившегося блока БгЕсли признак Н 0, то сеанс связи процессора 1 с блоком Б,- заканчивается нормально, как было описано выше. Если , то адрес блока Б; по сигналу Н

записывается на регистр 22. Схема 24 производит сравнение содержимого регистров 22 и 21. На последнем в исходном состоянии был записан нулевой адрес. Сигнал несравнения, вырабатываемый при этом схемой 24, поступает на узел 23, который устанавливает сигнал логического «О на входе, элемента И 26 и заносит «1 в счетчик 25. На выходе элемента И 26 производится сброс сигнала ОБР, в соответствии с которым снимается сигнал СИ.

Тем самым инициируется отключение блока .Б;. После снятия сигналов СИ и Н узел 23 вновь через элемент И 26 регенерирует сигнал ОБР и осуществляет запись содержимого регистра 22 в регистр 21. Поступившие в блок

6 сигналы СИ и Н инициируют действия, описанные выше, если результат сравнения нолучился опять отрицательным. Если схема 24 выдает на узел 23 сигнал положительного результата сравнения содержимого регистров

21 и 22, то узел 23 не вырабатывает сброса

сигнала ОБР , а выдает па входы 13, 14 про/leccopa сигналы СИ и ОТК, после чего процессор 1 осуществляет иормальпое завершеине сеанса связи с блоком 5, и выполняет дейетпня г, соответствии с сигиалом ОТК. Сигнал ОТК вырабатывается узлом 23 и в случае переполнения сметчика 25, фиксирующего количество попыток подключения процессора 1 к блоку 5;-. Разрядность счетчика определяется в соответствии с установленным количеством попыток обран1;ения.

Если время фиксации отказовой ситуации НС является жестко лимитированным, но ее выявление возлагается на аппаратуру с наименьшим содержанием оборудования, то в блок 6 могут не входить региетры 21 и 22 н схе.ма сравнения 24. В этом случае сигнал ОТК вырабатывается узлом управления 23 только по переполнении счетчика 25.

В случае, если отказ, т. е. ненодключенне нроцессора 2 в теченне заданного времени (от момента начала выдачи сигнала ОБР до ожидаемого момента получения сигнала СИ ), формируется в нронессоре, то блок 6 может состоять только из элемента И 26 и узла унравлення 23.

Физическая реализация дублированной синхронной системы для приема передачи данных может предусматривать выполнение блока б либо отдельным конструктивом (фиг. 1), либо включенным в состав процессора 1 блоком коммутации 3.

В известной систе.ме приема и передачи данных время сеанса связи нроцессора с внешним устройством складывается из времени полного цикла взаимодействия нроцессора н времени ндентифнкации запросов внешнего устройства. Последняя составляющая имеет значение 3-30 мксек.

Время идентификации запросов в системе равно задержке на двух логических элементах узла формирования признака неподключеиня нроцессора. (10 иеек).

Блок анализа сеанса связи вносит дополнительную задержку во временной цикл нормального взаимодействия процеееора с внешним устройством (ВУ) примерно на 10 нсек (задержка на двух логических элементах).

В случае первоначального подключения процессоров к разным ВУ (блоки ) интерфейе с цени «блок анализа возможности сеанса связи - блок коммутатиш - блок сопряжения с каналом связи отбрасывается не полностью, а ограничивается обменом только одной серией импульсов. Это позволяет сократить вре.менной цикл сеанса связи в ненормаль 1ОЙ ситуации но отношению к нормальной примерно в 3-6 раз.

Таким образом, при нормальном подключении прон,ессоров к внешнему устройству время ндеитификацин обращений процеесоров к внешнему устройству в предлагаемой системе но сравнению с известной системой сокращается в 1,5-10 -15-10- раз. При периоде ностунлення запросов 100 мксек н вероятности

появления моментов подключения процессоров к разным внешни.м устройствам, ршнюй 10, производительность процессоров в системе увеличивается до 30%. При этом отпадает необходимость исиользования дополнительного оборудования межпроцессорного взаимодействия.

Формула и 3 о б р е т е н н я

I. Дублированная синхронная система для нриема и передачи данных, содержащая первый и второй процессоры связи, запросные входы которых соединены с заироснымн выходами блоков коммутации соответственно первой и второй групп, информационный и еинхронизирующий выходы г-го блока коммутации (,..., п) нервой, второй групп соединены с первыми информационными и снихроиизирующими входами (/-1)-го блока ко.ммутации соответственно нервой н второй групп, запускающий выход i-ro блока коммутации (/,..., п-1) первой, второй групп соединен с запускаюшим входом ()-го

блока коммутацпп (г 1,..., п-I) соответственно первой и второй групи, информациои-иый вход первого и второго процессоров связи соединен с информационным выходом первого блока коммутации соответственно первой и второй грунн, блоки сопряжения е каналами связи, первый и второй информационные выходы, первый и второй синхронизирующие выходы г-го (,..., п) блока сопряжения е каналами связи соединены соответственно с вторыми информационными и синхронизирующими входами /-Х (,..., п) блоков коммутации соответственно первой и второй групп блоков коммутации, первый и второй запускающие входы 1-го (,..., п) блока сопряжеиия с каналами связи соединены с вторыми запускающими выходами i-x (,..., п) блоков коммутации соответственно первой и второй групп, а грунпа входов - выходов каждого блока еопряжения с каналами связи соединена с соответствующей группой входов - выходов внешного устройства, отличающаяся тем, что, с нелью повышения пропускной способности системы и сокращения оборудования, система содержит первый и второй блоки анализа возможности сеанса связи, причем синхронизирующий, сигнальный н информационный входы первого и второго блоков анализа возможности сеанса связи соединены с снихронизируюпиш, сигнальным и информационным выходами нервого блока коммутации соответственцо первой и второй групп, синхронизирующий и сигнальпый выходы первого и второго блоков анализа возможности сеанса связи соединены с синхронизирующим и сигнальным входа.ми соответственно первого и второго процессоров связи, запускающие выходы первого и второго процессоров связи соединены с запускающими входами соответственно нервого и второго блоков анализа возможности сеанса

связи, заиускающие выходы которых соединены с запускающими входами первых блоков коммутации соответственно первой и второй групп, сигнальные выходы i-x (г 2,..., п) блоков коммутации первой и второй групп соединены с первыми сигнальными входами (i-1)-х (г 2,..., п) блоков коммутации соответствецно первой и второй групп, первый и второй сигнальные выходы 1-го (,..., л) блока сопряжения с каналами связи соединены с вторыми сигнальными входами г-х (/ 1,..., «) блоков коммутации соответственно первой и второй груцц.

2.Система по п. 1, отличающаяся тем, что блок сопряжения с каналами связи содержит узел формирования признака неподключенпя процессора связи, первый, второй входы и первый, второй выходы которого соединены соответственно с первым, вторым запускающими входами и первым, вторым сигнальными выходами блока.

3.Система по п. 1, отличающаяся тем.

что блок апализа возможности сеанса связи содержит узел управления, элемент И, счетчик, первый и второй регистры, схему сравнения, причем выходы узла управления с первого по пятый соединены соответственно с синхронизирующим и сигнальным выходами блока, с входом счетчика, с первыми входами первого регистра и элемента И, входы узла управления с первого по пятый соединены соответственно с запускающим входом блока, с выходами счетчика и схемы сравнения, с синхронизирующим и сигнальным входами блока, входы схемы сравнения соединены с выходом первого и первым выходом второго регистров,

второй выход второго регистра соединен с вторым входом первого регистра, запускаюгций выход сигнальный, информационный и запзскающий входы блока соединены соответственно с выходом элемента И, с первым и

вторым входами второго регистра и с вторым входом элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Устройство для сопряжения канала ввода-вывода с внешними устройствами | 1980 |

|

SU955017A1 |

| Устройство для сопряжения процессоров с внешними абонентами | 1978 |

|

SU750472A1 |

| Устройство для сопряжения | 1987 |

|

SU1458875A2 |

| Устройство для сопряжения процессоров с каналами ввода-вывода | 1975 |

|

SU526881A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

| Устройство для сопряжения | 1983 |

|

SU1115044A1 |

| Устройство для сопряжения | 1982 |

|

SU1056177A2 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

I-

ГР

IJ-и

Vj

м

26

L.

/

/7

/г

-

ll

. 2

22

ZD

IE

/

fue.2

Авторы

Даты

1976-10-30—Публикация

1975-04-11—Подача