1

Изобретение относится к области вычислительной техники, в частности к устройствам сопряжения нроцессоров и каналов, и может быть использовано при построении многопроцессорных вычислительных систем с общим парком каналов.

Известно устройство для сопряжения каналов ввода-вывода и процессора, содержащее блок обработки запросов и приоритета, блок приема команды и организации прерывания, блок фиксации ситуации и тестов локализации неисправностей 1.

Недостатком известного устройства является невозможность работы каналов ввода-вывода более, чем с одним нроцессором, что приводит к сужению функциональных возможностей устройства.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство, содержащее блок связи с каналами, первый и второй блок связи с процессорами, причем первая, вторая и третья группа входов-выходов устройства соединены соответственно с группой входов-выходов блока связи с каналами, с группами входов-выходов соответствеиио первого и второго блоков связи с процессорами, первый, второй и третий входы первого и второго блоков связи с процессорами соединены соответственно с первым, вторым и третьим выходами блока

связи с каналами, четвертый н пятый выходы которого соединены с четвертыми входами соответственно первого и второго блоков связи с процессорами, первый и второй входы блока связи с каналами соединены с первыми выходами соответственно первого и второго блоков связи с процессорами, третий и четвертый входы блока связи с каналами соединены со вторыми выходами соответственно первого и второго блоков связи с процессорами 2.

Недостатком известного устройства являются ограниченные функциональные возможности, обусловленные тем, что устройство не обеспечивает возможности одновременной работы нескольких каналов ввода-вывода с несколькими центральными процессорами.

Цель изобретения - расширение функциональных возможностей устройства без введения дополнительных команд.

Поставленная цель достигается тем, что устройство содержит дополнительные блоки связи с процессорами, причем пятые входы всех блоков связи с процессорами соединены с щестым выходом блока связи с каналами, иервый, второй, третий выходы которого соединены соответствеино с первыми, вторыми, третьими входами дополнительных блоков связи с процессорами, первые и вторые выходы которых соединены соответственно с первой и второй группами входов блока связи

с каналами, группы выходов которого соедине i;-i с четвертыми ьчодями допо.ишпч-льпых бло1(;и спязн с процессорами, а группы входов-выходов этих блоков соедплсны с cooi icrствуюгцими группами входов устройства.

В устройстве блок связи с каналами содержит регистр адреса, регистр информации, узел синхронизации и ириоритета, узлы выдачи инструкций, сигналов прерывания, формирования кода условия и ассоциативную память, причем с первого по пятый входы группы входов-выходов блока соединены с первыми входами соответственно узла сигналов прерывания, узла выдачи инструкций, узла синхронизации и приоритета, регистров информации и адреса, первый и второй выходы группы входов-выходов блока соединены с первыми выходами соответственно узла выдачи инструкций и регистр информации, .выходы регистра адреса, узла выдачи инструкций, узла сигналов прерывания, узла фор лирования кода условия соединены соответственно с первым, вторым, третьим и шестым выходами блока, четвертый и пятый выходы и группа выходов которого соединены с выходами узла сипхронизации и приоритета, первый, второй входы и первая группа входов блока соединены с группой входов регистра информации, третий, четвертый входы и вторая группа входов соединены с группой входов узла выдачи инструкций, второй вход, первый и второй выходы узла синхронизации и приоритета соединены соответственно со вторым выходом регистра информации, со вторыми входами регистра ииформации и регистра адреса, вторые вход и выход узла выдачи инструкций соединены с первыми выходами и входом ассоциативной памяти, вторые вход и выход которой соединены соответственно с первым и со вторым входами узла сигналов прерывания.

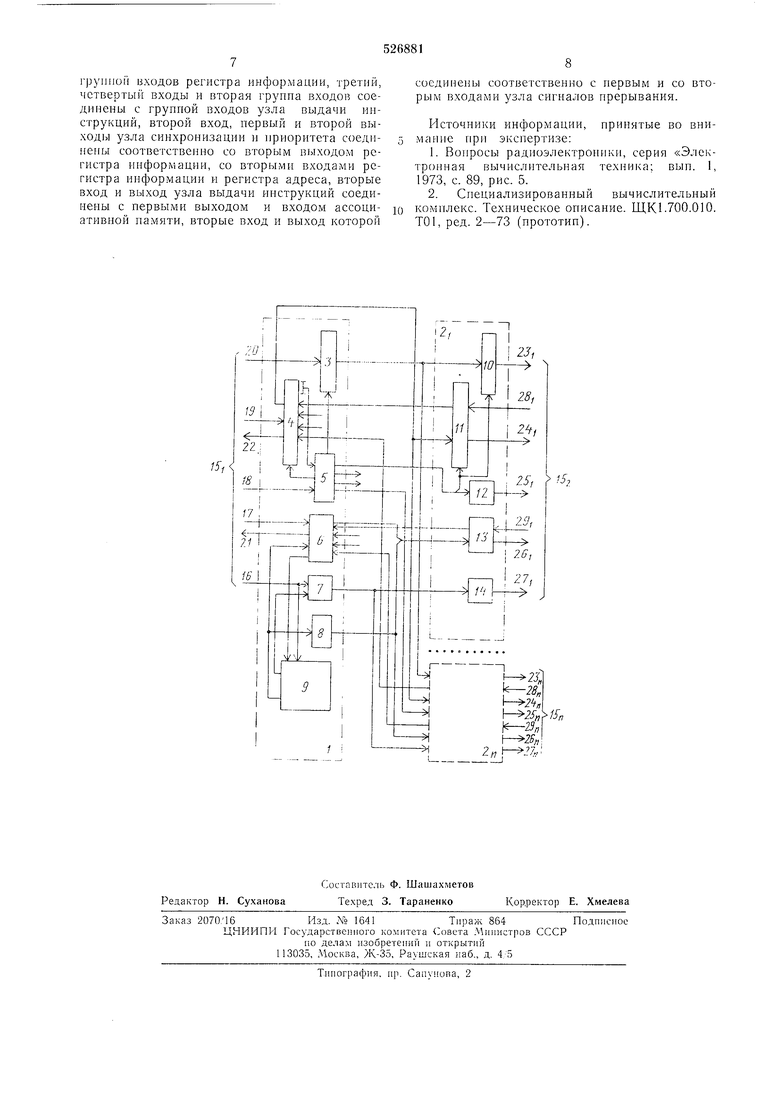

На чертеже представлена блок-схема устройства.

Устройство для сопряжения процессоров с каналами ввода-вывода содержит блок 1 связи с каналами, блока связи с процессорами, регистр 3 адреса, регистр 4 информации, узел 5 синхронизации и приоритета, узел 6 выдачи инструкций, узел 7 сигналов прерывания, узел 8 формирования кода условия, ассоциативную память 9, процессорный регистр 10 адреса, процессорный регистр И информации, узел 12 синхронизации обмена, узел 13 приема инструкций, узел 14 выдачи сигналов прерывания группы входов-выходов устройства, входы 16-20 (с первого по пятый соответственно) первой группы входов-выходов устройства, первый 21 и второй 22 выходы первой группы входов-выходов устройства, выходы 23i-23„, 24i-24„, 25i-25„, 26i-26n, соответствующих групп входов-выходов устройства, входы 28i-1 п, 29i-29 соответствующих групп входов-выходов устройства.

Устройство для сопряжения процессоров с

каналами ввода-вывода работает следующим oopaacjM.

К лрулпе 15 IB ходов-выходов ссройстиа юдключаются каналы ввода-вывода (мультиплексные и селекторные). Параллельная работа этих каналов обеспечивается за счет стандартных аппаратных средств (схемы приоритетов), имеющихся в каналах.

К блокам 2)-2„, количество которых соответствует числу центральных процессоров, через группы 152-157i подключаются центральные процессоры со своей оперативной намятью. Работа нескольких центральных процессоров с устройством сопряжения обеспечивается средствами коммутации и приоритетов, закладываемыми в устройство сопряжения.

Поступившая по входу 29 от центрального процессора инструкция фиксируется узлом 13 приема инструкций. При отсутствии инструкций в узлах 13 д;ругих блоков 1ч-In с более высоким приоритетом инструкция передается в узел 6 выдачи инструкции блока 1 связи с каналами. По адресу канала и виещнего устройства, содержащихся в инструкции, следует

5 обращение в память 9. Если в памяти 9 есть зафиксированный при использовании предыдущей инструкции признак, что требуемое внешнее устройство занято, в приславший инструкцию центральный процессор выдается

0 код уловия «занято через узел 8 формирования кода условия и узел 13 на ВЕЛХОД 26i. В памяти 9 фиксируется признак обращения к этому внешнему устройству. В случае, если в памяти 9 нет признака занятости адресуемого

5 внешнего устройства, инструкция из узла б пересылается на выход 21 и далее каналу. Полученный из канала по входу 17 код условия через узел 6 и ззел 13 соответствующего блока 2|.-2и связи с процессором, приславшим инструкцию, передается на выход 26i и далее этому процессору.

При необходимости чтения информации из центральной оперативной памяти адрес ячейки с входа 20 поступает в регистр 3 адреса

5 ячейки центральной оперативной памяти, а запрос с входа 18 поступает в узел 5 синхронизации и выдачи запроса обращения к центральной оперативной памяти. В зависимости от значения старших разрядов адреса ячейки этот адрес направляется на выходной регистр 10 адреса ячейки центральной оперативной памяти, а запрос - в узел 12 синхронизации обмена с центральной оперативной памятью соответствующего блока 2i-2n связи с процессором. Далее адрес выдается па выход 23. Выбранная информация с входа- принимается на регистр П, далее на канальный регистр 4 и выход 22 информации.

При необходимости записи информации в

0 центральную оперативную память адрес ячейки с входа 20 поступает в регистр 3, инфор мация с входа 19 - в регистр 4, запрос с входа 18 - в узел 5. В зависимости от значения старших разрядов адреса адрес ячейки, информация и запрос направляются соответственно на регистры 10, 11 и узел 12 блока 2i и далее на выходы 23i, 24ь 25i. После фиксации адреса информации регистры 3, 4 и узел 5 готовы для приема следующего запроса.

Если внешнее устройство имеет возможность выдавать инициативные прерывания, необходимо предварительно по инструкции, например «проверить ввод-вывод в памяти 9, зафиксировать признак обращения к этому внешнему устройству от данного процессора. Выданные этим внешним устройством сигналы прерывания будут направляться тем нроцессорам, для которого в памяти 9 зафиксирован такой признак.

Признаки стираются в намяти 9 по инструкции «остановить ввод-вывод. Прн выдаче прерывания сигнал прерывания с входа 16 ноступает в узел 7 сигналов прерывания и в память 9. В намяти 9 определяется но адресу внешнего устройства какому (каким) процессору оно должно быть нанравлено. По сигналу из памяти 9 прерывание из узла 7 передается узлу 14 выдачи сигналов прерывания. Узел 14 выдает сигнал прерывания на выход 27i.

Устройство для сопряжения значительно расширяет функциональные возможности вычислительной системы, в состав которой оно входит. Устройство позволяет подключить каналы ввода-вывода (мультинлексные и селекторные) однопроцессорных вычислительных систем к несколькнм центральным нроцессорам. Прн этом обеснечивается возможность «одновременной (мультинлексной) работы нескольких центральных процессоров с несколькими каналами ввода-вывода и соответственно через них с любыми внешними устройствами, подключенным к этим каналам. Этим достигается возможность нолучения общего поля внешних устройств для нескольких центральных процессоров, повышенные характеристики вычислительной системы, оптимизации ее структуры и возможность лучшего распределения как внешних устройств, так и нроизводнтельности центральных вычислителей и системы в целом. Вышеуказанные возможности реализуются без доработки апнаратуры и введения специальных команд (доработки математического обеспечения) в стандартные каналы ввода-вывода и центральные процессоры однопроцессорных вычислительных систем (например ЕС ЭВМ), что является самым существенным достоинством нредлагаемого технического решения.

И так, нредлагаемое устройство расширяет функциональные возможности и нозволяет проектировать многопроцессорные вычислительные системы (в части подключения каналов ввода-вывода к нескольким центральным процессорам и создания общего поля виешннх устройств) из технических средств однопроцессорных вычислительных систем без доработки их (существующего) математического обеснечения.

6 Форм у л а изобретен и я

1.Устройство для сопряжения процессоров с каналами ввода-вывода, содержащее блок

связи с каналами, первый и второй блоки связи с процессорами, нричем первая, вторая и третья группы входов-выходов устройства соединены соответственно с грунной входов-выходов блока связи с каналами, с группами

входов-выходов соответственно первого и второго блоков связи с нроцессорами, первый, второй и третий входы первого и второго блоков связи € процессорами соединены соответственно € первым, вторым и третьим выхода;ми блока связи с каналами, четвертый и пятый выходы которого соединены с четвертыми входами соответственио иервого и второго |блоков связи с процессорами, первый и второй входы блока связи с каналами соединены с первыми выходами соответственно первого н второго блоков связи с процессорами, третий и четвертый входы блока связп с каналами соединены со вторыми выходами соответственно нервого и второго блоков связн с нроцессорамп, отличающееся тем, что, с целью расширения функциональных возможностей устройства, оно содержит дополннтельные блоки связи с процессорами, причем пятые входы всех блоков связи с нроцессорами соединены с шестым

выходом блока связи с каналами, нервый, второй н трет);и выходы которого соединены соответственно с первыми, вторыми и третьими 1 ходами до11олнител1 иых блоков связи с процессорами, первые и вторые выходы которых

соединены соответственно с первой и BTOpoii группами входов блока связи с каналами, группа выходов которого соединена с четвертыми входами дополнительных блоков связи с процессорами, а группы входов-выходов этих

блоков соединены с соответствующими группами входов устройства.

2.Устройство поп. 1, отличающееся тем, что блок связи с каналами содержит

регистр адреса, регистр информации, узел синхронизации и прпоритета, узлы выдачи инструкций, сигналов прерывания, формирование кода условия н асоциативную память, причем с первого по пятый входы группы входов-выходов блока соединены с первыми входами соответственно узла сигналов прерывания, узла выдачи нструкцнй, узла снн.хронизацин и прпор1ггета. регистров информации н адреса, первый и BTOpoii выходы группы входов-выходов блока соединены с первыми выходами соответственно узла выдачи инструкцнй и регистра ннформацни, выходы регистра адреса, узла выдачи инструкций, узла сигналов прерывания, узла формирования кода усЛОБНЯ соединены соответственно с первым, вторым, третьим и шестым выходами блока, четвертый и пятый выходы н грунна выходов которого соединены с выходами узла синхронизации и приоритета, первый, второй входы

и первая группа входов блока соединены с

группой входов регистра информации, третий, четвертый входы и вторая группа входов соединены с группой входов узла выдачи инструкций, второй вход, первый и второй выходы узла синхронизации и приоритета соединены соответствеино со вторым выходом регистра информации, со вторыми входами регистра ииформации и регистра адреса, вторые вход и выход узла выдачи инструкций соединены с первыми выходом и входом ассоциативной памяти, вторые вход и выход которой

соединены соответственно с первым и со

вторым входами узла сигналов прерывания.

Источники информации, принятые во внимание при экспертизе:

1.Вопросы радиоэлектроники, серия «Электронная вычислительная техника; вып. 1, 1973, с. 89, рис. 5.

2.Специализированный вычислительный комплекс. Техническое описание. 1ЦК1.700.010. Т01, ред. 2--73 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал многопроцессорной вычислительной системы | 1973 |

|

SU521559A1 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Устройство для обмена информацией | 1978 |

|

SU794630A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для связи процессора с устройствами ввода-вывода | 1973 |

|

SU495659A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

2,,

Авторы

Даты

1976-08-30—Публикация

1975-02-05—Подача