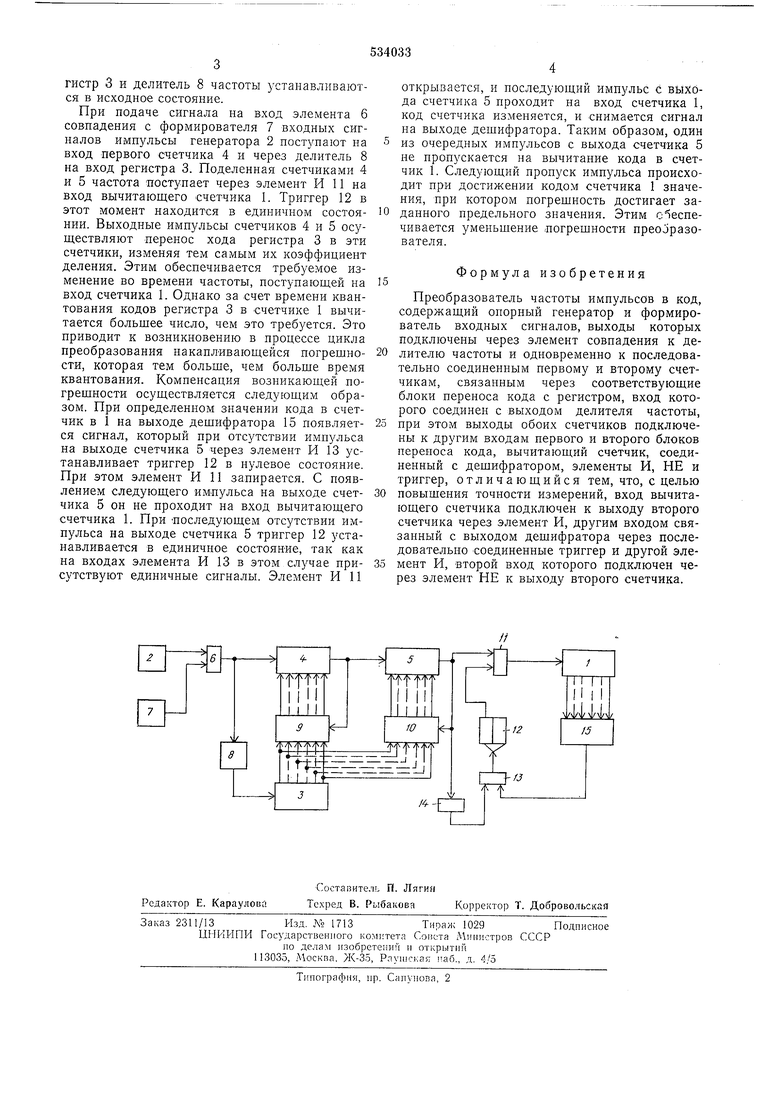

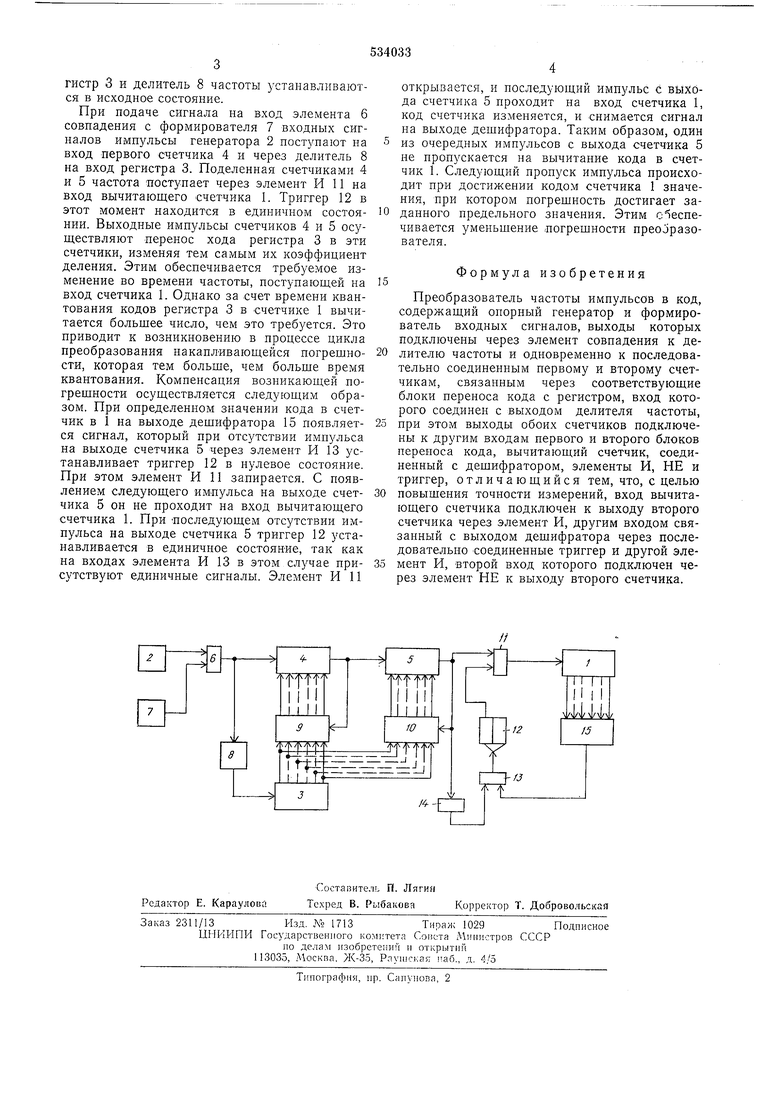

гистр 3 и делитель 8 частоты устанавливаются в исходное состояние.

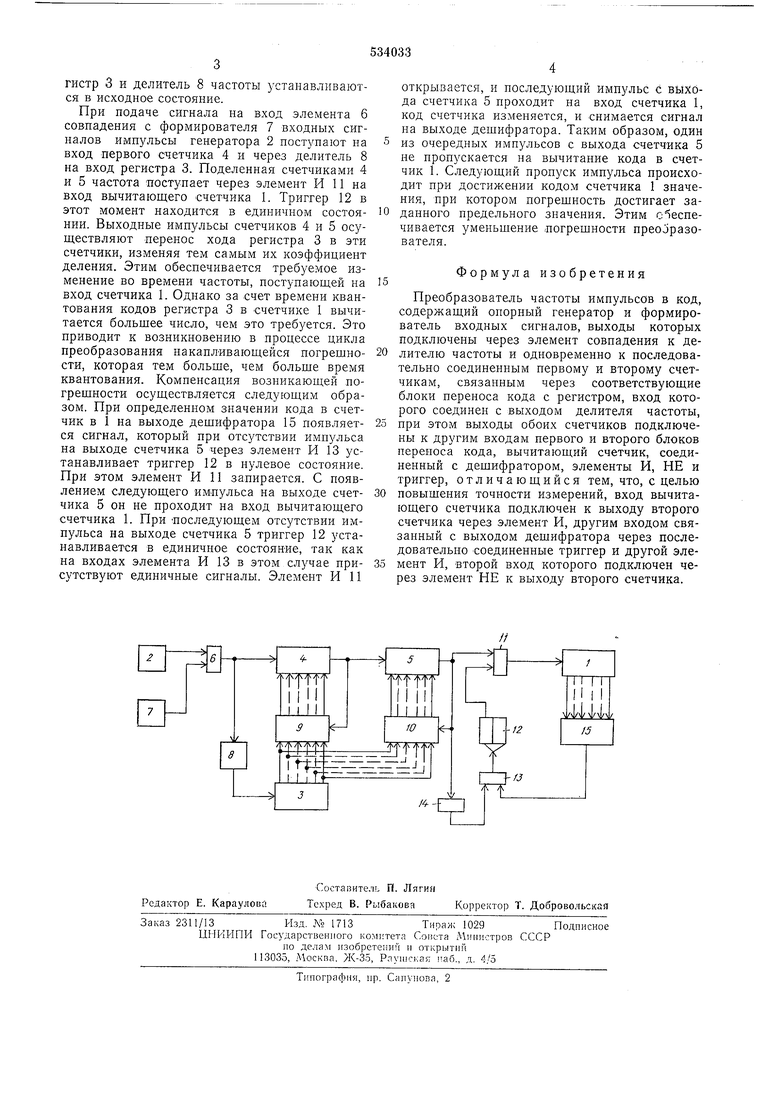

При подаче сигнала на вход элемента 6 совладения с формирователя 7 входных сигналов импульсы генератора 2 на вход первого счетчика 4 и через делитель 8 на вход регистра 3. Поделенная счетчиками 4 и 5 частота поступает через элемент И 11 на вход вычитающего счетчика 1. Триггер 12 в этот момент находится в единичном состоянии. Выходные импульсы счетчиков 4 и 5 осуществляют перенос хода регистра 3 в эти счетчики, изменяя тем самым их коэффициент деления. Этим обеспечивается требуемое изменение во времени частоты, поступающей на вход счетчика 1. Однако за счет времени квантования кодов регистра 3 в счетчике 1 вычитается большее число, чем это требзется. Это приводит к возникновению в процессе цикла преобразования пакапливающейся погрешности, которая тем больше, чем больше время квантования. Компенсация возникающей погрешности осуществляется следующим образом. При определенном значении кода в счетчик в 1 на выходе дешифратора 15 появляется сигнал, который при отсзтствии импульса на выходе счетчика 5 через элемент И 13 устанавливает триггер 12 в нулевое состояние. При этом элемент И И запирается. С появлением следующего импульса на выходе счетчика 5 он не проходит на вход вычитающего счетчика 1. При последующем отсутствии импульса на выходе счетчика 5 триггер 12 устанавливается в единичное состояние, так как на входах элемента И 13 в этом случае присутствуют единичные сигналы. Элемент И 11

открывается, и последующий импульс с выхода счетчика 5 проходит на вход счетчика 1, код счетчика изменяется, и снимается сигнал на выходе дешифратора. Таким образом, один

из очередных импульсов с выхода счетчика 5 не пропускается на вычитание кода в счетчик 1. Следующий пропуск импульса происходит при достижении кодом счетчика 1 значения, при котором погрешность достигает заданного предельного значения. Этим обеспечивается уменьшение погрешности преобразователя.

Формула изобретения

Преобразователь частоты импульсов в код, содержащий опорный генератор и формирователь входных сигналов, выходы которых подключены через элемент совпадения к делителю частоты и одновременно к последовательно соединенным первому и второму счетчикам, связанным через соответствующие блоки переноса кода с регистром, вход которого соединен с выходом делителя частоты,

при этом выходы обоих счетчиков подключены к другим входам первого и второго блоков переноса кода, вычитающий счетчик, соединенный с дешифратором, элементы И, НЕ и триггер, отличающийся тем, что, с целью

повышения точности измерений, вход вычитающего счетчика подключен к выходу второго счетчика через элемент И, другим входом связанный с выходом дешифратора через последовательно соединенные триггер и другой элемент И, второй вход которого подключен через элемент НЕ к выходу второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Способ измерения фазового сдвига между двумя гармоническими сигналами и устройство для его осуществления | 1988 |

|

SU1596272A1 |

| Преобразователь сдвига фазы в код скорости и ускорения | 1986 |

|

SU1358096A1 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

| Измеритель сдвига фаз (его варианты) | 1982 |

|

SU1040432A1 |

| Цифровой фазометр | 1984 |

|

SU1176264A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388989A2 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Измеритель переходных характеристик частотных прецизионных устройств | 1987 |

|

SU1620992A1 |

| Устройство для умножения частоты следования периодических импульсов | 1975 |

|

SU544112A2 |

Авторы

Даты

1976-10-30—Публикация

1974-10-25—Подача