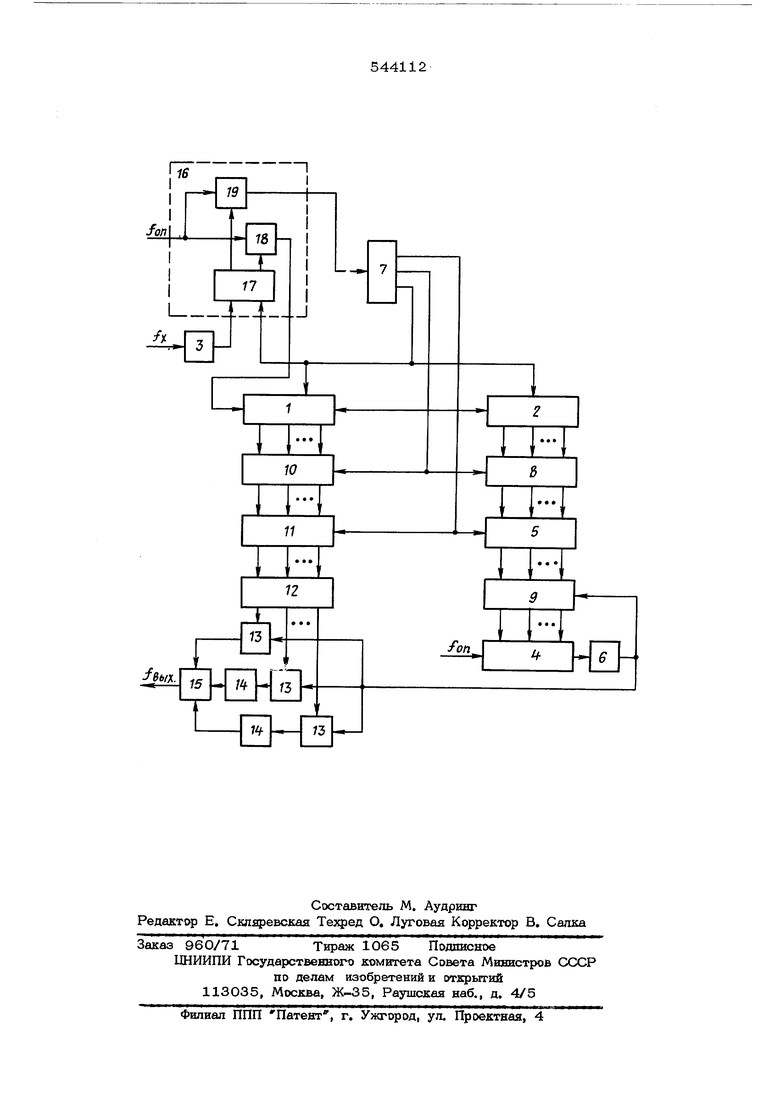

Изобретение относится к автоматике и измерительной технике и может быть исполь зовано в цифровых измерител$1х частоты. Известно устройство для умножеЕпая частоты следования периодических импульсов, содержащее делитель опорной частоты, с ко эффициентом деления, равным коэффициенту умножения, счетчик импульсов опорной час- , счетчик импульсов, формирователь, запоминающий регистр, два блока перен1х:а, построенных на схемах И и блок управления Однако это устройство характеризуется погрешностью дискретности, обусловленную некратностью числа N импульсов генератора опорной частоты foni поступающих в те чение периода Т умножаемой частоты f на вход делителя, коэффициента К деления. В результате к конну каждого периода Т.в делителе может остаться число, представляющее дробную часть частнсзго от деления N / К , что вьфажается в погрешн сти периода следования импульсов выходной последовательности, достигающей в пределе величины Целью изобретения является повышение то шости умножения. С этой целью в устройство для умножения, содержащее делитель опорной частоты с коэффициентом деления, равным коэффициенту умножения, счетчик импульсов опорной частоты, формирователи, запоминающий регистр, два блока переноса и блок управления, введены дополнительный блок переноса, дополнительный запоминающий регистр, дешифратор, элементы совпадения, линии задерй&ки, элемент ИЛИ и логическое устройство, состоящее из триггера и элементов И, первые входы которых подключены к источнику опорной частоты, вторью входы - к выходам триггера, первый вход которого соединен с выходом входного формирователя, а второй вход - с одним из выходов блока управления, другие выходы которого подключены ко входам дополнительного блока переноса и дополнительного запоминающего регистра, причем выход одного из элементов И подключен ко входу блока управления, а выход второго - ко входу делителя опорной частоты, единичные выходы которого через допол- нительный блок переноса и дополнительный запоминающий регистр, которые соединены последовательно, подключены ко входам дешифратора, при этом выходы деши4 ратора со дияены с перзыми входами элементов совпа деиия, вторые входы которых объединены и подключены к выходу выходного формирователя, выход первого непосредственно, а выходы остальных через линии задержки подключены ко входам элемента ИЛИ. На чертеже представлена структурная электрическая схема устройства для умноже ния частоты следования периодических импульсов. Устройство содержит делитель 1 опорной частоты с коэффициентом деления К, счетчал 2 импульсов, образуемых при делении опорной частоты, входной формирователь 3, счетчик 4 импульсов опорной частоты, запо минающий регистр 5, выходной формирователь 6, блок 7 управления, блоки 8 и 9 переноса кодов, построенные на логических элементах И, дополнительный блок 10 переноса кодов, дополнительный запоминающий регистр 11, дешифратор 12лэлементы совпадения 13, линии задержки 14, элемент ИЛИ 15, логический элемент 16, состоящий из триггера 17 и элементов И 18 и 19. Устройство работает следующим образом. Каждый г мпульс умножаемой частоты f. через входной формирователь 3 поступает ,на нулевой вход триггера 17, который, пере брасываясь, открывает элемслт И 19 для прохоладешш импульсов опорной частоты на вход блока 7. За время, поступления в блок 7 импульсов частоты f в этом бло-;ке вырабатываются три сигнала, первый из .которых устанавливает в, О все разряды .заноминающих регистров 5 и 11, вторий nocJTnaer иа вторые входы схем И блоков S к 10 к переносит обратный код из счетг- чика 2 в запоминающий регистр 5 и прямой код из делителя 1 в запоминающий регистр 11, третий устанавливает все разряды счетчика 2 в состояние 1 и записывает в делителе 1 число, равное количеству импуль сов HaCTOtbt fon I прошедших на вход блока 7. Одновременно третьим сигналом из блока 7 перебрасывается триггер 17 и открывается элемент И18 для прохождения импульсов fofjua вход делителя 1, Импульсы с выхода делителя 1, частота следовадаш которых равна fop/К , подаются на вход счетчика 2. За один период Т-д следовалия импульсов умножаемой частоты f на вход счетчика 2 поступает число импульсов равноеТц N K-TOH При Этом в делителе 1 к концу периода ( образуется остоточное число ni , обусловлен ное некратностью числа N импульсов опор ной частоты, поступивших на вход делителя, коэффициенту К ((П i К) Поскольку все разряды счетчика 2 предварительно были установлены в , то в счетчике 2 фиксируется число, равное Ny--J. Это число поело поступления очередного импульса умножаемой частоты сигналом из блока 7 переносится в обратном коде посредством блока 8 в запоминающий регистр 5 и, таким образом, в регистре 5 устанавливав ется дополнительный код числа N . Одновременно этШЛ же сигналом из блока 7 переносится остаток m из делителя 1 в запомир наюший регистр 11. Импульсы опорной частоты непрерывно поступают на вход счетчика 4. Каждый импульс переполнения с выхода счетчика 4 выходной формирователь 6 поступает на вторые юсоды элементов И блока9, посредством которых осуществляется перенос дополнительного кода числа NX из запоминающего регистра 5 в счетчик 4. В резуль тате на выходе выходного формирователя 6 образуется последовательность импульсов с периодом следования. Tsw Т s-Ei AT on 1 Однако в действительности период Т оказывается меньше, чем определяется остаточным числом. tn в делителе 1. В пределе это уменьшение составляет величину и, таким образом, с учетом максимальной погрешности дискретности, выражение для периода следования на выходе выходного формирователя 6 запишется Т -Ik- Т 1 К оп Для уменьшения погрешности дискретности сигнал с выхода выходного формирователя 6 подается на один из входов элементов совпадения 13, другие входы которьк соединены с соответствующими выходами дешифратора 12. Дешифратор 12 анализирует состояние запоминающего регистра 11 и в зависимости от числа fTi выдает разрешающий потенциал на первый вход соответствующего элемента совпадения 13. Число выходных шин дешифратора 12 определяется тем, во сколько ( П раз) требуется уменьшить погрешность дискретности. При этом, если число т - jTO разрешающий потенциал появляется на первом входе того элемента совпадения 13, выход которого непосредственно связан со входом элемента ИЛИ 15, При - 4 разрешающий потенциал появляется на шине дешифратора 12, связанным с первым входом элемента совпадения 13, выход которого соединен со входом элеменга ИЛИ 15 через линию задерхоси 1 со времэнй.л ва ерхски Г - IP , при 2 - 4 п соединение со входой элемента ИЛИ 15 проI Л О ОП

;сход Г через лит1Ю задержки 1-9 с L- 1 яри через линию задержки 14 с 5 Та и т.д.

Таким образом, если сигнал с выхода формирователя 6 подать на вторые входы элементов совладения 13, то период его повторения на вьЕкоде элемента ИЛИ 15 будет с учетом, максимальной псягрешности дискретности опреде; яться вьфажением

Т -Ik- °

BWXK п

15

г.е. максимальная погрешность дискретности уменьшается в п раз. При этом увели ивается стабильность коэффициента умножения, уменьшается фазово-импульсная моду- 20 ляция выходного сигнала и расширяется рабочий диапазон частот. Действительно, ус ловие отсутствия перескоков коэффициента ; умножения К запишется в виде:

25

К 1х -1

Чп

; откуда

30

f IL

Последнее вьфажекие интерпретируется еле.дующим образом:

1.Диапазон умножаемой частоты увелишвается раз.

2.При сохранении fх возможно в п ,.аз уменьшить fg,j (уменьшить быстродей твие счетчиков) или соответственно увели,1

,чить коэффициент умножения.

Выралхенне для максимально возмож. ;юй нестабильности фазы выходных импульсов умножителя запишется в виде (в радианах)

utp -aft-т.е, фаэово-импульсная модуляция выходног1 сигнала уменьшается в Т1 раз.

Формула изобретения

Устройство для умножения частоты сле.дован1ш периодических импульсов, по авт. св. N 357668, отличающееся тем, что, с целью повышения точности умножения, в него введены дополнительный блок переноса, дополнительный запоминающий регистр, дешифратор, элементы совпадения, линии задержки, элемент ИЛИ и логическое устройство, состоящее из триггера и элементов И, первые входы которых подключены к источнику опорной частоты, вторые входык выходам триггера, первый вход которого соединен с выходом входного формирователя, а второй вход - с одним из |Выходов блока управления, другие выходы которого подклк чены ко входам дополнительного блока переноса и дополнительного запоминающего регистра, причем выход одного из элементов ;И подключен ко входу блока управления, авы;ход второго - КО входу делителя опорной частоты, единичные выходы которого через дополии тельный блок переноса и дополнительный запоми. нающий регистр, которые соединены последова- ;тельно, подключены ко входам дешифратора при этом выходы дешифратора соединены с |первыми входами элементов совпадения, втотрые входы которых объединены и подключе:Ны к выходу выходного формирователя, вы;Ход первого непосредственно, а выходы ос тальных через линии задержки подключены входам элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения частоты следования периодических импульсов | 1981 |

|

SU1005285A2 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Устройство для умножения частотыСлЕдОВАНия пЕРиОдичЕСКиХиМпульСОВ | 1979 |

|

SU824419A2 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Устройство для умножения частоты следования периодических импульсов | 1978 |

|

SU769720A1 |

| Устройство умножения частоты следованияиМпульСОВ | 1979 |

|

SU822327A1 |

| Умножитель частоты | 1979 |

|

SU813728A1 |

| Умножитель частоты следования импульсов | 1974 |

|

SU513510A1 |

| Цифровой умножитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU824440A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1012431A1 |

Авторы

Даты

1977-01-25—Публикация

1975-12-01—Подача