Изобретение относится к технике передачи данных.

Известно устройство для поэлементного фазирования приемников дискретной информации, содержащее фазовый дискриминатор, состоящий из селекторов опережения и запаздывания, и блок управления 1.

Это устройство обладает низкой помехозащищенностью и точностью фазирования.

Известно также устройство для поэлементного фазирования приемников дискретной информации, содержащее последовательно соединенные задающий генератор и делитель частоты, выполненный в виде последовательно соединенных триггеров, царафазные выходы которых, кроме триггера старшего разряда, подключены к соответствующим входам первого элемента И, выход которого подключен к одному из входов второго элемента И, а также входной блок 2.

Однако и это устройство обладает низкой помехозащищенностью и точностью фазирования.

Цель изобретения - повыщение помехозащищенности и точности фазирования.

Для этого в устройство для поэлементного фазирования- приемников дискретной информации, содержащее последовательно соединенные задающий генератор и делитель частоты, выполненный в виде последовательно

2

соединенных триггеров, нарафазные выходы которых, кроме триггера старшего разряда, подключены к соответствующим входам первого элемента И, выход которого подключен к одному из входов второго элемента И, а также входной блок, введены первый и второй триггеры и третий элемент И, при этом выход задающего генератора подключен к счетнему входу первого триггера, нулевой выход которого подключен к разрешающему входу триггера младшего разряда делителя частоты, а единичный выход - к соответствующему входу триггера второго разряда делителя частоты через третий элемент И, к другому входу

которого и к нулевым входам второго триггера подключен единичный выход триггера старшего разряда делителя частоты, причем единичный вход второго триггера соединен с выходом входного блока, а единичный выход - с соответствующим входом нервого

триггера через второй элемент И, парафазные

выходы триггера старшего разряда делителя

частоты являются выходами устройства.

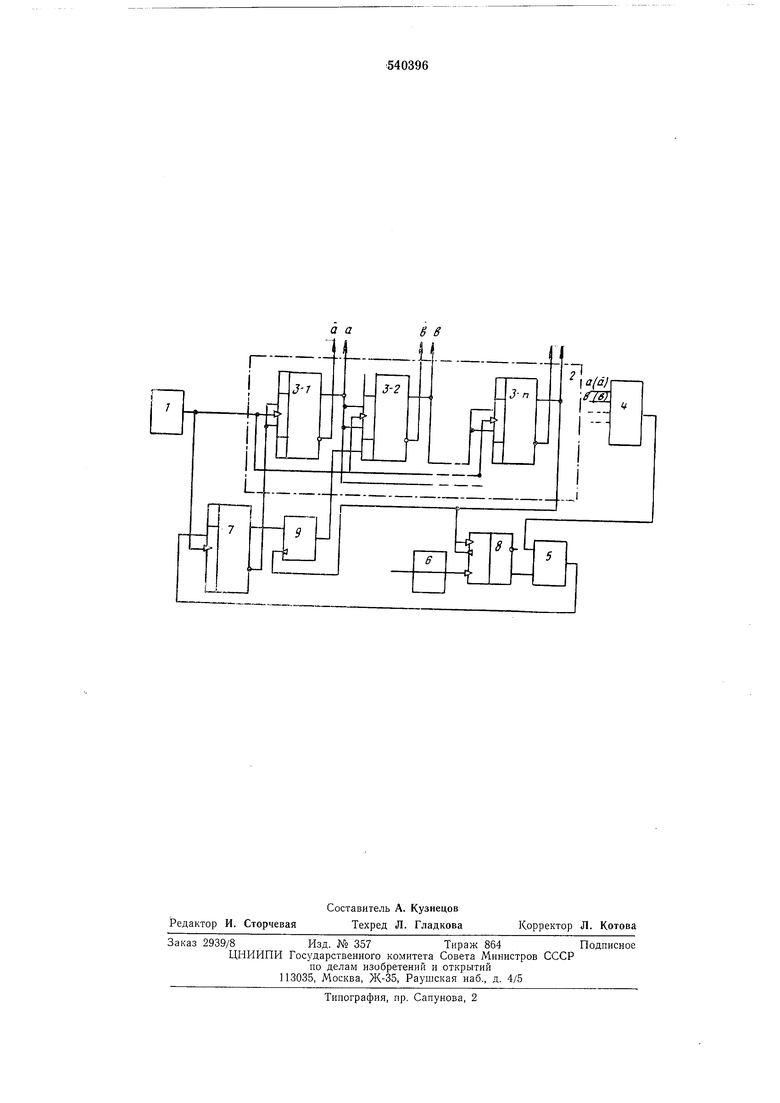

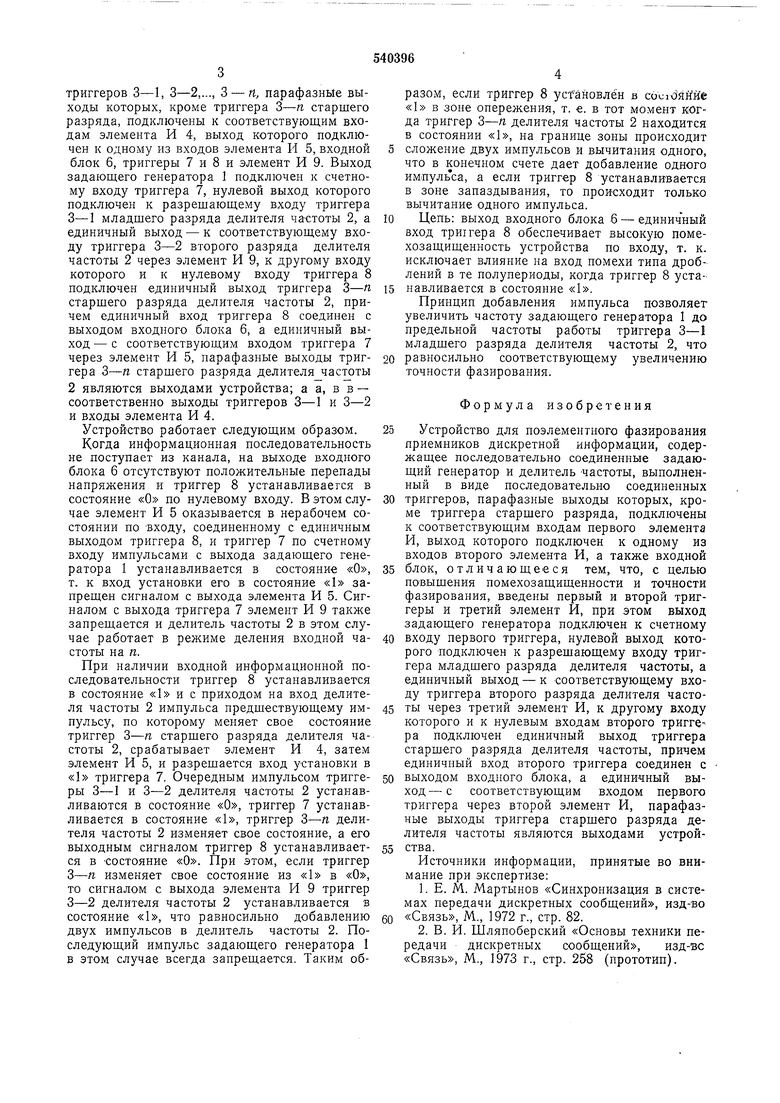

На чертеже приведена функциональная схема устройства.

Устройство для поэлементного фазирования приемников дискретной информации содержит последовательно соединенные задающий генератор 1, делитель частоты 2, выполпенный в виде последовательно соедниенных

триггеров 3-1, 3-2,..., 3 - ft, парафазные выходы которых, кроме триггера 3-п старшего разряда, подключены к соответствующим входам элемента И 4, выход которого подключен к одному из входов элемента И 5, входной блок 6, триггеры 7 я 8 и элемент И 9. Выход задающего генератора 1 подключен к счетному входу триггера 7, нулевой выход которого подключен к разрешающему входу триггера 3-1 младшего разряда делителя частоты 2, а единичный выход - к соответствующему входу триггера 3-2 второго разряда делителя частоты 2 через элемент И 9, к другому входу которого и к нулевому входу триггера 8 подключен единичный выход триггера 3-п старшего разряда делителя частоты 2, причем единичный вход триггера 8 соединен с выходом входного блока 6, а единичный выход - с соответствующим входом триггера 7 через элемент И 5, парафазные выходы триггера 3-п старшего разряда делителя частоты 2 являются выходами устройства; а а, в в - соответственно выходы триггеров 3-1 и 3-2 и входы элемента И 4.

Устройство работает следующим образом.

Когда информационная последовательность не поступает из канала, на выходе входного блока 6 отсутствуют положительные перепады напряжения и триггер 8 устанавливается в состояние «О по нулевому входу. В этом случае элемент И 5 оказывается в нерабочем состоянии по -входу, соедипенному с единичным выходом триггера 8, и триггер 7 по счетному входу импульсами с выхода задающего генератора 1 устанавливается в состояние «О, т. к вход установки его в состояние «1 запрещен сигналом с выхода элемента И 5. Сигналом с выхода триггера 7 элемент И 9 также запрещается и делитель частоты 2 в этом случае работает в режиме деления входной частоты на п.

При наличии входной информационной последовательности триггер 8 устанавливается в состояние «1 и с приходом на вход делителя частоты 2 импульса предшествующему импульсу, по которому меняет свое состояние триггер 3-п старшего разряда делителя частоты 2, срабатывает элемент И 4, затем элемент И 5, и разрешается вход установки в «1 триггера 7. Очередным импульсом триггеры 3-1 и 3-2 делителя частоты 2 устанавливаются в состояние «О, триггер 7 устанавливается в состояние «1, триггер 3-п делителя частоты 2 изменяет свое состояние, а его выходным сигналом триггер 8 устанавливается в Состояние «О. При этом, если триггер 3-п изменяет свое состояние из «1 в «О, то сигналом с выхода элемента И 9 триггер 3-2 делителя частоты 2 устанавливается в состояние «1, что равносильно добавлению двух импульсов в делитель частоты 2. Последующий импульс задающего генератора 1 в этом случае всегда запрещается. Таким образом, если триггер 8 установлен в со(лОйййе «1 в зоне опережения, т. е. в тот момент когда триггер 3-п делителя частоты 2 находится в состоянии «1, на границе зоны происходит сложение двух импульсов и вычитания одного, что в конечном счете дает добавление одного имлульса, а если триггер 8 устанавливается в зоне запаздывания, то происходит только вычитание одного импульса.

Цепь: выход входного блока 6 - единичный вход триггера 8 обеспечивает высокую помехозащищенность устройства по входу, т. к. исключает влияние на вход помехи типа дроблений в те полупериоды, когда триггер 8 устанавливается в состояние «1.

Принцип добавления импульса позволяет увеличить частоту задающего генератора 1 до предельной частоты работы триггера 3-I младшего разряда делителя частоты 2, что

равносильно соответствующему увеличению точности фазирования.

Формула изобретения

Устройство для поэлементного фазирования приемников дискретной информации, содержащее последовательно соединенные задающий генератор и делитель частоты, выполненный в виде последовательно соединенных

триггеров, парафазные выходы которых, кроме триггера старшего разряда, подключены к соответствующим входам первого элемента И, выход которого подключен к одному из входов второго элемента И, а также входной

блок, отличающееся тем, что, с целью повышения помехозащищенности и точности фазирования, введены первый и второй триггеры и третий элемент И, при этом выход задающего генератора подключен к счетному

входу первого триггера, нулевой выход которого подключен к разрешающему входу триггера младшего разряда делителя частоты, а единичный выход - к соответствующему входу триггера второго разряда делителя частоты через третий элемент И, к другому входу которого и к нулевым входам второго триггера подключен единичный выход триггера старшего разряда делителя частоты, причем единичный вход второго триггера соединен с

выходом входного блока, а единичный выход - с соответствующим входом первого триггера через второй элемент И, парафазные выходы триггера старшего разряда делителя частоты являются выходами устройства.

Источники информации, принятые во внимание при экспертизе:

1.Е. М. Мартынов «Синхронизация в системах передачи дискретных сообщений, изд-во

«Связь, М., 1972 г., стр. 82.

2.В. И. Шляпоберский «Основы техники передачи дискретных сообщений, изд-вс «Связь, М., 1973 г., стр. 258 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поэлементного фазирования приемников дискретной информации | 1976 |

|

SU642863A2 |

| Устройство поэлементного фазирования приемников дискретных сигналов | 1972 |

|

SU467490A1 |

| Устройство поэлементного фазирования приемников дискретных сигналов | 1981 |

|

SU1040616A1 |

| Устройство для измерения периода сигналов | 1983 |

|

SU1173337A1 |

| Устройство фазирования дискретных сигналов | 1980 |

|

SU896780A2 |

| Устройство поэлементного фазирования приемников дискретных сигналов | 1972 |

|

SU450377A2 |

| Формирователь синхроимпульсов биимпульсного кода | 1983 |

|

SU1128373A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119174A1 |

| Демодулятор фазоманипулированного сигнала | 1987 |

|

SU1536506A1 |

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

Авторы

Даты

1976-12-25—Публикация

1974-07-12—Подача