1

Изобретение относится к дискретным устройствам обработки информации и может быть использовано в системах передачи данных.

Известны устройства поэлементного фазирования приемников дискретных сигналов, содержащие задающий генератор, подключенный к делителю частоты. Выход старшего разряда делителя частоты соединен с селектором опережающих значащих моментов, к второму входу которого подключено входное устройство. Такие устройства имеют недостаточную точность фазирования.

В целях повышения точности фазирования без задержки начала корректирования в описываемом устройстве между выходом задающего генератора и входом делителя частоты включены последовательно соединенные схема запрета и первая схема «ИЛИ. Соответствующие выходы делителя частоты подключены к первой и второй схемам «И, выход первой схемы «И соединен с первым входом третьей и четвертой схем «И, а выход второй схемы «И подключен через пятую схему «И к щине сброса делителя частоты. Выход старшего разряда делителя частоты дополнительно соединен с первым входом второй схемы «ИЛИ и вторым входом четвертой схемы «И, а другой выход старщего разряда делителя частоты подключен к

первому входу третьей схемы «ИЛИ и второму входу третьей схемы «И и второй схемы «ИЛИ, выход которой соединен с входом триггера управления. Единичный выход триггера подключен к третьему входу четвертой схемы «И, выход которой соединен с вторым входом первой схемы «ИЛИ, а нулевой выход - к второму входу пятой схемы «И и третьему входу третьей схемы «И. Выход третьей схемы «И через последовательно соединенные третью схему «ИЛИ и формирователь подключен к второму входу схемы запрета. Входное устройство дополнительно подключено к второму входу триггера управления.

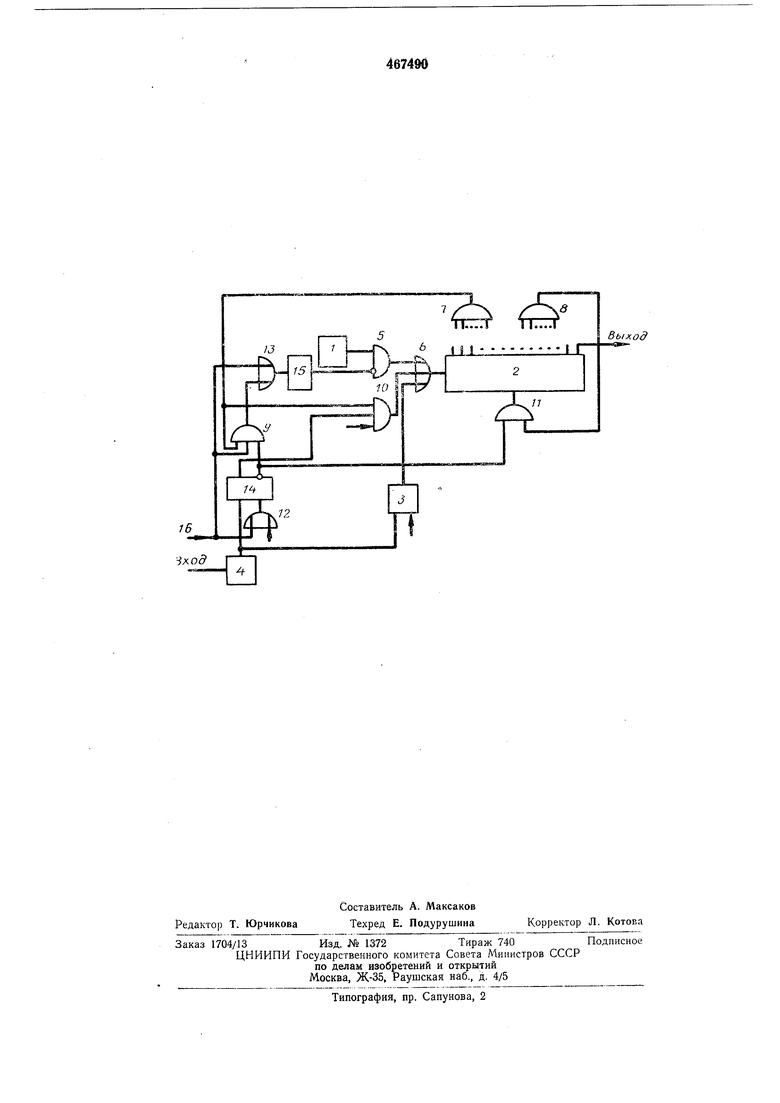

На чертен е показана функциональная схема предлагаемого устройства.

Задающий генератор 1 устройства подключен к делителю частоты 2, выход старшего разряда которого соединен с селектором 3 опережающих значащих моментов. 1 второму входу селектора подключено входное устройство 4. Между входом задающего генератора и входом делителя частоты включены последовательно соединенные схемы запрета 5 и «ИЛИ 6. Соответствующие выходы делителя частоты подключены к схемам «И 7 и 8. Выход схемы 7 подключен к первым входам схем «И 9 и 10, а выход схемы 8 связан через схему «И 11 с щиной сброса делителя

частоты. Выход старшего разряда делителя частоты дополнительно подключен к первому входу схемы «ИЛИ 12 и второму входу схемы 10, а другой выход старшего разряда делителя частоты соединен с первым входом схемы «ИЛИ 13 и вторым входом схем 9 и

12.Выход схемы 12 соединен с входом триггера управления 14, единичный выход которого подключен к третьему входу.схемы 10. Выхрд схемы 10 соединен с вторым входом схемы 6. Нулевой выход триггера подключен к второму входу схемы 11 и третьему входу схемы 9, выход которой через последовательно соединенные схему 13 и формирователь 15 подключен к второму входу схемы запрета 5. Входное устройство 4 дополнительно подключено к второму входу триггера.

Схема «И 7 выполняет функции дешифратора заранее выбранного состояния /С первых триггеров делителя частоты и определяет то число импульсов задаюш,его генератора (т), после которого в случае корректировки запаздывания запрещается один очередной импульс генератора и в случае корректировки опережения очередной импульс добавляется. Сигналы с выхода схемы 7 поступают на входы схем «И 9 и 10.

Схема «И 8 выполняет функции дешифратора состояния L делителя частоты 2. Значение L определяется выбором числа т и соответствует тому состоянию делителя, в котором он оказывается с начала коррекции за-, паздываюш,его значащего момента до моменг

та выдачи генератором - импульсов. В этот

момент по переднему фронту единичного сигнала со схемы 8 делитель сбрасывается в соD

стояние - . Сброс делителя осуществляется

сигналом со схемы «И 11, разрешенной сигналом с нулевого плеча триггера 14.

Импульсы от задающего генератора 1 проходят на делитель частоты 2 через схемы запрета 5 и «ИЛИ 6.

Установка триггера 14 в состояние «О производится по переднему фронту сигналов с нулевого и единичного выходов делителя частоты через схему «ИЛИ 12.

Импульс запрета тактовых импульсов формируется по сигналу 16 или по сигналу с выхода схемы «И 9 по цепи: схема «ИЛИ

13,формирователь 15, запрещающий вход схемы 5. Во временном интервале ожидания импульса запаздывания триггер устанавливается в состояние «О и схемы 9 и II разрешены, а схема «И 10 запрещена. Устройство работает в этом случае в режиме коррекции

ожидаемого временного интервала запаздывания. По сигналу запаздывания триггер устанавливается в состояние «1 и схемы 9 и 11 запрещаются. Схема 10 в этом временном интервале запрещена сигналом 16. Если сигнал запрета не поступает, то сигналом со схемы 8 через схему 11 делитель частоты сбрасывается, схема 9 запрещается сигналом 16, а схема 11 оказывается в нерабочем

состоянии.

Импульс опережения со входного устройства 4 устанавливает триггер в состояние «1 и по цепи: селектор 3, схема 6 проходит в делитель частоты. Через схемы 7, 10 и 6 в делитель добавляется каждый (т-|-1)-й импульс корректировки сигнала опережения.

Иредмет изобретения

Устройство поэлементного фазирования

приемников дискретных сигналов, содержащее задающий генератор, подключенный к делителю частоты, выход старшего разряда которого соединен с селектором опережающих значащих моментов, к второму входу

которого подключено входное устройство, отличающееся тем, что, с целью повышения точности фазирования без задержки начала корректирования, между выходом задающего генератора и входом делителя частоты включены последовательно соединенные схема запрета и первая схема «ИЛИ, соответствующие выходы делителя частоты подключены к первой и второй схемам «И, выход первой схемы «И соединен с первым

входом третьей и четвертой схем «И, а выход второй схемы «И подключен через пятую схему «И к щине сброса делителя частоты, выход старшего разряда делителя частоты дополнительно подключен к первому вхоДУ второй схемы «ИЛИ и второму входу четвертой схемы «И, а другой выход старщего разряда делителя частоты подключен к первому входу третьей схемы «ИЛИ и второму входу третьей схемы «И и второй

схемы «ИЛИ, выход которой соединен с входом триггера управления, единичный выход которого подключен к третьему входу четвертой схемы «И, выход которой соединен с вторым входом первой схемы «ИЛИ, а нулевой выход - к второму входу пятой схемы «И и третьему входу третьей схемы «И, выход которой через последовательно соединенные третью схему «ИЛИ и формирователь подключен к второму входу схемы запрета, причем входное устройство дополнительно подключено к второму входу триггера управления.

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поэлементного фазирования приемников дискретной информации | 1974 |

|

SU540396A1 |

| Устройство для поэлементного фазирования приемников дискретной информации | 1976 |

|

SU642863A2 |

| Устройство поэлементного фазирования приемников дискретных сигналов | 1972 |

|

SU450377A2 |

| Устройство для измерения периода сигналов | 1983 |

|

SU1173337A1 |

| Электронные часы с коррекцией показаний по эталонным сигналам времени | 1986 |

|

SU1405020A1 |

| Устройство для определения среднего | 1980 |

|

SU877563A1 |

| Устройство для преобразования временных интервалов в цифровой код | 1975 |

|

SU531124A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯХАРАКТЕРИСТИКИ ГРУППОВОГО ВРЕМЕНИЗАПАЗДЫВАНИЯ | 1972 |

|

SU428309A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119174A1 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

Авторы

Даты

1975-04-15—Публикация

1972-12-15—Подача