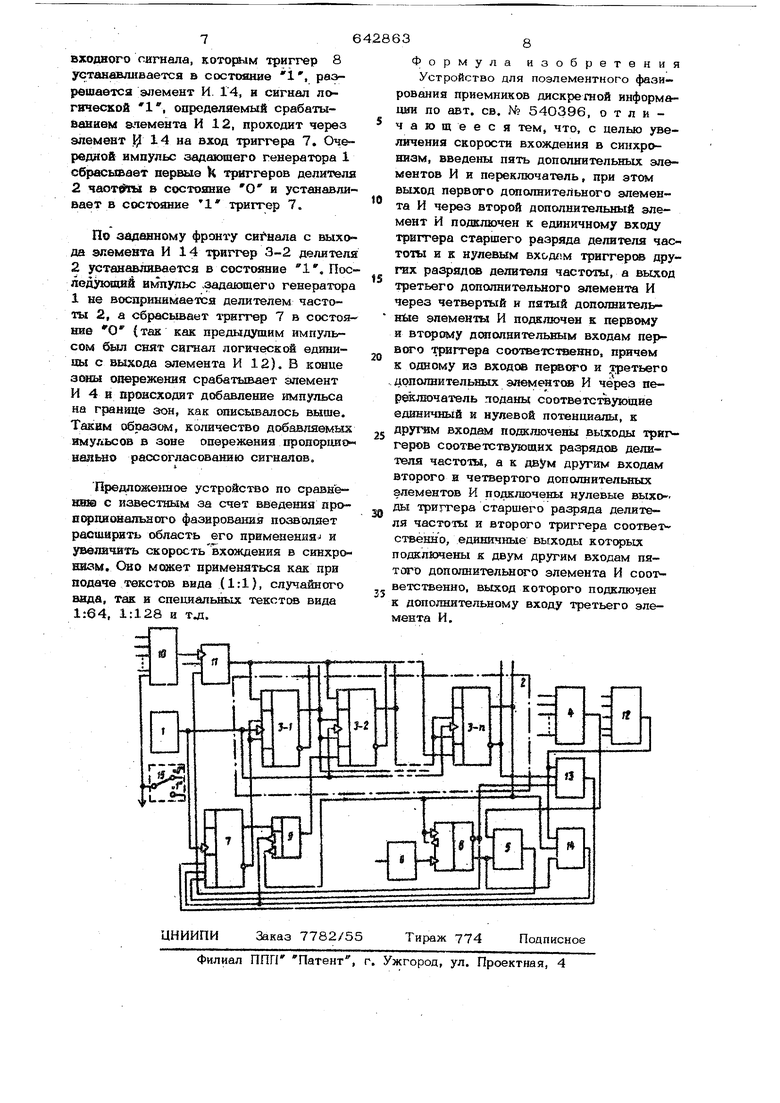

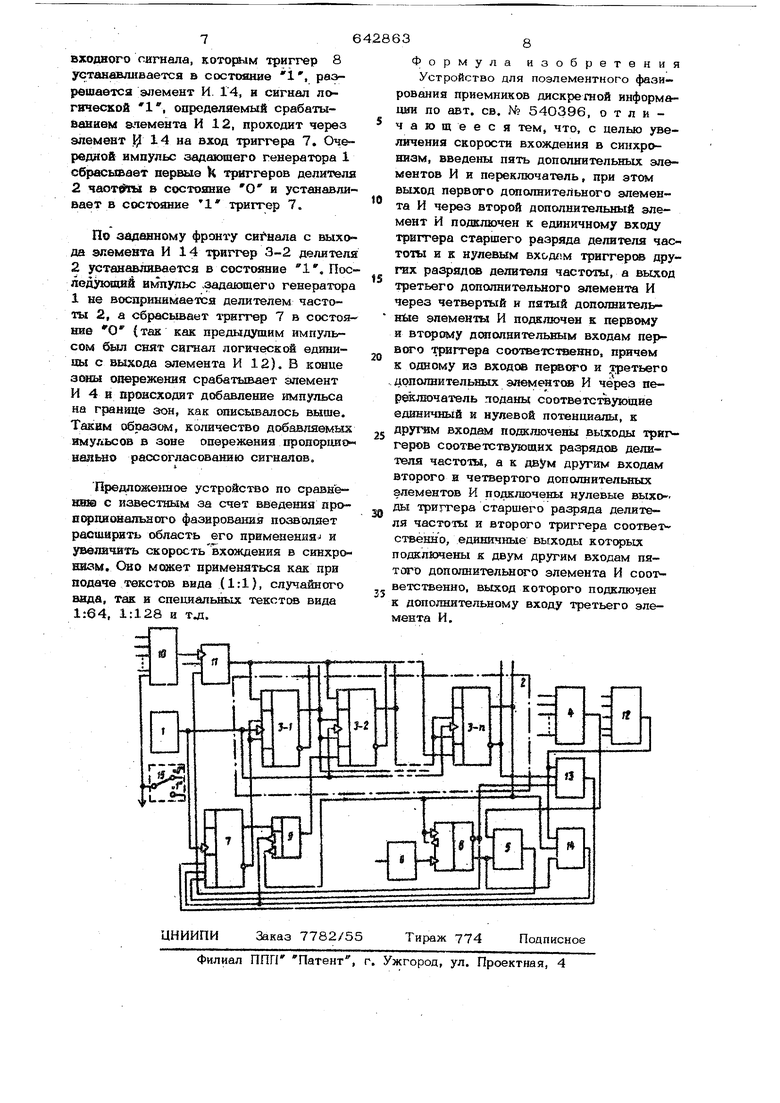

(54) УСТРОЙСТВО ДЛЯ ПОЭЛЕМЕНТНОГО ФАЗИРОВАНИЯ ПРИЕМНИКОВ ДИСКРЕТНОЙ ИНФОРМАЦИИ Ероме триггера старшего разряда, под|СЛ19чевы к соответствующим входам перисто элемента И, выход которого подкшочее к оцаому из входов второго элемента И, входной блок, первый и триггеры и третий элемент И, при этом выход эадакяцего генератора подключен к C4ettJOMy входу первого триггера, нудевой шйход которого подключен к раэрешакмдему входу триггера ктадшего разряда делителя частоты, а едаиичный выход - к соответствующему входу триг гера второго разряда делителя частоты через третий элемент И, к другому входу которого и к нулевым входам второvo триггера подключен единичный выход триггера старшего разрада дедштеля частоты, прЕгчем единичный вход второго триггера соединен с выходом вход ного блока, а единичный выход - с соотйетсХвующим входом первого тригге ра через второй элемент И, парафазные выходы триггера старшего разряда делителя частоты являются выходами усо ройства, введены пять дсиолни тельных элементов И и переключатель, при этом выход первого дополнительного элемент И через второй дополнительный элемент И пo щлючeн к единичному входу триггера старшего разряда делителя частотам и к нулевым входам триггеров других разрядов делителя частоты, а вгыход третьего дополнительного аЛемента И через четвертый и пятый доноянйтельные элементы И подключен к первому к второму дополнительным входам первого триггера соответственно, причем к одному из входов первого и третьего дополнительных элементов И через переключатель поданы со ответе твующие единичный и нулевой потенциалы к другим входам подключены выходы триггеров соответствующих разрядов делителя частоты, а к двум другим входам второго и четвертого дополнительных элементов И подключены нулевые выходы триггера старшего разряда делителя частоте : и второго триггера соответственно, единичные выходы которых подключены к двум другим входам пятого дополнительного элемен та И соответственно выход которого нодключен к дополнительному входу третьего элемента И, На чертеже приведена структурная электрическая схема устройства. Устройство для поэлементного фазирования приемников дискретной информа НИИ содержит последовательно соединенные задшоший генератор 1 и делитель 2 частоты, выполненный в виде после™ д(даятельно соединенных триггеров - 3- |Э , парафазные выходы которых, кроме триггера 3-П старшего раз-ряда, подключены к соответствукшим входам первого элемента И 4, выход которого подключен к одному из входов второго элемента И 5, входной блок б, первый 7 и второй 8 триггеры и третий элемент И 9, при этом выход задающего генератора 1 подключен к счеТному входу первого триггера 7, нулевой выход которого подключен к разрешающему входу триггера 3-1 младшего разряда делителя 2 частоты, а единичный выход - к соответствующему входу триг« гера 3-2 второго разряда делителя 2 через третий элемент И 9, к другому входу которого и к нулевым входам второго триггера 8 подключен единичный выход триггера З-п старшего разряда делителя 2, причем единичный вход второго триггера 8 соединен с выходом входного блока 6, а единичный выход с соответствующим входом первого триггера 7 через второй элемент И 5, Устройство содержит также пять дополнительных элементов И10 - И 14 я переключатель 15, при этом выход первого дополнительного элемента И 10 через второй дополнительный элемент И 11 подключен к единичному входу триггера старшего разряда З-П делителя частоты 2 и к нулевым входам триггеров 3-1, 3-2 других разрядов делителя частоты 2, а выход третьего дополнительного элемента И 12 через четвертый и пятый дополнительные элементы И 13 и И 14 подключен к первому и второму дополнительным входам первого триггера 7 соответственно, причем к одному из входов первого и третьего дополнительных элементов IИ 10, И 12 через переключатель 15 поданы соответствующие единичный и нулевой потенциалы, а к другим входам подключены выходы триггеров 3-1 3-Г) соответствующих разрядов делителя 2, к двум другим входам второго и четвертого дополнительных элементов И 11, И 13 подключены нулевые выходы триггера 3- г старшего разряда делителя 2 и второго триггера 8 соответственно, единичные выходы которых подключены к двум другим входам пятого дополнительного элемента И 14 соответственно, выход которого подключен к дополнительному входу третьего элемента И 9. Устройство работает следующим образом. При подаче на общий конуакт переключателя 15 потенциала логического О элементы И 1О и И 12 оказьшают ся запрещенными и, в свою очередь, выходными сигналами запрещают работ элементов И 11- И 14. При отсутстви входного сигнала на единичном входе триггера 8 последний сигналом с выхо да триггера старшего разряда 3-jfi де лителя 2 частоП) сбрасывается в состояние О и элемент И 5 в этом состоянии запрещается. Таким образом исключается воздействие управляющих сигналов на триггеры 3-1 - 3- п де лителя 2 и последний работает в режиьле деления частоты на г Если на единичный вход триггера 8 поступает сигнал в зоне опережения, то в момент, когда состояние делителя 2 становится равным1|/21- 1 (например для Tl , «Л / 2- ), срабатывает элемент И 4 и через элемент И 5 потенциал логической поступает на вход разрешения записи 1 в триггер 7. Очередным импульсом триг гера 7 устанавливается в состояние , триггеры 3-1 - 3-п делителя 2 устанавливаются в состояние О, триг гер старшего разряда 3- п делителя 2 частоты переходит в состояние О, и по цепи: единичный выход триггера 3- fl элемент И 9 записьтается еди ница в триггер 3-2 делителя 2 по зна- нашему моменту сигнала триггера 3- П Последующий импульс с выхоа задающего генератора 1 не воспринимается делителем 2, так как соответствующие входы триггера 3-1 запрещены сигналом с нулевого выхода триггера 7, но , сбрасывает триггер 7 в состояниеО Если же триггер 8 устанавливается в Состояние в зоне отставания, то устройство работает аналогичным образом, однако импульс записи единицы в триггер 3-2 делителя 2 не формируется, так как логический элемент И 9 оказывается запрещенным в зоне опережения до прихода импульса, определяющего величину рассогласования в этой зоне. В итоге получается не добавление одного импульса, как в зоне опережения, а запрещение одного импульса независима от величины рассог- 34 ласования фаз входного и формируемого сигналов. При установке переключателя 15 в состояние, когда на его общем контакте будет потенциал логической If, эл&менты И 1О и И 12 включены и работают допсданительно элементь И 11 И 14, причем вышеописанные режимы работы сохраняются. При отсутствии входного сигнала элементы И 5 и И 14 запрещены сигналом логического О с единичного выхода триггера 8; элемент И 13 разрешен сигналом с нулевого выхода этого же триггера 8. В зоне опаздывания сигнал с выхода элемента И 12, определяющий единичные состояния k первых, начиная, с младшего, триггеров 3-1 и 3-2 делителя 2 частоты, через элемент И 13 проходит на вход разрешения записи 1 в триггер 7, Очередной импульс сбрасывает первые К триггеров трип (3-1 и 3-2} в состояние U, а триггер 7 в состояние . Последующий импульс с вь1хода задающего генератора 1 не воздействует на делитель 2- и сбрасывает в О триггер 7. Таким образом происходит запрещение каждого 2+1 импульса до тех пор, пока в зоде опаздывания задакядий генератор 1 не выдаст количество импульсов, равное )1;/(где 11 - коа{4)ициент деления де-г лителя 2 частоты), причем в этом случае делитель 2 зафиксирует строго определенное количество импульсов, мен1 ше1Т/2. Элемент И 10 - дешифратор этого состояния. Сигнал с выхода элемента И Ю при отсутствии входного сигнала в зоне опаздывания сбрасывает триггер 3- t делителя 2 в состояние , а все другие триггеры делителя 2 - в состояние О, снимая тем самым ненужную коррекцию в этой зоне. В случае, если входной сигнал попадает в зону опаздывания, триггер 8 устанавливается в состояние 1 и элемент И 11запрещается, одновременно разрешается элемент И 5 и на границе зоны опаздывания происходит запрещение одного импульса, обусловленное срабатьшшшем элемента И 4, как объяснялось ранее. Таким образом, количество запрешенных по входу импульсов пропорционально рассогласованию в зоне опаздывания. В зоне опережения элементы И 5, И 13 и И 14 запрещены до прихода

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поэлементного фазирования приемников дискретной информации | 1974 |

|

SU540396A1 |

| Устройство поэлементного фазирования приемников дискретных сигналов | 1972 |

|

SU467490A1 |

| Устройство для сравнения фаз | 1984 |

|

SU1282254A1 |

| Устройство для определения статистических характеристик случайного процесса | 1984 |

|

SU1198539A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119174A1 |

| Устройство для измерения периода сигналов | 1983 |

|

SU1173337A1 |

| Коррелятор | 1981 |

|

SU1024933A1 |

| Цифровой измеритель резистивных параметров кабеля | 1986 |

|

SU1406517A1 |

| Сравнивающее устройство | 1986 |

|

SU1370756A1 |

| Устройство фазирования дискретных сигналов | 1980 |

|

SU896780A2 |

Авторы

Даты

1979-01-15—Публикация

1976-03-12—Подача