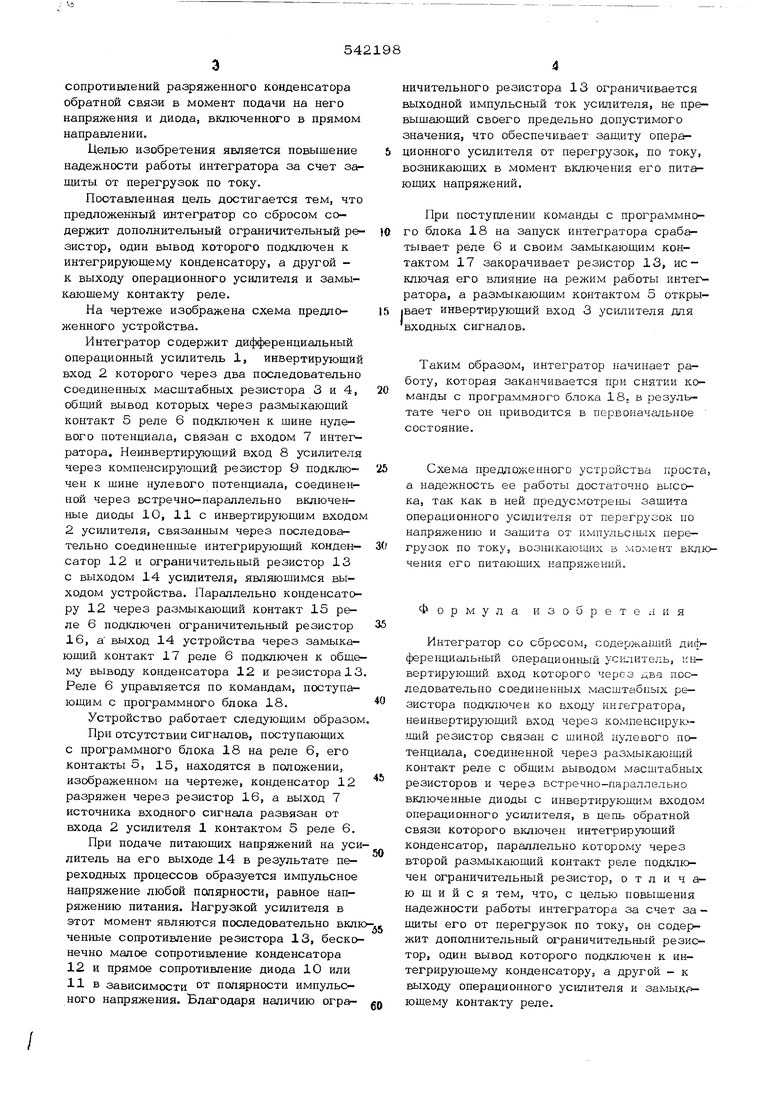

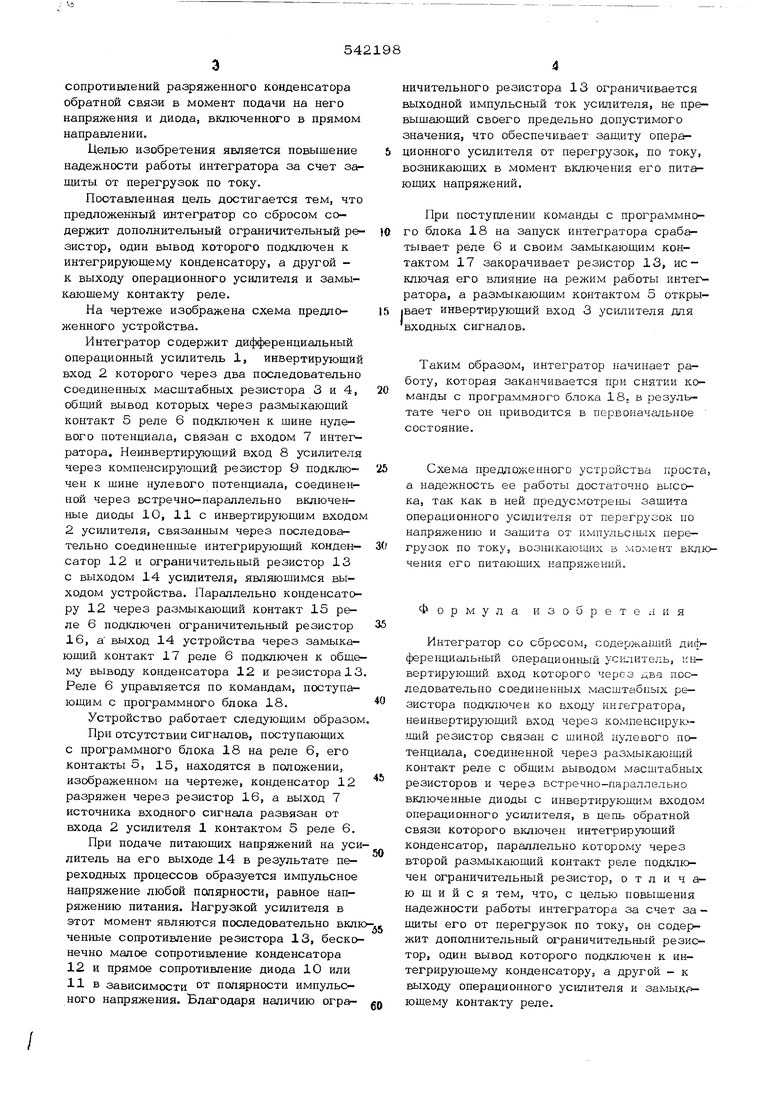

сопротивлений разряженного конденсатора обратной связи в момент подачи на него напряжения и диода, включенного в прямом направлении. Целью изобретения является повышение надежности работы интегратора за счет защиты от перегрузок по току. Поставленная цель достигается тем, что предложенный интегратор со сбросом содержит дополнительный ограничительный резистор, один вывод которого подключен к интегрирующему конденсатору, а другой к выходу операционного усилителя и замыкаюшему контакту реле. На чертеже изображена схема предпоженного устройства. Интегратор содержит дифференциальный операционный усилитель 1, инвертирующий вход 2 которого через два последовательно соединенных масштабных резистора 3 и 4, общий вывод которых через размыкающий контакт 5 реле 6 подключен к шине нулевого потенциала, связан с входом 7 интегратора. Неинвертируюший вход 8 усилителя через компенсирующий резистор 9 подключен к шине нулевого потенциала, соединенной через встречно-параллельно включенные диоды 10, 11 с инвертирующим входо 2 усилителя, связанным через последовательно соединеньиые интегрируюищй конденсатор 12 и ограничительный резистор 13 с выходом 14 усилителя, являющимся выходом устройства. Параллельно конденсатору 12 через размыкающий контакт 15 реле 6 подключен ограничительный резистор 16, а выход 14 устройства через замыкающий контакт 17 реле 6 подключен к обще му выводу конденсатора 12 и резистора 13 Реле 6 управляется по командам, поступающим с программного блока 18. Устройство работает следующим образом При отсутствии сигналов, поступающих с программного блока 18 на реле 6, его контакты 5, 15, находятся в положении, изображенном на чертеже, конденсатор 12 разряжен через резистор 16, а выход 7 источника входного сигнала развязан от входа 2 усилителя 1 контактом 5 реле 6. При подаче питающих напряжений на ус литель на его выходе 14 в результате переходных процессов образуется импульсное напряжение любой полярности, равное напряжению питания. Нагрузкой усилителя в этот момент являются последовательно вкл ченные сопротивление резистора 13, беско нечно малое сопротивление конденсатора 12 и прямое сопротивление диода 10 или 11 в зависимости от полярности импульсного напряжения. Благодаря наличию ограичительного резистора 13 ограничивается ыходной импульсный ток усилителя, не преышающий своего предельно допустимого начения, что обеспечивает защиту операионного усилителя от перегрузок, по току, озникающих в момент включения его питащих напряжений. При поступлении команды с программноо блока 18 на запуск интегратора срабаывает реле 6 и своим замыкающим конактом 17 закорачивает резистор 13, ислючая его влияние на режим работы интегратора, а размыкающим контактом 5 открывает инвертирующий вход 3 усилителя для входных сигналов. Таким образом, интегратор начинает работу, которая заканчивается при снятии команды с программного блока 18; в результате чего он приводится в первоначальное состояние. Схема предложенного устройства проста, а надежность ее работы достаточно высока, так как в ней предусмотрены зашита операционного усилителя от перегрузок по напряжению и защита от импульсных перегрузок по току, возникающих в момент включения его питающих напряжений. Формула изобретения Интегратор со сбросом, содержащий дифференциальный операционный усилитель, инвертирующий, вход которого через два последовательно соединенных масштабных резистора подключен ко входу интегратора, неинвертирующий вход через компенсирующий резистор связан с шиной нулевого потенциала, соединенной через размыкающий контакт реле с общим выводом масштабных резисторов и через встречно-параллельно включенные диоды с инвертирующим входом операционного усилителя, в цепь обратной связи которого включен интегрирующий конденсатор, параллельно которому через второй размыкающий контакт реле подключен ограничительный резистор, о т л и ч а ю щ и и с я тем, что, с целью повышения надежности работы интегратора за счет за щиты его от перегрузок по току, он содержит дополнительный ограничительный резистор, один вывод которого подключен к интегрирующему конденсатору, а другой - к выходу операционного усилителя и замыкающему контакту реле.

Источники информации, принятые во внимание при экспертизе изобретения:

1. Патент США №3702394 кл, 235-183 от 7.11. 1972 г.

2. Отраслевой стандарт Ост. II бко. 342. 007-72 Микросхемы интегральные полупроводниковые. Серия 140. Руководство по применению, стр. 187, 215.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1978 |

|

SU855674A1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Устройство для моделирования упругого гистерезиса | 1980 |

|

SU966708A1 |

| Устройство для интегрирования сигнала | 1984 |

|

SU1201853A1 |

| Импульсный генератор инфранизкой частоты | 1979 |

|

SU793303A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Измерительный преобразователь активной мощности | 1989 |

|

SU1659890A1 |

| Интегратор | 1979 |

|

SU834715A1 |

| Устройство для интегрирования знакопеременных сигналов с запоминанием промежуточных значений | 1985 |

|

SU1275484A1 |

- ()ы:

Авторы

Даты

1977-01-05—Публикация

1975-06-20—Подача