1

Изобретение относится к вычислительной технике и может быть использовано при интегрировании двух и более аналоговых сигналов последовательно во времени.

Известны интеграторы, содержащие операционный усилитель, интегрирующий конденсатор,масштабные резисторы и устройство управления для поочерёдного подключения каждого из входных сигналов ко входу интегратора через соответствующие масштабные резисторы, которое осуществляется с помощью ключей последовательного и параллельного

типа 1}.

Недостатком данных интеграторов с ключами последовательного типа является сложность, вызванная трудностью выполнения бесконтактных ключей последовательного типа, например, на дефицитных элементах - оптронах, атакже снижение точности из-за утечек ключей последовательного типа вследствие утечек, в особенности при больших постоянных времени интегрирования. В интеграторах с управляющими устройствами на более простых ключах параллельного типа утечки ключей в закрытом состоянии не снижают точности интегратора, так как токи утечек

замыкаются через низкоомные ограни-чиванхдие резисторы. Однако в этом случае точность интеграторов снижается за счет остаточного падения напряжейия на ключах, а также из-за напряжения смещени; операционного усилителя.

Наиболее близким к предлагаемому является интегратор, содержащий опе10рационный усилитель, инвертирующий вход которого соединен через конденсатор с выходом операционного усилителя, а через две параллельные цепи из переменного (масштабного) и огра15ничивающего резистора с соответствуюошми входными клеммами, причем общая точка резисторов каждой цепи подключена через ключ двухтактного распределителя к общей шине 12 1.

20

Недостатком данного интегратора является низкая точность из-за алияния остаточного напряжения на ключе и напряжения смещения операционного

25 усилителя.

Цель изобретения - повышение точности интегратора при наличии напряжения смещения операционного усилителя и остаточного напряжения ключей

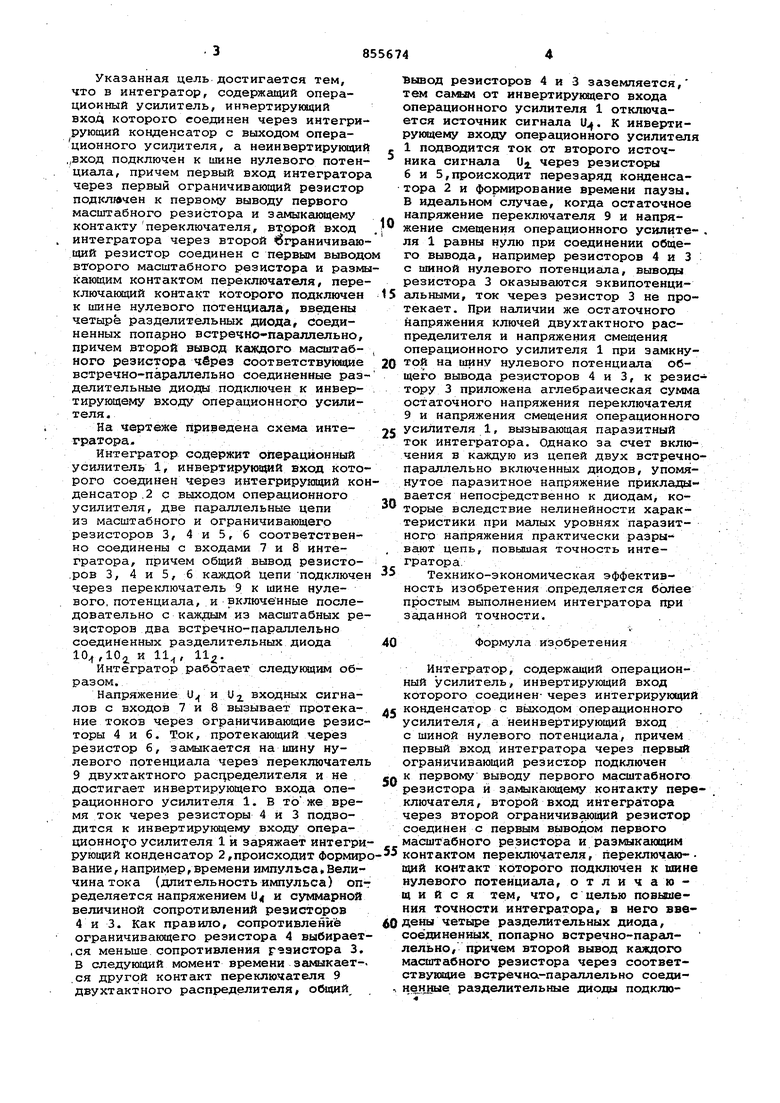

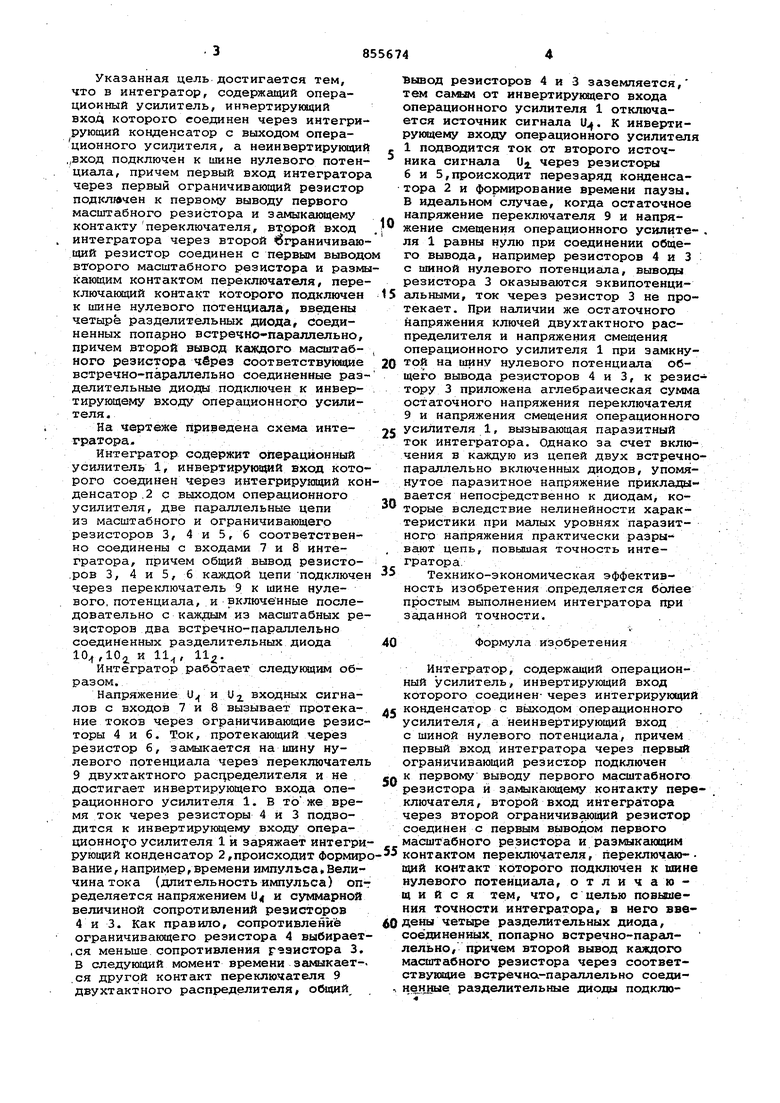

30 устройства управления. Указанная цель достигается тем, что в интегратор, содержащий операционный усилитель, инчертирунйций вход которого соединен через интегрирующий конденсатор с выходом операционного усилителя, а неинвертирукяций ,;Вход подключен к шине нулевого потенциала, причем первый вход интегратор через первый ограничивающий резистор подкл чен к первому выводу первого масштабного резистора и замыкакздему контакту переключателя, второй вход интегратора через второй Ограничиваю щий резистор соединен с первьам вывод второго масштабного резистора и разм кающим контактом переключателя, пере ключающий контакт которого подключен к шине нулевого потенциала, введены четыре разделительных диода, соединенных попарно встречно-параллельно, причем второй вывод каждого масштабного резистора чбрез соответствуквдие встречно-параллельно соединенные раз делительные диоды подключен к инвертирующему входу операционного усилителя . На чертеже приведена схема интегратора. Интегратор содержит операционный усилитель 1, инвертируюдай вход кото рого соединен через интегрирующий ко денсатор .2 с выходом операционного усилителя, две параллельные цепи из масштабного и ограничивающего резисторов 3, 4 и 5, б соответственно соединены с входами 7 и 8 интегратора, причем общий вывод резисто.ров 3, 4 и 5, б каждой цепи подключе через переключатель 9 к шине нулевого, потенциала, и включенные последовательно с из масштабных ре зисторов два встречно-параллельно соединенных разделительных диода 10 ,102. и 11, И. Интегратор работает следующим образом. , Напряжение U и Uj. входных сигналов с входов 7 и 8 вызывает протекание токов через ограничивающие резис торы 4 и б. Ток, протекающий через резистор 6, замыкается на шину нулевого потенциала через переключател 9 двухтактного распределителя и не достигает инвертирующего входа oneрационного усилителя 1, В тоже время ток через резисторы 4 и 3 подводится к инвертирукадему входу операционно:го усилителя 1 и заряжает интегри рующий конденсатор 2,происходит Формир вание, например,времени импульса Величина тока (длительность импульса) оп ределяется напряжением U и суммарной величиной сопротивлений резисторов 4 и 3. Как правило, сопротивление ограничивающего резистора 4 выбирает ,ся меньше сопротивления рзаистора 3. В следующий момент времени замыкает.ся другой контакт переключателя 9 двухтактного распределителя, общий вьшод резисторов 4 и 3 заземляется, тем самым от инвертируквдего входа операционного усилителя 1 отключается источник сигнала U. К инвертирующему входу операционного усилителя 1 подводится ток от второго источника сигнала Uj. через резисторы 6 и 5,происходит перезаряд конденсатора 2 и формирование времени паузы. 8идеальном случае, когда остаточное напряжение переключателя 9 и напряжение смещения операционного усилителя 1 равны нулю при соединении общего вывода, например резисторов 4 и 3 с шиной нулевого потенциала, выводы резистора 3 оказываются зквипотенциальными, ток через резистор 3 не протекает. При наличии же остаточного напряжения ключей двухтактного распределителя и напряжения смещения операционного усилителя 1 при замкнутой на ШИНУ нулевого потенциала Общего вывода резисторов 4 и 3, к резистору 3 приложена аглебраическая сумма остаточного напряжения переключателя 9и напряжения смещения операционного усилителя 1, вызывающая паразитный ток интегратора. Однако за счет включения в каждую из цепей двух встречнопараллельно включенных диодов, упомянутое паразитное напряжение прикладывается непосредственно к диодам, которые вследствие нелинейности характеристики при малых уровнях паразитного напряжения практически разрывают цепь, повышая точность интегратора. Технико-экономическая эффективность изобретения .определяется более простым выполнением интегратора при заданной точности. Формула Изобретения Интегратор, содержащий операционный усилитель, инвертирующий вход которого соединен- через интегрирующий конденсатор с выходом операционного усилителя, а неинвертирующий вход с шиной нулевого потенциала, причем первый вход интегратора через первый ограничивающий резистор подключен к nepBON выводу первого масштабного резистора и з.амыкающему контакту переключателя, второй вход интегратора через второй ограничивгиощий резистор соединен с первым выводом первого масштабного резистора и размыкающим контактом переключателя, переключаю-щий контакт которого подключен к шине нулевого потенциала, отличающийся тем, что, с целью повышения точности интегратора, в него введены четыре разделительных диода, соединенных. попарно встречно-параллельно, причем второй вывод каждого масштабного резистора через соответствукадие встречна-параллельно соединещше разделительные диоды подключен к инвертирующему входу оперсщион,ного усилителя.

Источники информации, принятие во внимание при экспертизе

1.:Авторское свидетельство СССР 507872, кл. G Об G 7/18, 1973.

2.: Авторское свидетельство; СССР 542198, кл. G Об G 7/18, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1984 |

|

SU1196906A1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Интегратор | 1979 |

|

SU834715A1 |

| Интегратор со сбросом | 1975 |

|

SU542198A1 |

| Интегратор со сбросом | 1982 |

|

SU1080155A1 |

| Интегратор | 1983 |

|

SU1198546A1 |

| Интегратор | 1978 |

|

SU748439A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Операционный усилитель с периодической компенсацией смещения нуля | 1982 |

|

SU1024938A1 |

| Коррелятор | 1980 |

|

SU894733A1 |

4}

Авторы

Даты

1981-08-15—Публикация

1978-03-29—Подача