Изобретение относится к автоматическому регулированию, а именно к пропорционально-интегрально-дифференциальным (ПИД) устройствам управления с ограничениями выходных сигналов и защитой их от насыщения, и может быть использовано при автоматизации различных технологических процессов.

Известны ПИД-регуляторы, содержащие усилители, интегратор, дифференциатор, сумматор, релейные и нелинейные элементы, например, ПД/ПИД-регулятор с системой ограничения дифференцирования [патент ПНР N 73281, кл. G 05 B 11/42, 1975] , в котором сигнал, приводящий в действие схему ограничения интегрирования, выдается лишь тогда, когда сигнал дифференцирования близок к нулю.

Однако такие регуляторы обладают сложной конструкцией и не обеспечивают установку необходимого соотношения между изменениями выходных сигналов интегратора и дифференциатора в процессе ограничения выходного сигнала всего регулятора, что снижает точность процесса регулирования.

Наиболее близким по технической сущности к предлагаемому является ПИД-регулятор, содержащий параллельно соединенные интегратор и дифференциатор, а также усилитель, выходы которых подключены к входам сумматора, выход которого соединен с нелинейным ограничителем и входом релейного элемента [авт. свид. СССР N 696410, кл. G 05 B 11/36, БИ, 1979, N 41].

Однако в известном регуляторе содержатся дополнительные сумматоры и нелинейный блок, с помощью которых при выходе сигнала регулятора за установленные пределы прекращается процесс интегрирования. Кроме того, когда выходной сигнал регулятора достигает одного из пределов ограничения, предотвращается дальнейшее увеличение выходного сигнала дифференциатора. В этом случае выходной сигнал дифференциатора, являющийся составной частью выходного сигнала регулятора и вызывающий срабатывание схемы ограничения интегрирования, приводит к нежелательному изменению интегральной составляющей. Это явление весьма неблагоприятно, так как ведет к значительному ухудшению качества регулирования.

Для повышения качества автоматической системы регулирования (АСР) с ограниченными управляющими воздействиями необходимо задавать нужное соотношение между изменениями выходных сигналов интегратора и дифференциатора в процессе возвращения выходного сигнала регулятора в заданные пределы. Кроме того, при отходе исполнительного механизма АСР от его крайнего положения в системе управления не должно быть излишнего упреждающего воздействия. Требуется таким образом организовать защиту от насыщения динамических составляющих закона регулирования и выходного сигнала регулятора в целом, чтобы качество управления также увеличивалось.

В предлагаемом ПИД-регуляторе, содержащем параллельно соединенные интегратор и дифференциатор, а также усилитель, выходы которых подключены в входам сумматора, выход которого соединен с нелинейным ограничителем и входом первого релейного элемента, дополнительно установлены переключатель параметров, три элемента ИЛИ и второй релейный элемент, вход которого соединен с выходом интегратора, первый и второй управляющие входы которого соединены с выходами соответственно первого и второго элементов ИЛИ, входы первого элемента ИЛИ соединены с первыми выходами первого и второго релейных элементов, входы второго элемента ИЛИ - с вторыми выходами первого и второго релейных элементов, а входы третьего элемента ИЛИ соединены с первым и вторым выходами первого релейного элемента, выход третьего элемента ИЛИ через переключатель параметров подключен к входу изменения параметров дифференциатора.

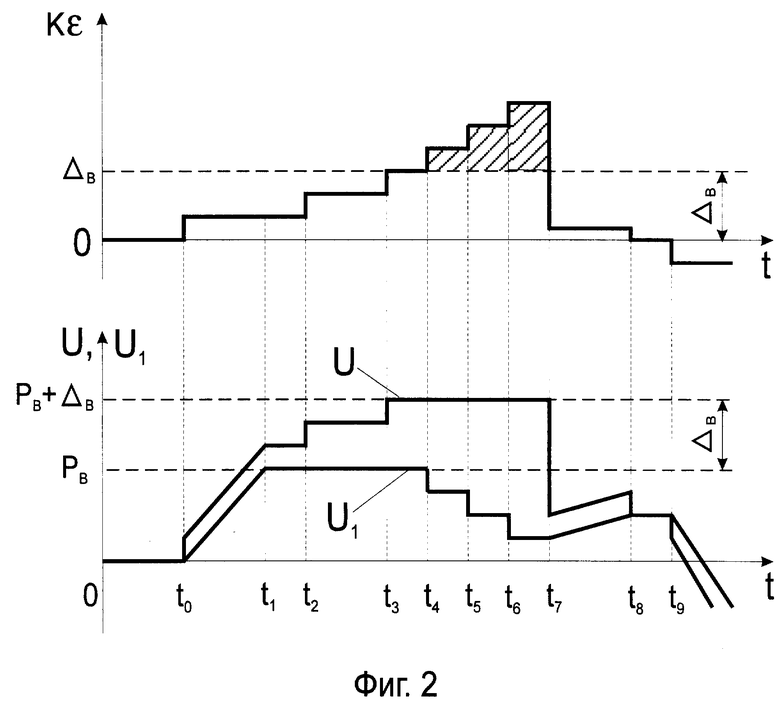

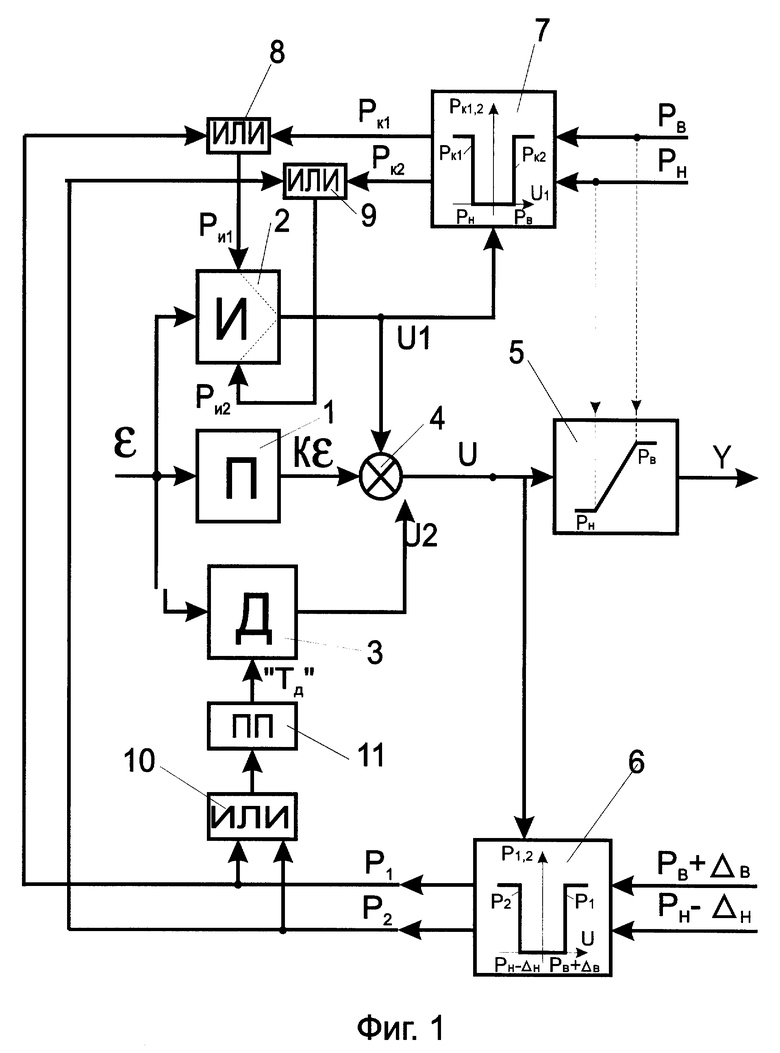

На фиг. 1 представлена блок-схема регулятора; на фиг. 2 - его временные диаграммы работы при отключенном дифференциаторе (постоянная времени дифференцирования Tд равна нулю) и при длительно действующем положительном входном сигнале (ошибка регулирования), когда выходные сигналы интегратора и регулятора достигают верхних пределов изменения PB, PB + ΔB. При длительно действующем отрицательном входном сигнале, когда выходные сигналы достигают нижних пределов изменения PH, PH - ΔH, временные диаграммы выглядят аналогично и будут симметричными относительно оси времени t.

ПИД-регулятор содержит усилитель 1 (пропорциональная часть регулятора), интегратор 2, дифференциатор 3, сумматор 4, нелинейный ограничитель 5, первый и второй релейные элементы 6, 7, первый, второй и третий элементы ИЛИ 8-10 и переключатель 11 параметров дифференциатора (его постоянной времени Tд). Переключатель параметров 11 может представлять собой, например, переключающее реле, которое коммутирует два резистора в RC-цепи, на базе которой обычно реализуется дифференцирующее звено.

Вход ε регулятора (ошибка регулирования) соединен с входом усилителя 1 и основными входами интегратора 2 и дифференциатора 3. Выходы блоков 1, 2, 3 подключены к входам сумматора 4, выход U которого соединен с входом нелинейного ограничителя 5 и входом первого релейного элемента 6, первый вход P1 которого соединен с первыми входами первого и третьего элементов ИЛИ 8, 10. Второй вход третьего элемента ИЛИ 10 подключен к второму выходу P2 первого релейного элемента 6 и первому входу второго элемента ИЛИ 9, другой вход которого подключен ко второму выходу PК2 второго релейного элемента 7, вход которого соединен с выходом интегратора 2, первый PИ1 и второй PИ2 управляющие входы которого подключены к выходам соответственно первого 8 и второго 9 элементов ИЛИ. Первый выход PК1 второго релейного элемента 7 соединен с другим входом первого элемента ИЛИ 8. Выход третьего элемента ИЛИ 10 соединен с входом переключателя параметров 11, выход которого соединен с входом изменения параметров Tд дифференциатора 3. Выход нелинейного ограничителя 5 подключен к выходному каналу регулятора Y. Настройка верхнего PВ и нижнего PН пределов изменения выходного сигнала U1 интегратора 2 и выходного сигнала Y регулятора производится через задающие входы блоков 5, 7 от первого и второго задающих каналов PВ, PН. Настройка верхнего и нижнего пределов изменения выходного сигнала U сумматора 4 производится через задающие входы блока 6 от третьего и четвертого задающих каналов PB + ΔB и PH - ΔH. Пределы изменения выходного сигнала U сумматора 4 расширены по сравнению с пределами изменения выходных сигналов U1 интегратора и Y регулятора, то есть ΔB > 0 и ΔH > 0.

Регулятор работает следующим образом.

Входным сигналом регулятора является сигнал рассогласования ε между заданным и текущим значениями регулируемого параметра. Входной сигнал ε поступает одновременно на входы усилителя 1 (пропорциональное звено), интегратора 2 и дифференциатора 3, выходные сигналы которых подаются на входы сумматора 4 и образуют выходной сигнал U, который в линейном режиме является алгебраической суммой пропорциональной, интегральной и дифференциальной составляющих закона регулирования. При этом выходной сигнал U сумматора 4 находится в заданных пределах (PH - ΔH , PB + ΔB), расширенных по сравнению с заданными пределами (PН, PВ) изменения выходных сигналов U1 интегратора и Y регулятора, которые также находятся внутри своих заданных пределов (PН, PВ). Логические сигналы P1, P2 на выходах первого и PК1, PК2 на выходах второго релейных элементов 6, 7 равны нулю. Следовательно, равны нулю сигналы на выходах всех трех элементов ИЛИ, а значит отсутствуют сигналы на входе переключателя 11 параметров дифференциатора и на обоих управляющих входах PИ1, PИ2 интегратора. Интегратор 2 и дифференциатор 3 реализуют обычные стандартные операции интегрирования и дифференцирования входного сигнала ε регулятора с заданными значениями постоянных времени TИ и TД.

Выходной сигнал Y регулятора повторяет выходной сигнал U сумматора 4, если U находится в заданных пределах (PН, PВ), и

если сигнал U вышел за заданные пределы (PН, PВ).

Уровни ограничения выходных сигналов регулятора Y и интегратора U1 определяются уровнями сигналов, поступающих из задающих каналов PВ и PН . Расширенные уровни ограничения выходного сигнала U сумматора 4 определяются уровнями сигналов, поступающих из задающих каналов PB + ΔB и PH - ΔH, где ΔB > 0 и ΔH > 0. Регулятор реализует линейный ПИД-закон управления - см. фиг. 2, отрезки времени t ≤ t1 и t ≥ t7.

Когда выходной сигнал U1 интегратора 2, изменяясь, становится больше верхнего предела PВ, на выходе PК1 второго релейного элемента 7 появляется логический сигнал "единица" (т.е. PК1 = "1"), которая через первый элемент ИЛИ 8 поступает на первый управляющий вход PИ1 интегратора 2. Сигнал PИ1 = "1" дает команду на принудительное уменьшение с заданной скоростью выходного сигнала U1 интегратора 2 до верхнего граничного уровня PВ, т.е. возвращает U1 в заданные пределы (PН, PВ). Такая ситуация возникает в предлагаемом ПИД-регуляторе при небольших, но длительно действующих ошибках регулирования ε при Kε ≤ ΔB, где K - коэффициент передачи усилителя 1 (пропорциональной части) - см. фиг. 2, отрезок времени t1 - t4.

Аналогично при выходе сигнала U1 за нижний предел PН на выходе PК2 релейного элемента 7 появляется логическая "единица", которая через второй элемент ИЛИ 9 поступает на второй управляющий вход PИ2 интегратора, что приводит к "принудительному" увеличению с заданной скоростью выходного сигнала U1 интегратора и возвращению его в заданные пределы (PН, PВ). Такая ситуация возникает при небольших (по модулю), но также длительно действующих ошибках регулирования ε при |Kε| ≤ ΔH и Kε < 0.

Когда выходной сигнал U сумматора 4, изменяясь, становится больше верхнего расширенного предела PB + ΔB, на выходе P1 первого релейного элемента 6 появляется логический сигнал "единица", которая через первый элемент ИЛИ 8 поступает на первый управляющий вход PИ1 интегратора и через третий элемент ИЛИ 10 и переключатель параметров 11 - на вход изменения параметров Tд дифференциатора 3. В дифференциаторе устанавливается малая постоянная времени дифференцирования TД1, близкая к нулю, в результате чего дифференциальная составляющая U2 выходного сигнала ПИД-регулятора будет быстро уменьшаться до нуля, способствуя уменьшению выходного сигнала U сумматора 4 до верхнего расширенного граничного уровня PB + ΔB. Одновременно с этим по команде PИ1 = 1 происходит уменьшение интегральной составляющей U1 выходного сигнала ПИД-регулятора. Совокупное действие этих эффектов уменьшения U1 и U2 уменьшает выходной сигнал U сумматора 4 до верхнего граничного уровня PB + ΔB, т.е. возвращает его в заданные расширенные пределы (PH - ΔH , PB + ΔB). На фиг. 2 (отрезок времени t4 - t7) показаны диаграммы работы ПИД-регулятора при отключенном дифференциаторе 3 (время TД ≡ 0) и при больших ошибках регулирования (Kε > ΔB), где для удержания выходного сигнала U сумматора 4 на верхнем расширенном граничном уровне PB + ΔB выходной сигнал U1 интегратора уменьшается на величину ΔU1 = Kε - ΔB.

Аналогично при выходе сигнала U сумматора 4 за нижний расширенный предел PH - ΔH, на выходе P2 первого релейного элемента 6 появляется логическая "единица", которая через второй элемент ИЛИ 9 поступает на второй управляющий вход PИ2 интегратора и через третий элемент ИЛИ 10 и переключатель параметров 11 - на вход изменения параметров Tд дифференциатора 3. В дифференциаторе также устанавливается малая постоянная времени TД1, близкая к нулю, в результате чего дифференциальная составляющая U2 выходного сигнала ПИД-регулятора будет быстро увеличиваться до нуля (уменьшаться по абсолютной величине), способствуя увеличению выходного сигнала U сумматора 4 до нижнего расширенного граничного уровня PH - ΔH. Одновременно с этим по команде PИ2 = 1 происходит увеличение интегральной составляющей U1 выходного сигнала ПИД-регулятора. Совокупное действие этих эффектов увеличения U1 и U2 увеличивает выходной сигнал U сумматора 4 до нижнего расширенного граничного уровня PH - ΔH, т.е. возвращает его в заданные расширенные пределы (PH - ΔH , PB + ΔB).

Исследования предлагаемого ПИД-регулятора совместно с моделью объекта управления показывают, что в процессе возвращения выходного сигнала регулятора в заданные пределы дифференциальную составляющую U2 следует изменять в 5-10 раз быстрее, чем интегральную составляющую U1. Это соотношение устанавливают с помощью выбора значения малой постоянной времени дифференциатора TД1 и выбором скоростей принудительного увеличения и уменьшения интегральной составляющей по соответствующим командам PИ1 и PИ2.

Расширение заданных пределов изменения (PH - ΔH , PB + ΔB) выходного сигнала U сумматора по сравнению с заданными пределами изменеия (PН, PВ) выходного сигнала Y регулятора позволяет устранить излишнее упреждающее воздействие в системе управления при отходе исполнительного механизма от его крайних положений, соответствующих сигналам PН и PВ на выходе Y регулятора. Кроме того, все изменения выходного сигнала U сумматора 4 в процессе его ограничения на границах расширенного диапазона не проходят на выход регулятора через нелинейный ограничитель 5 и не могут воздействовать на регулируемый параметр. Поэтому предлагаемый регулятор обеспечивает существенное улучшение динамических характеристик систем регулирования технологических параметров.

По сравнению с известными, предлагаемый регулятор имеет более простую конструкцию и наряду с согласованными ограничениями выходных сигналов регулятора обеспечивает дополнительно защиту от насыщения динамических составляющих закона управления, что улучшает динамику процессов регулирования вследствие реализации регулятора с "антинасыщением". При этом простыми средствами обеспечивается оптимальное соотношение между приращениями интегральной и дифференциальной составляющих закона регулирования в процессе ограничения (сброса) выходного сигнала регулятора, что способствует повышению точности регулятора.

Предлагаемый ПИД-регулятор с ограничениями выходных сигналов и защитой их от насыщения можно выполнить на элементах цифровой и микропроцессорной техники, и даже на элементах и модулях промышленной пневмоавтоматики его реализация не вызывает затруднений.

Изобретение относится к автоматическому регулированию, а именно к пропорционально-интегрально-дифференциальным (ПИД) устройствам управления с ограничениями выходных сигналов и защитой их от насыщения, и может быть использовано при автоматизации различных технологических процессов. Технический результат изобретения заключается в повышении качества регулирования. Предлагаемый ПИД-регулятор содержит параллельно соединенные интегратор и дифференциатор, а также усилитель, выходы которых подключены к входам сумматора, выход которого соединен с нелинейным ограничителем и входом первого релейного элемента, переключатель параметров, три элемента ИЛИ и второй релейный элемент, вход которого соединен с выходом интегратора, первый и второй управляющие входы которого соединены с выходами соответственно первого и второго элементов ИЛИ, входы первого элемента ИЛИ соединены с первыми выходами первого и второго релейных элементов, входы второго элемента ИЛИ - с вторыми выходами первого и второго релейных элементов, а входы третьего элемента ИЛИ соединены с первым и вторым выходами первого релейного элемента, выход третьего элемента ИЛИ через переключатель параметров подключен к входу изменения параметров дифференциатора. 2 ил.

Пропорционально-интегрально-дифференциальный регулятор с ограничениями выходных сигналов, содержащий параллельно соединенные интегратор и дифференциатор, а также усилитель, выходы которых подключены к входам сумматора, выход которого соединен с нелинейным ограничителем и входом первого релейного элемента, отличающийся тем, что он дополнительно содержит переключатель параметров, три элемента ИЛИ и второй релейный элемент, вход которого соединен с выходом интегратора, первый и второй управляющие входы которого соединены с выходами соответственно первого и второго элементов ИЛИ, входы первого элемента ИЛИ соединены с первыми выходами первого и второго релейных элементов, входы второго элемента ИЛИ - со вторыми выходами первого и второго релейных элементов, а выходы третьего элемента ИЛИ соединены с первым и вторым выходами первого релейного элемента, выход третьего элемента ИЛИ через переключатель параметров подключен к входу изменения параметров дифференциатора.

| Пропорционально-интегральнодифференциальный регулятор | 1977 |

|

SU696410A1 |

| Несущая поверхность самолета, имеющая предкрылки | 1947 |

|

SU73281A1 |

| Пропорционально-интегрально-дифференциальный регулятор | 1976 |

|

SU628462A1 |

| US 3819999 A, 25.06.74. | |||

Авторы

Даты

1998-10-20—Публикация

1998-02-03—Подача