VSO УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ

ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Устройство для вычисления корня к-ой степени | 1976 |

|

SU736096A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Матричное устройство для решения дифференциальных уравнений в частных производных | 1982 |

|

SU1120346A1 |

| Устройство для извлечения квадратного корня и его обратной величины | 1988 |

|

SU1545218A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

1

Изобретение относится к вычислительной технике и может быть применено в качестве спецпроцессора в комплексе с цифровой вычислительной ма- шиной или в специализированных вычислительных устройствах для оперативной реализации вычислительного процесса, наггример в системах автоматического управления динамическими бб1 ектами.

Известно устройство, содержащее генератор тактовых импульсов, элемент запрета. Делитель частоты аргумента, счетчик аргумента, делитель частоты участков аппроксимации, счетчик результата, делители частоты, ;блок вычитания и масштабирующий блок, причем управляющий и информационный входы регистра подключены соответ- ственно к выходу делителя частоты участков аппроксимации и вы- , ходу счетчика участков аппроксимации, а управляющие входы первого и второго делителей частоты подключены

соответственно к выходу регистра и выходу счетчика участков аппроксимации Cl 3Недостатком известного устройства является относительно низкая точность 5 из-за необходимости реализации кусочно-линейной аппроксимаций воспроизводимой функции, ограниченные функциональные возможности и относительно низкое быстродействие, определяемое последовательной организацией вычислительного процесса.

Наиболее близким к изобретению по технической сущности является уст.ройство, содержащее два сумматора, два блока деления, пять блоков умножения и блок сведения баланса, пер- вый вход первого сумматора соединен с выходом первого блока умножения,

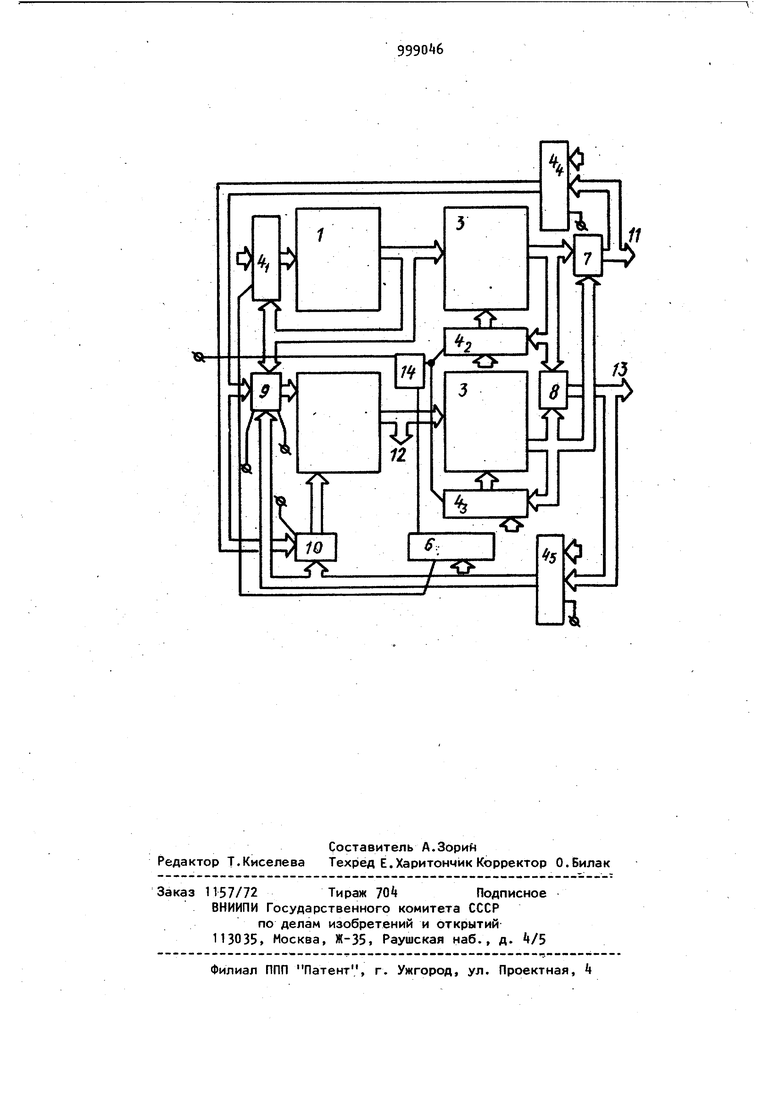

20 второй вход первого сумматора соедиHfeH с выходом второго блока умножения, первый вход которого соединен с выходом блока деления C2l. Недостатком известного устройства являются ограниченные функциональные .возможности, относительно низкое быстродействие, а также относительная сложность, определяемая налйчием блока сведения баланса и сложностью управления вычислительным процессом. Цель изобретения - повышение быст родействия. Поставленная цель достигается те что в уст 3ойство для вычисления эле ментарных функций, содержащее блок деления, два блока умножения и сум-, матор, первый вход которого соедине .с выходом первого блока умножения, второй вход сумматора соединен с выходом второго блока умножения, первый вход которого соединен с выходом блока деления, дополнительно введены пять регистров, регистр сдвига, два коммутатора, элемент И, вычитатель и блок извлечения корня, вход которого соединен с выходом первого регистра, вход записи которого соединен с выходом блока извле чения корня, первым информационным входом первого коммутатора и первым входом первого блока умножения, вто рой вход которого соединен с выходо второго регистра, вход записи которого соединен с выходом Первого бло ка умножения и первым входом вычитателя, второй вход которого соединен с выходом второго блока умножен и входом записи третьего регистра, выход которого соединен со вторым входом второго блока умножения, выход сумматора соединен с входом записи четвертого регистра, выход которого соединен с вторым информационным входом первого Коммутатора и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом пятого регистра и третьим информационным входом первого коммута тора, выход которого соединен с первым входом блока деления, второй вход которого соединен с выходом вто рого коммутатора, выход вычитателя соединен с входом записи пятого регистра, вход тактовщх импульсов уст ройства соединен с тактовыми входами первого регистра и регистра сдви га и первым входом элемента И, втор вход которого соединен с выходом ре гистра сдвига, выход элемента И сое динен с тактовыми входами второго и третьего регистров, входы ратрешения записи четвертого и пятого регистров соединены с входом разрешения установки устройства, вход задания режима которого соединен с управляющими входами первого и второго коммутаторов, установочные входы регистров соединены с входом ввода аргумента устройства. На чертеже представлена блок-схема устройства. Устройство для вычисления элементарных функций содержит блок 1 извлечения корня, блок 2 деления, блоки 3 умножения, регистры ,вход 5 тактовых импульсов, регистр 6 сдвига, сумматор 7, вычитатель 8, коммутаторы 9 и 10, выходы 11-13 устройства, элемент И 14. Ьлок 1 извлечения корня конструктивно содержит (п-1) группу последовательно соединенных одноразрядных сумматоров по ( 2-fi)B каждом (i 1 ,2 ,. .. ,п-1) , (п-2)группы из . i сумматоров по модулю два в каждой i-й группе, (п-1) инвертор, элемент ИЛИ и генератор единиц, причем выход каждого {j+l)-ro одноразрядного сумматора (j 1,2,...2+i) i-й группы соединен с первым входом j-ro одноразрядного сумматора (1+1)-и группы, второй вход первого одноразрядного сумматора соединен с выходом переноса первого одноразрядного сумматора i-группы, входом (i+l)-ro разряда выхода блока, первым входом К-го (К 1,2 - i)сумматора по модулю . два i-й Группы, подключенного своим выходом ко второму входу (К+1)-го одноразрядного сумматора (1+1)-и группы и второму входу (К+1)--го одноразрядного сумматора (1+1)-й группы и второму входу (К+1 )-го .сумматора по модулю два всех групп, начиная с М+и-й, выходы первого и второго разрядов входа блока соотвественно с первыми входами первого и второго одноразрядных сумматоров первой группы и входами элемента ИЛИ, подключенного своим выходом ко входу старшего разряда выходной шины, второму входу первого сумматора по модулю два всех групп и входу первого инвертора выход которого соединен с вторым входом первого одноразрядного сумматора первой группы, 2 (,i +1)-й и (2- + +1)-й разряды входа блока подключены соответственно к третьему входу рд- , норазрядного сумматора младшего раз ряда i й группы, входу (i+l)ro инвертора, подключенного к первому входу предпоследнего одноразрядного сумматора (i+1)-и группы, и второму входу одноразрядного сумматора младшего разряда , i-и группы,первый инверсный вход которого соединен с йулевой шиной устройства, а выход генератора единиц подключен ко второму входу второго одноразрядно го сумматора первой группы. Блок 2 деления содержит п групп последова тельно соединенных одноразрядных су маторов по (.п+1) в каждой и м гру из п сумматоров по модулю два, при чем выход каждого (j+IJ-ro однораз рядного сумматора (j 1,2,..,п+1 i-й группы (i 1,2,...,п)соединен с первым входом j-го одноразрядного сумматора (i+1)-ni группы, второй вход первого одноразрядного суммато ра i-rt группы соединен с выходом переноса пеового одноразрядного сумматора О-О-й группы, первым входом каждого К-го (,2,,., ,п) сумматора по модулю два 1-й группы подключенного своим выходом ко второму входу (K-t-l)-ro одноразрядного сумматора i-й группы, третьему вход одноразрядного сумматора младшего разряда i-й группы и входу i-ro разряда выхода блока, вторые входы К-го сумматора по модулю два каждой i-й группы объединены и подключены к выходу К-го разряда первого входа .блока, первый вход j-ro одноразрядного сумматора первой группы и второй вход одноразрядногЬ сумматора младшего разряда (i+)-й группы подключены соответственно к выходу j-ro разряда и (a+1+i)-ro разряда второго входа блока,.а второй вход первого одноразрядного сумматора первой группы, первые входы всех сум маторов по модулю два первой группы и третий вход одноразрядного сумматора млади1его разряда первой группы подключены к входу единичного сигнала. Работу устройства, реализующего вычисление зависимостей Х.-гХ.х -X. 1 . -t , а-а .О . с.оЧа« -«(в частном случае при вычисление гиперболических функций shx, chx. sechx, cosechx, thx, cthxj,поясним на конкретном примере. Представим выражение у а в разрядной форме, полагая, что а принимает произвольные значения и -14 X 1. В результате преобразова НИИ получим-J ,OL«lU,J.,0-i))t а J -J c,(-) где а 1, х - значение Г-го раз- ряда аргумента х. Работа устройства происходит следующим образом. В исходном состоянии первый вход первого коммутатора 9 и второй вход второго коммутатора 10 соединены соответственно с выходами коммутаторов, в первый регистр k записано значение а, во второй 2, четвертый k и пя :тый k регистры записано значение единицы, а в сдвиговый регистр 6 записано значение X. В устройстве происходит переходной процесс,после окончания которого на выходе блока извлече- ч корня 1 образуется значение О-, на блоке 2 деления образуется значение 1/16 , а на выходах блоков 3 умножения, сумматора 7и вычитателя 8 по выражению (1) образуются значения соответственно Vaj/VE. H:ftjL-V5-l/ S, при а В. можно считывать со с двигом на один разряд в сторону старших разрядов значения гйперболического секанса sech х. При подаце. на управлякяций вход пятого регистра kg сигнала записи, на управляющий вход второго коммутатора 10 и второй управляющий вход первого коммутатора 9 единичных сигналов., благодаря которым к их выходам подключаются первый и третий входы, соответственно, и после записи в третий регистр k единицы, на втором выходе устройства 12 образуется знаили при а С. значение а -01гиперболического косеканса cosechx, который можно считывать со сдвигом на один разряд в сторону старших разрядов. Аналогично при подаче на управляющие входы третьего и пятого регистров сигнала записи и на первый управляющий вход первого коммутатора 9 единичного сигнала на выа -с.ходе 12 образуется значение о. .а а при подаче на второй управляющий .вход первого коммутатора 9 и управляющий вход второго коммутатора 10 единичных сигналов, на выходе 12 образуется значение , ном случае, когда а Е, на втором управляющем выходе 12 образуются .значения гиперболических тангенса ..« thx и котангенса cthx, соответстве но. 8 предлагаемом устройстве сущест венно увеличено быстродействие, в отличие -ОТ известного. В предлагаемо устройстве за (h-1) такт вычисляется значения двух функций а + , а и еще за один такт - любая из четыре функций с.ао.,9 d ,При этом такт в предлагаемом устройстве равен времени переходного процесса в схеме устройства и практи чески составляет единицы микросекунд В предлагаемом устройство также существенно упрощено управление вычислительным процессом, которое сводится только, к подаче (n-l)-ro импульса на вход устройства. Формула изобретения Устройство для вычисления элементарных функций, содержащее блок деления, два блока умножения и сумматор, первый вход которого соединен с выходом первого блока умножения, второй вход сумматора соединен с выходом второго блока умножения, первый вход которого соединен с выходом блока деления, отличающеес я тем, что, с цепью повышения быстродействия, в него введены пять регистров, регистр сдвига, два коммутатора, элемент И, вычитатель и блок извлечения корня, вход которого соединен с выходом первого регистра. вход записи которого соединен с выXOflOM блока извлечения корня, первым информационным входом первого коммутатора и первым входом первого блока умножения, второй вход которого соединен с выходом второго регистра, вход записи которого соединен с выходом первого блока умножения и первым входом вычитателя, второй вход которого соединен с выходом второго блока умножения и входом Записи третьего регистра, выход которого соединен со вторым входом второго блока умножения, выход сумматора соединен с входом записи четвертого регистра, выход которого соединен с вторым информационным входом первого коммутатора и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом пятого регистра и третьим информационным входом первого коммутатора, выход которого соединен с первым входом блока деления, второй вход которого соединен с выходом второго коммутатора, выход вычитателя соединен с входом записи пятого регистра,вход тактовых импульсов устройства соединен с тактовыми входами первого регистра и регистра сдвига и первым входом элемента И, второй вход которого соединен с выходом регистра сдвига, выход элемента И соединен с тактовыми входами второго и третьего регистров, входы разрешения записи четвертого и пятого регистров соединены с входом разрешения установки устройства, вход задания режима которого соединен с управляющими входами первого и второго коммутаторов, установочные входы регистров соединены с входом ввода аргумента устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 732837, кл. G Об F 1/02, 1980. 2.Смолов В.Б. Функциональные преобразователи информации, Л., Энергоиздат, 1981, с. 176, рис.З- (прототип) .

И

11

а

««инмвм

Авторы

Даты

1983-02-23—Публикация

1981-07-17—Подача