лителяу первые входы каждого S-ro, разряда (,,... ,2+-i)( 3 +2)-го

сумматора-вычитателя подключены к .нулевой шине устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления суммы квадратов К @ -разрядных чисел | 1981 |

|

SU993256A1 |

| Устройство для извлечения корняТРЕТьЕй СТЕпЕНи | 1979 |

|

SU842803A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU805336A1 |

| Устройство для возведения п-разрядных чисел в квадрат | 1979 |

|

SU911520A1 |

| Устройство для вычисления корней квадратного уравнения | 1980 |

|

SU999060A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Однородная вычислительная структура для @ разложения матриц | 1984 |

|

SU1249531A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

Изобретение относится к вычислительной технике и может быть приме+не но в качестве спецпроцессора в комплексе с Цифровой вычислительной машиной для оперативного вычисления экспоненциальной функции.

Известно устройство, содержащее три регистра, регистр адреса, вычитатель, сумматор и блок памяти, выход которого соединен с вторым входом второго и третьего регистров, вход блока памяти соединен с выходом регистра адреса, а выходы второго и третьего регистров подключены со. ответственно к первому и второму входам сумматора, соединенного своим выходом с входом второго и третье)го регистров и выходом устройства tl 3

Недостатками известного устройст ва являются низкое быстродействие .из-за последовательной организации вычислений и относительная сложность управлений вычислительным процессом, так как в устройстве реализуется считывание информации из блока памяти и запись .информации.

Наиболее близким к изобретению по технической сущности является устройство для вычисления экспоненциальной функции, содержащее блок сдвига, накопительные регистры, блок односторонней памяти, ч. сумматора-вычитателя, блок управления, блок определения знака и элементы И, причем информационные ёходы блока сдвига соединены с информационными выходами накопительного регистра, выходы блока сдвига соединены с первым и вторым входами четвертого сумматора вь(читателя, третий вход которого соединен с выходом блока определения знака 2 .

Недостатками известного устройстаа являются отнрсительно низкое быстродействие, определяемое тем, что результат вычисления определяет ся за (.У итерацию, а также относительная сложность управления вычислительным процессом из-за необходимости использования блока памяти.

Целью изобретения является повышение быстродействия.

: .

Указанная цель достигается тем,

что в матричный вычислитель экспоненты, содержащий четыре сумматора-вычитателя и экспоненты И, дополнительно введены группа элементов И, (И -) сумматоров-вычитателей, где ji - число разрядов входного слова и и матриц -элементов И, причем выход ч-го элемента И (4 1, 2,...,и ) первого

столбца матрицы и выход К-го элемента И (к 1, 2,...,Ин-1) (:)+ 1)-го столбца j 1, 2,. ..,иJ матрицы соединены соответственно с первыми входами (2 -(-О-го и (1 -и + р-го разрядов

первого и (J -«-1)-го сумма торов-вычитателей соответственно, первый выход каждого разряда j-го сумматора-вЫчитателя подключен к второму входу соответствующего разряда (J+ 1/-ГО

сумматора-вычитателя, первый вход К-го элемента И (-j+l)-го столбца матрицы соединен с первым выходом К-го разряда j-ro сумматора-вычитателя, второй и третий входы каждого {.+2)-го

разряда первого сумматора-вычитателя подключены соответственно к выходу i-ro элемента И группы и -му разряду входа вычислителя, второй выход (1-1- 2)-го разряда j-ro сумматора-вычитателя соединен с третьим

входом соответствующего разряда

(j+ 1)-го сумматора-вычитателя, пер-, вый выходперенЛа-третьего разряда которого Подключен к вторым входам Элементов И матрицы j-ro столбца,

четвертые входы всех К разрядов 3 KJ И +2 каждбго j -го сумматора-вычитателя сформированы в четыре группы,.входы первой из которых не.посредственно, а входы второй через

инверторы подключены к нулевой шине устройства, входы третьей группы непосредственно, а входы четвертой через инверторы соединены с первым

выходом переноса третьего разряда (j-l)-ro сумматора-вычитателя, первые входы элементов И группы объединены и подключены к первому выходу переноса третьего разряда первого сумматора-вычитателя, выход переноса второго разряда которого соединен с первым входом первого разряда второго сумматора-вычитателя, вторые входы элементов И группы и первые входы элементов И первого столбца матрицы сформированы в две группы, BXdды первой из которых непосредственно а входы второй группы через инверторы подключены к нулевой шине устройства, инверсный.вход второго разряда первого сумматора-вычитателя подключены к нулевой шине устройства, выходы И -го сумматора-вычитателя являются разрядными выходами вычислителя, первые входы каждого -,го разряда (9 3, ,..., 2 +j)(j+ 2)-го сум- л матора-вычитателя подключены к нулевой шине устрой.ства.

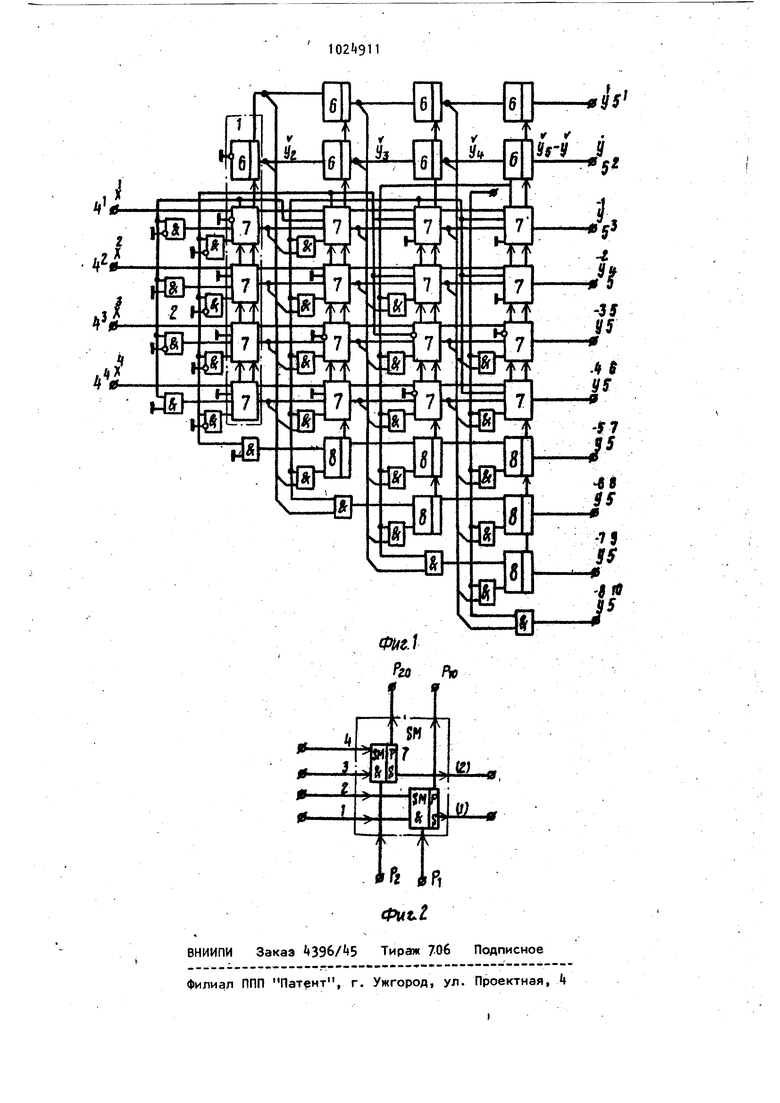

На фиг. 1 представлена схема матричного вычислителя экспоненты для случа-я, когда Vi ; на фиг. 2 схема К-го разряда 3 Ki5H +2/j-ro сумматора-вычитателя j 1, 2,...,И.

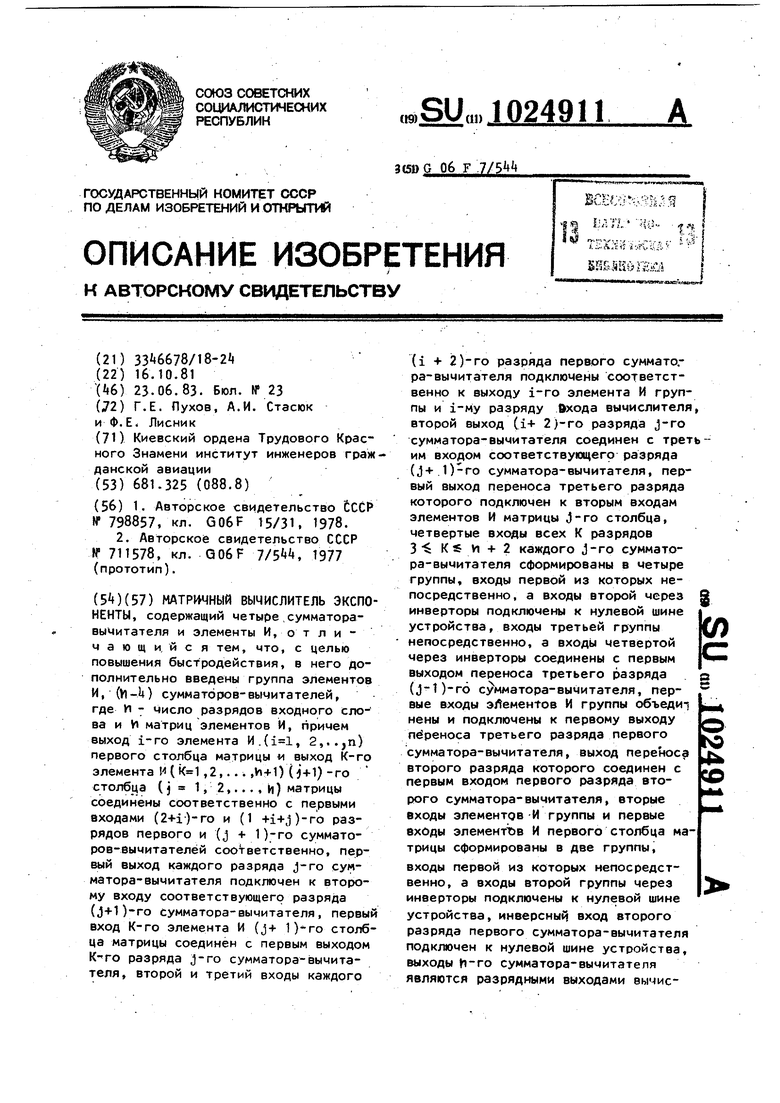

Матричный вычислитель экспоненты (фиг, 1) содержит У сумматоров-вычитателей 1, группу 2 элементов И, ма трицу элементов ИЗ, входную шину () 1, 2,. .. , VI) и выходную шину 5(Е 1, 2,..., 2к1+2). Первый сумматор-вычитатель 1 выполнен в виде последовательно соединенных полусумматора 6 и и одноразрядных сумматоров 7. Каждый (+1)-ый сумматорвычитатель 1 (| 1, 2,..,И выпол;нен в виде последовательно соединенных двух полусумматоров 6, Vi одноразрядных сумматоров 7 и j одноразрядных сумматоров на три входа 8. Групni 2 элементов И выполнена из И двухвходовых элементов И 3. Матрица элементов И 3 выполнена в виде Vi столбцов по Ли + l) и VI +2) элемента И 3 в первом и j +1)-ом столбцах соответственно, причем каждый (+4)- ый столбец сдвинут на один разряд вниз относительно (-i+lj-ro. Каждый одноразрядный сумматор 7 (фиг. 2) го сумматора-вычитателя выполнен например, в виде двух одноразрядных Сумматоров на три входа 8, первый и второй входы первого и второго являются соответственно первым, вторым, третьим и четвертым входами

одноразрядного сумматора 7. Выходы первого и второго одноразрядных сумматоров на три входа 8 одноразрядного сумматора 7 являются соответственно первь1м и вторым выходами одноразрядного сумматора 7 первым выходом переноса которого является выход переноса второго одноразрядного сумматора на три входа 8.

Матричный вычислитель экспоненты работает следующим образдм.

Функция е, О « Х5 представ.ляется в виде

gXi+Xa --- XM gX gXx gX«

где lev .5;

Х2 ln(l+2-)0,lt05lv65; Х, ln(l+2-)0,223lU3; Х 1п(1+2)0,11Т783, Хс ln(l+2-)0.0602U; Хц ln(l+2-t M; ,3,...n, ли соответственно

. рО,в ей .-) Еи(+2.-)

.,:-; -e°(.rt..

...И.).(i)

Для вычисления -у по выражению (2) определяют ненулевые значения X; (i 1, 2,.,, ,j )как

1 Уч .

.

Г&Г- «1-; 1Н/й,...,1, (г)

Ф

где g.

Xj .7/01

, U)

.-Х i

W1 i iи.

(5)

На основании выражений (3) - (5 ) значение определяется по выражению

50

, (6

- --%M- i - i,Vl,

где ,

55, и в соотствии с выражениями (3) и ( t) вычисляется на основании зависимости

-V

. ч |о 10 а. ,,64872tn/3a х,/0и - V( . Пример. Х 0,6875i Y 10.874 1,98873. 1 1; Х-х.,б875,- 0,5 0,1875 Х -7 о; Е, Y,, i,6U8721. i 2; х, - Х2 0,1875 - 0, 0,2179б5 г ± Qi 0; Y Y 1,. i 3; Xi - Хз 0, - 0,22311 3- 0,182322 Xj-,. xl + Xa - 0,217965 + 0,182322 - 0,03561 3 X 0; Е,-ХЗ; d O; Y, Yj 1,. 1 Xj - Хд 0,223ll 3 - 0,117783 О 1П53бО Е I4 4 4 Хо + Х4 - 0,03561 3 + 0,105360 0,069717 Xj 7 О 1 Ч Ъ 1,6W721 + .1, 1,. i 5; Х - Xg - 0,069717 - 0 06062Ц: 0,009093 Xj О; Е 1; Y Y Y4 1, + 2 , 1, 97873. Поскольку при организации вычисл Н+1Й в соответствии с выражениями (З) - (7 необходимо использовать постоянныезначения X; или Х которые при каждой -ой реализации выражения ( 3 ) соответственно либр вычитаются из , либо складываЮТСЯ с X- , то для их фОрМИрОВания запишем в двоичной системе счис ления при И 4 в дополнительном коде и хУ в прямом коде X,.-Ot10,- Х OOIH i X4 0001i x -j -foio ; jcl i-foi i 4 -f-f-jii Xi - OO-tOi XV - 00-11 i yfj, 0010. Ha основании выражений (8) и (f) формируемое значение из которого образуется X; либо х- , в зависи , г-, п мости от значения dL-.(T) может быть g ии о в,« « w0 J I Txi-v -j ± X. )С-5,-Л.о4.2.о-211|Л4-°-зл - 1 уф Таким образом, двоичные разряды Xt, из котораго образуется Х либо Х| , условно делятся на четыре пруппы: к первой группе относятся разряды, принимающие нулевое значение Оу |1 в X и , к второй группе относятся разряды, принимающие единичное значение в и Х- , а к третьей и четвертой группе относятся разряды, принимающие соответственно значения и оС по выражению ( 7) Работа предлагаемого устройства происходит следующим образом. . На входную шину k т.е. на и разрядов ее , Л ,..., , подаются соответственно значения разрядов X , Х,..., X значения X. При этом следует отметить, что автоматически на .вход полусумматора 6 первого . сумматора-вычитателя 1 подается единица и на вторые входы элементов ИЗ группы 2 подается значение 0,648721 (т.е. фактически подается У 1, или в двоичной системе - счисления 1,1010. Входы элементов И ИЗ группы 2, на которые подаются единичные сигналы упомянутого кода относятся к второй/группе входов, они выполнены в виде инверсных и подключены к нулевой шине устройства, подключенной к входам элементов ИЗ группы 2, на которые подаются нулевые сигналы двоичного кода). На первые входы элементов И 3 первой группы матрицы подается значение 2- 1.6t8721 илиО.ПОЮ и на четвертые входы одноразрядных сумматоров 7 первого сумматора-вычитателя 1 подается значение Х 0,5 или Х 0,1000. В устройстве происходит переходный процесс, после окончания которого в первом сумматоре- вычитателе 1 реализуется выражение СЗ) т.е. на вторых выходах ««ик,с vjy , -.«. « «.М«л .л ° образуется значение Х-Х,Х;, а на первом выходе переноса одноразрядного сумматора 7 третьего разряда его по выражению (7 образуется значение oi . Значение oLjf поступает на первые входы элементов И 3 группы 2 и тем самым разрешает поступление значения У- на вторые входы одноразрядных сумматоров 7 первого сумматора у----квычитателя 1, кроме того е посту ь -ч j д четвертые входы второго сумматора- вычитателя 1, благодаря чему в нем по выражению (9) Формируется

значение X. Во втором сумматоре-вычитателе 1 реализуются выражения (3) {), т.е. Х -Е i X,/, а на первом выходе переноса третьего разряда его по выражению {7) образуется значениечз, поступающее на вторые входы элементов И 3 первого столбца матрицы, благодаря чему значение У поступает на первые входы одноразрядных сумматоров 7 первого сумматора-вычитателя 1, а на первых выходах его по выражению 6 образует ся значение У + .yi. Кроме того, oi поступает на. четвертые входы одноразрядного сумматора-выг читателя 1 в котором формируется по выражению (9) Xj. реализуется выражение (3) и ( ), на вторых выходах, его образуется значение Х L ) первом выходе переноса третьего разряда его по вы.ражению (7) образуется0 4,. Значениео у поступает на вторые входы элементов И 3 второго столбца матрицы, благодаря чему значение (,У поступает на первые входы одноразрядных сумматоров 7 второго сумматора-вы- . читателя t, в котором реализуется выражение (6, и на первых выходах его образуется значение У ..

Аналогичным образом на четвертые входы одноразрядных сумматоров 7 каждого i-ro сумма тора-вычитателя 1 поступает значение , в котором по выражению (9) формируется xf, реализуются выражения (3) и (, на вторых выходах образуется значение . X jj ,j - , а на первом выходе

переноса третьего разряда его по выражению (7) образуетсяoij. Это значение d. поступает на вторые входы элементов И 3 ( i -Ото столбца матрицы, разрешая тем самым поступление значения У,- на первые входы одноразрядных сумматоров 7( 4-1)-го сумматора-вычитателя 1, на первых выходах которых по выражению (6) образуется значение

+ ,-. . И,наконец по аналогии с описанным, на первых выходах одноразрядных сумматоров 7 последнего сумматора-вычитателя 1 и соответственно, на выходной шине 5 образуется по выражению 6 искомое значение

г.

Чи-1)

У УИ .,,Технико-экономическая эффективность заключается в том, что в устройстве результат вычислений получается за время переходного процесса в схеме, которое практически равно времени задержки сигнала между в входом и выходом устройства.

Кроме того, в предлагаемом устройстве не. используется управленческая информация и блок памяти, а вычислительный процесс начинается с момента подачи на входную шину исходной информации 5t. Эти факты способствуют применению устройства для реализации вычислительного процесса в натуральном масштабе времени, например, управления технологическими процессами или динамическими объектами в режиме их нормального функционирования Л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления экспоненты | 1978 |

|

SU798857A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-23—Публикация

1981-10-16—Подача