дои декады соединен с выходом переноса своей декады, выход второй схемы И сое- диней с первым входом схемы ИЛИ следующей декады, вторые входы всех вторых схем И соединены с шиной сложения, выход вентиля вычитания соединен со входами опроса с-хем выявления нулевого состояния декад, установочные входы триггера соединены с выходом задё зжанного девятого импульса блока формирования.

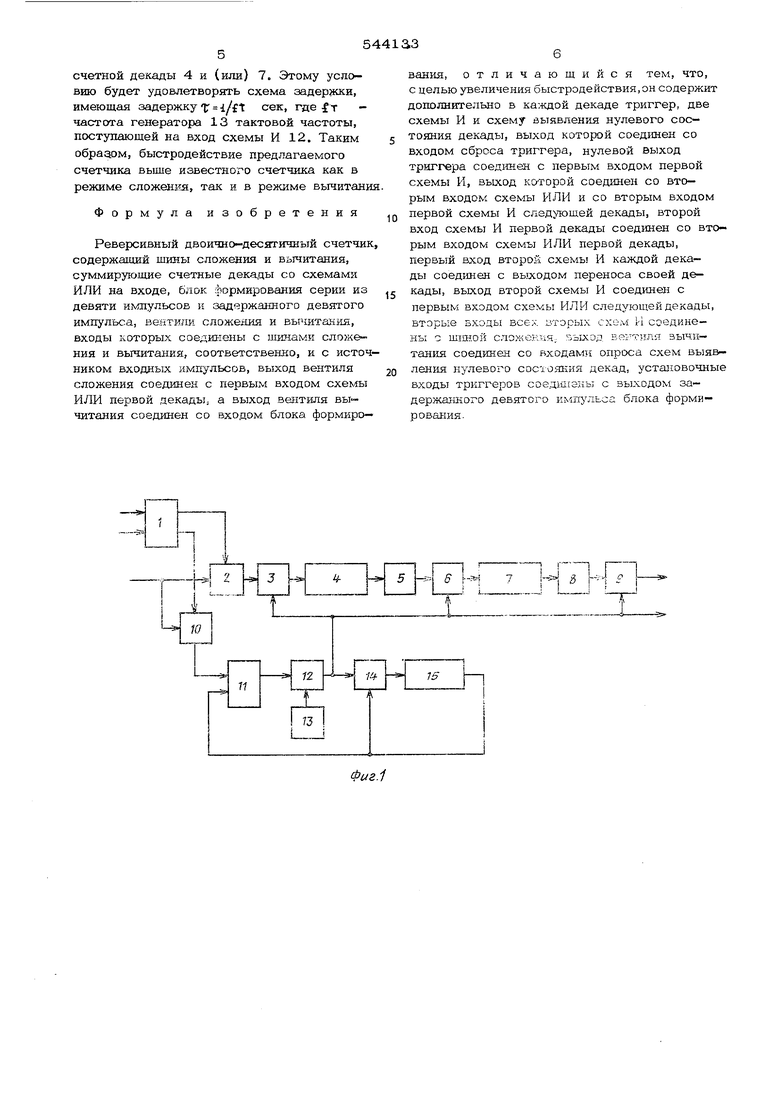

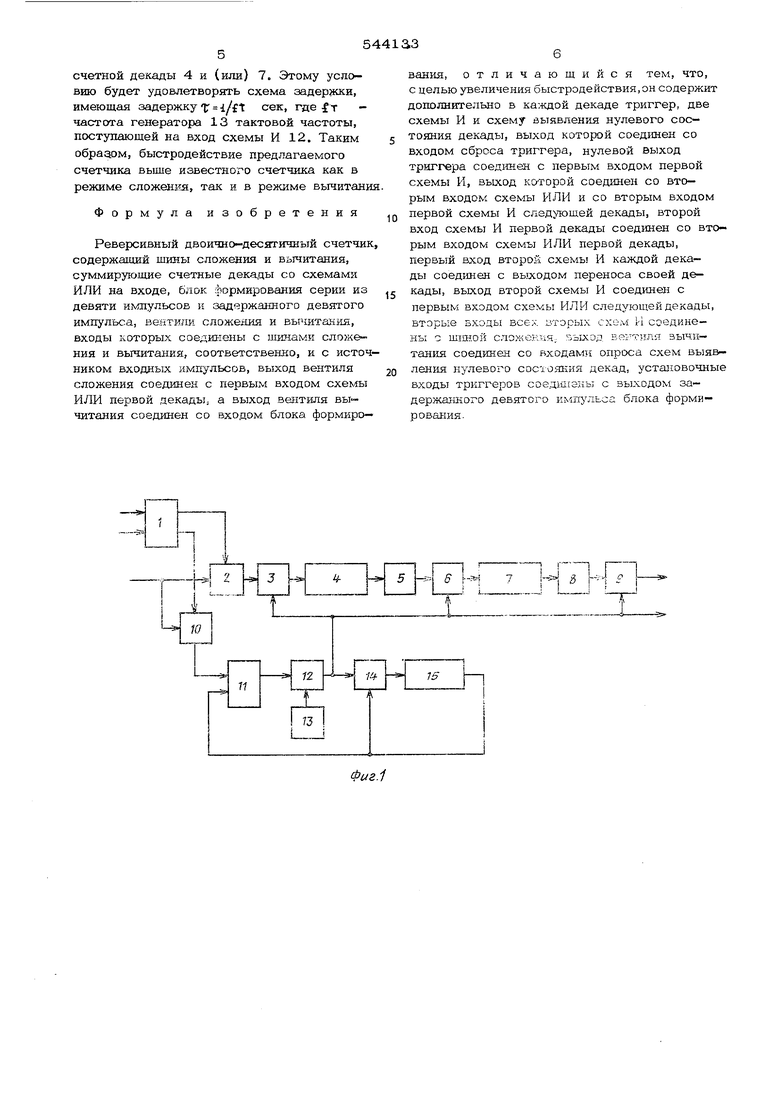

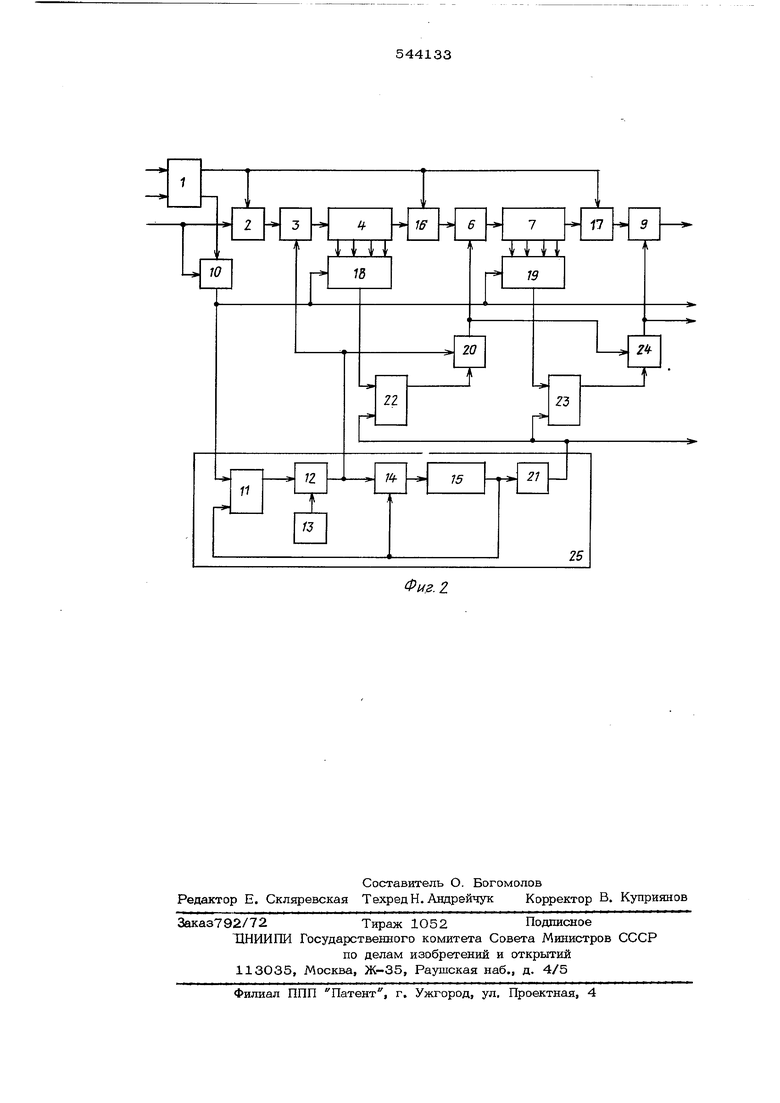

На фиг. 1 изображена схема известного счетчика на фиг, 2 - схема предлагаемого счетчика.

Схема реверсивного двоично-десятичного счетчика включает в себя триггер 1 с раздельными входами, логическую схему И 2, логическую схему ИЛИ 3, счетную декаду 4, схему задержки 5, логическую схему ИЛ 6, счетную декаду 7, схему задержки 8, логическую схему ИЛИ 9, логическую схему И 10, триггер 11 с раздельными входами, логическую схему И 12, генератор тактовый частоты 13, логическую схему ИЛИ 14, счетную декаду 15, логическую схему И 16 и 17, дешифратор нуля 18 и 19, логическую схему И 20, схему задержки 21, триггеры с раздельными входами 22 и 23, логическую схему И 24, схему формирования 25 девяти импульсов с двумя выходами.

Схема работает следующим образом. После команды Сложение триггер 1 устанавливает логическую единицу на входах схем И 2, 16, 17. Поступающие на счетчи счетные импульсы через логическую схему И 2 и схему ИЛИ 3 поступают на вход счетной декады 4.

Возникающие импульсы переполнения с выхода счетной декады 4 через схему И 16 и схему ИЛИ 6 сразу же поступают на вход второй счетной декады , Аналогично импульсы переноса с выхода счетной декады 7 через схему 17 и схему ИЛИ 9 сразу же поступают на вход следующей счетной декады. При приходе команды Вычитание триггер 1 установит логическую единицу на входе схемы И 10 и логический нуль на входах схем И 2, 16, 17. При этом связь между счетными декадами 4 и 7 разрывается. Счетный импульс через схему И 10 поступает на вход схемы формирования 25, устанавливая триггер 11 в состояние, при котором через схему И 12 начинают проходить импульсы от генератора тактовый частоты 13, превышающей частоту входных сигналов на порядок. Одновременно счетный импульс с выхода схемы И 10 поступает на входы схем дешифратора нуля 18 и 19. При этом, если содержимое счетной декады 4 и (или) 7 равно нулю, импульс с выхода схемы И 1О пройдет через соответствующую схему дешифратора нуля 18 и (или) 19 на вход соответствующего триггера 22 и (или) 23, устанавливая их в нулевое состояние, при котором на вход схем И 20 и (или) 24 поступает логическая единица. Импульсы с выхода схемы И 12 через схему ИЛИ 14 поступают в счетную декаду 15, в которой всегда записан начальный код единица. При поступлении в декаду девяти импульсов на ее выходе появляется импульс переполнения, сбрасывающий триггер 11 управления в состояние нуль и через схему ИЛИ 14, устанавливающий начальный код в декаде единицу.

С выхода схемы И 12 серия из девяти импульсов поступает через схему ИЛИ 3 на вход первой декады, а также на вход схемы И 2О. При этом, если триггер 22 находится в нулевом состоянии, что говорит о том, что перед вычитанием содержимое счетной декады 4 равнялось нулю, то девять импульсов пройдут через схему И 20, и схему ИЛИ 6 на вход счетной декады 7. Аналогично, если перед вычитанием содержимое счетной декады 7 равнялось ну.шо, о чем будет говорить нулевое состояние триггера 23, девять импульсов схемы И 24 и схемы ИЛИ 9 поступят на вход следующей счетной декады. Поступление девяти импульсов в счетную декаду равносильно вычитанию единицы из содержимого счетной декады. Если же перед вычитанием содержимое младшей счетной декады отличалось от нуля, то девят импульсов не пройдут на вход второй и последующих декад, независимо от того, были более старшие счетные декады в нулевом состо5шии перед вычитанием или нет. Воэникаюшие импульсы переноса с выхода счетных декад не проходят на вход следующих декад, так как в режиме вычитания счетные декады работают независимо, поскольку на схемы И 2, 16, 17 с триггера управления поступает логический нуль. Процесс вычитания в счетных декадах заканчивается сразу же с приходом девятого импульса. Для того, чтобы схему подготовить к вычитанию следующей единицы из содержимого счетчика, служит схема задержки 21. Импульс иереполнелия, соответствующий девятому импульсу, с выхода счетной декады 15, входящей в состав схемы формирования 25 серии из дев5гги импульсов, поступает на вход схемы задержки 21, с выхода которой задержанный импульс поступает на единичные входы триггеров 22, 23, устанавливая их в исходное состояние. Время схемы задержки выбирают из условий надежного прохождения девятого импульса на вход со.ответствуклцие счетной 4 и (или) 7. Этому условию будет удовлетворять схема задер кки, имеющая задержку f i/ft сек, iTie f т частота генератора 13 тактовой частоты, поступающей на вход схемы И 12. Таким образом, быстродействие предлагаемого счетчика выще известного счетчика как в режиме сложения, так и в режиме вычитан Формула изобретения Реверсивный двоично-десятичный счетчи содержащий шины сложения и вычитания, суммируюшие счетные декады со схемами ИЛИ на входе, блок гЬормирования серии из девяти импульсов и задержанного девятого импульса, вентили сложения и вычитания, входы которых соединены с шинами сложения и вытаитания, соответственно, и с источ ником входных импульсов, выход вентиля сложения соединен с первым входом схемы ИЛИ первой декады а выход вентиля вычитания соединен со входом блока формирования, отличающийся тем, что, с целью увеличения быстродействия, он содержит дополнительно в ка;«дой декаде триггер, две схемы И и схему выявления нулевого сое- тояиия декады, выход которой соединен со входом сброса триггера, нулевой выход триггера соединен с первым входом первой схемы И, выход которой соединен со вторым входом схемы ИЛИ и со вторым входом первой схемы И следующей декады, второй вход схемы И первой декады соединен со вторым входом схемы ИЛИ первой декады, первый вход второй схемы И каждой декады соединен с выходом переноса своей декады, выход второй схемы И соединен с первым входом схемы ИЛИ следующей декады, вторые входы всех, вторых схем И соединены с Ш1ШОЙ сложения.: выход вегтипя вычитания соединен со входами опроса схем выявления нулевого состояния декад, установочные входы триггеров соедш1эны с выходом задержанного девятого импульса блока формирования

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный двоично-десятичный счетчик импульсов | 1975 |

|

SU572934A2 |

| Десятичный реверсивный счетчик с цифровой индикацией | 1985 |

|

SU1279062A1 |

| Разностный счетчик импульсов | 1980 |

|

SU936433A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1451857A1 |

| Устройство для ввода информации | 1976 |

|

SU638948A1 |

| Реверсивный декадный счетчик импульсов | 1976 |

|

SU603126A1 |

| ЭЛЕКТРОННЫЙ ПРИБОР ДЛЯ ОПРЕДЕЛЕНИЯ СКОРОСТИ, ПРОЙДЕННОГО РАССТОЯНИЯ И ВРЕМЕНИ | 1965 |

|

SU170776A1 |

| Счетное устройство | 1984 |

|

SU1210221A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Пересчетное устройство | 1982 |

|

SU1046935A1 |

Л

in

Авторы

Даты

1977-01-25—Публикация

1974-03-26—Подача