кода, а выходы кодов, соответствующих пяти, девяти и нулю, соединены с первьин входами соответственно первого, второго и третьего элементе совпадения, первый вход третьего элемента совпадения соединен с первым входом четвертого элемента совпа дения, второй вход которого является входом управления реверсом корректора кода и соединен с вторым входом третьего элемента совпадения и инверсными вторыми входами первого и второго элементов совпадения, третьи и четвертые входы первого и третьего элементов совпадения соединены в корректоре кода счетчика соответственно с входом выбора модуля и входом синхронизации, выходы первого, второго, третьего и четвертого элементов совпадения соединены с входами шифратора двоичного кода, информационные выходы и выход перено са которого являются информационными выходами и выходом переноса корректора кода, синхронизатор переносов содержит четыре элемента И, элемент ИЛИ и два Б -триггера., первые входы первого и второго элементов И являются соответственно входом переноса и входом синхронизации синхронизатора переносов, выход и второй .вход первого элемента И соединены с первым входом элемента ИЛИ и

)Прямым выходом первого D -триггера,, который является вькодом разрешения

счета синхронизатора переносов , так-- товый вход которого соединен с перИзобретение относится к измерительной и вычислительной технике и предназначено для использования в- , технических средствах, принцип действия которых основан на подсчете количества импульсов, таких как электронные счетчики, таймеры, частотомеры, тахометры .и т.д.

Цель изобретения - повьппение быстродействия и расширение ф-ункцио- нальиых возможностей счетного устрой

,U221

вым входом третьего элемента И и тактовым входом первого D -триггера, 15-вход которого соединен с выходом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и вторым входом третьего элемента И, выход которого соединен с тактовым входом второго D -триггера, D -вход, прямой выход и вход установки которого соединены соответственно с шиной нулевого логического сигнала, вторым входом второго элемента И и выходом четвертого элемента И, первый и второй входы которого являются дополнительным входом переноса и выходом разрешения счета, синхронизатор счетных импульсов содержит первый и второй триггеры задержки, элемент запрета и вспомогательный элемент . ИЛИ, выход которого является выходом разрешения счета синхронизатора счетных импульсов ., тактовый вход которого соединен с тактовыми входами первого и второго триггеров задержки, прямые выходы которых соединены соответст венно с прямым и инверсным входами элемента запрета,выход которого соединен с первым входом вспомогательного элемента ИЛИ,второй вход которого соединен с входом разрешения, непрерьшного счета синхронизатора счетных импульсов, вход счетных импульсов которого соединен с Л - входом первого триггера задержки, прямой выход которого соединен с D - входом второго триггера за- . держки.

ства за счет обеспечения реверсивного счета по выбираемому модулю счета.

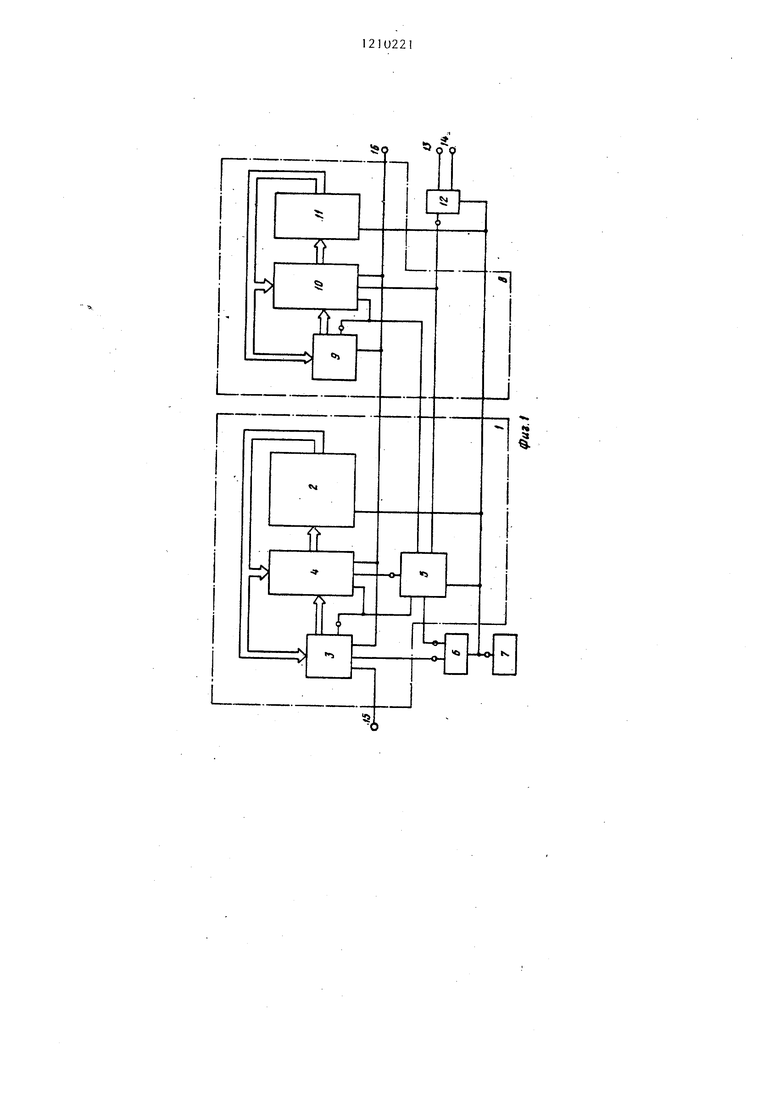

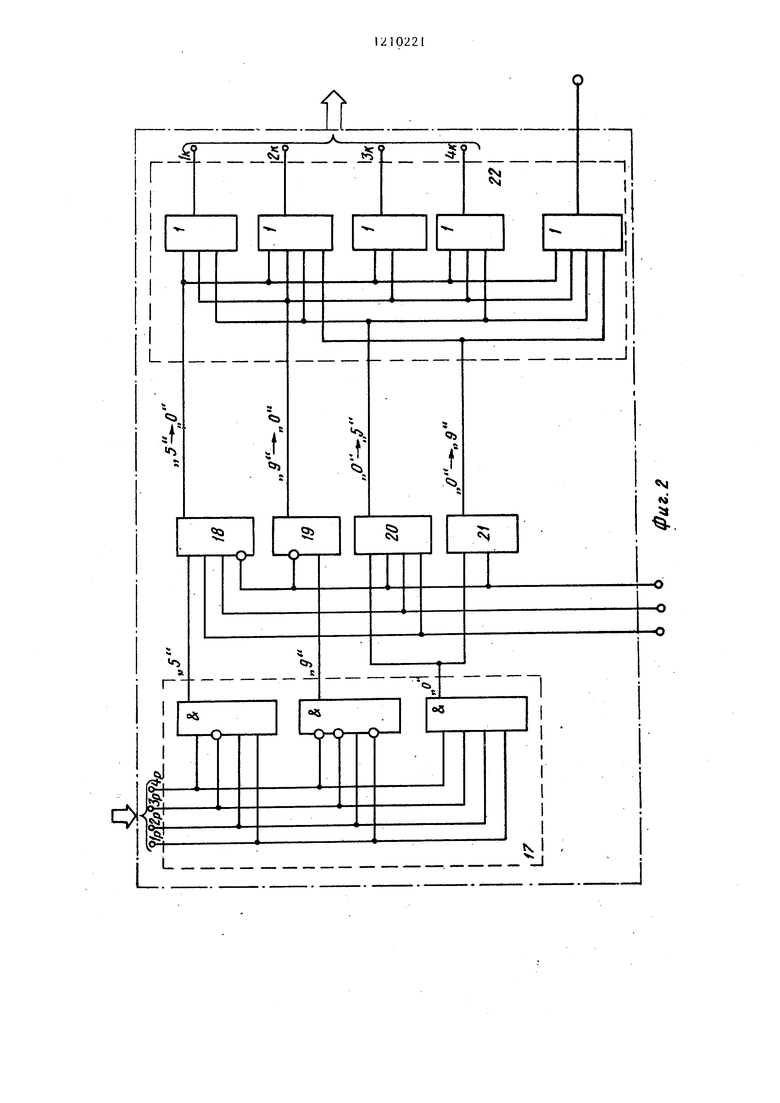

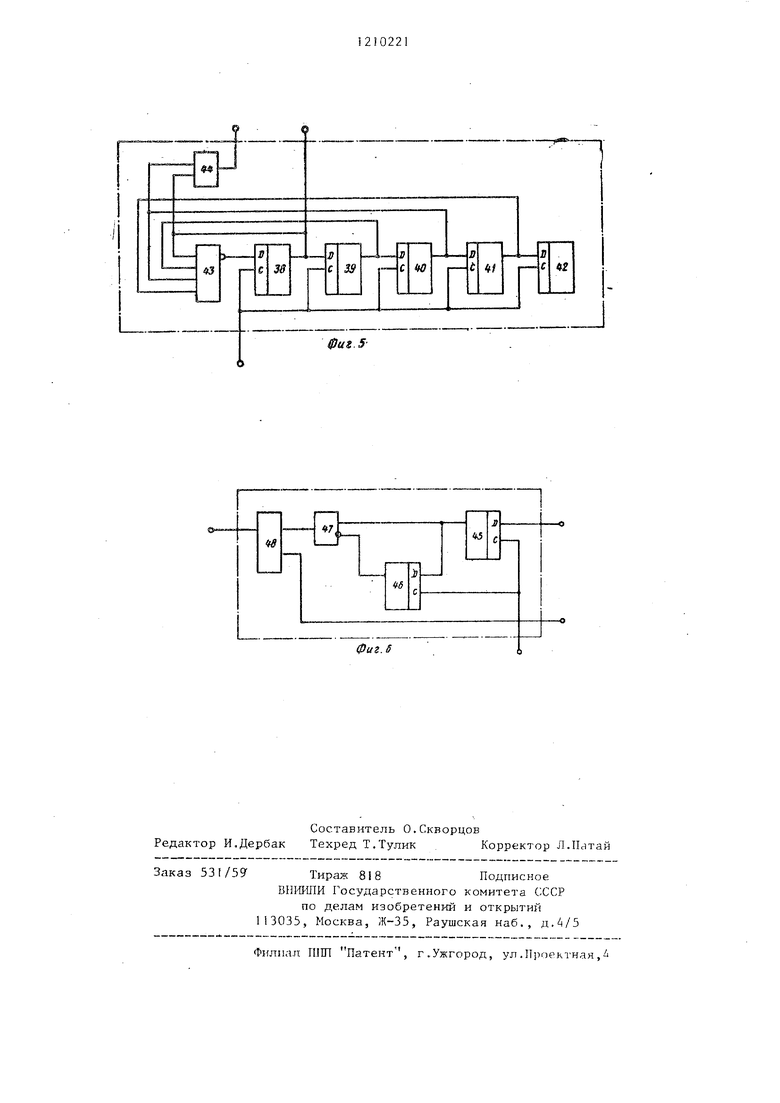

На фиг.1 показана функциональная схема устройства; на фиг.2 - структурная схема корректора кода; на фиг,3 - пример структурной схемы суг гматора; на фиг.4 - структурная схема синхронизатора переносов; на фиг.5 - пример схемной реализации Счетчика синхронизации; на фиг.6 3

структурная схема синхронизатора счетных импульсов.

Счетное устройство содержит счетчик 1, включающий регистр 2, корректор 3 кода, сумматор 4 и синхронизатор 5 переносов ,вход переноса которого соединен с выходом переноса корректора ;з кода, информационный вход которого соединен с первым информационным входом сумматора 4 и выходом регистра 2, информационный вход которого соединен с выходом сумматора 4, а вход синхронизации корректора 3 кода соединен с выходом счетчика 6 синхронизации, вход которого соединен с выходом генератора 7 тактов, а также счетчик 8 младшей декады, содержащий корректор 9 кода, сумматор 10 и регистр 11, информационньй выход которого соединен с информационным входом корректора 9 кода счетчика младшей декады и первым информационным входом сумматора 10 счетчика младшей декады, информационный вход и выход которого соединены с информационным выходом и информационным входо соответственно корректора 9 кода и регистра 1 1 счетчика младшей декады,а также синхронизатор счетных импульсов 1 2, первый и второй входы которого соединены соответственно с входом 13 счетных импульсов и входом 14 разрешения непрерьшного счета счетного устройства, вход 15 выбора модуля счета которого соединен с входом выбора модуля счета корректора 3 счетчика, вход управления реверсом которого соединен с входами управления реверсом сумматоров,счетчика 4 и счетчика младшей декады 10 и корректора 9 кода младшей декады и является входом 16 управления реверсом счетного устройства.

Выход генератора 7 тактов соеди- иен с тактовыми входами синхронизатора 5 переносов, синхронизатора 12 счетных импульсов и регистров счетчика 2 и счетчика младшей декады I1, дополнительный выход счетчика 6 синхронизации соединен с входом синхронизации синхронизатора 5 переносов, выход синхронизатора 12 счетных импульсов соединен с входами разрешения счета сумматора 10 счетчика младшей декады и синхронизатора 5 переноса, выход разрешения счета которого соединен с входом разрешения счета-сумматора 4 счетчика, вход переноса которого соединен

21 - 4

с выходом переноса корректора 3 код; счетчика, дополнительньш вход переноса синхронизатора 5 переносов соединен с выходом переноса корректора 9 кода счетчика младшей декады и входом переноса сумматор.а 10 счетчика младшей декады.

Каждый корректор кода (фиг.2) содержит дешифратор 17, входы которого

являются информационными входами корректора кода, а выходы кодов, соответствующих пяти, девяти и нулю, соединены с первыми входами соответственно первого 18, второго 19 н

третьего 2U элементов совпадения,

первый вход третьего элемента 20 совпадения соединен с первым входом четвертого элемента 21 совпадения, второй вход которого является входом

управления реверсом корректора кода и соединен с вторым входом третьего элемента 20 совпадения и инверсными вторыми входами первого 18 и второго 19 элементов совпадения, третьи

и четверть1е входы первого и третьего элементов совпадения соединены в корректоре кода счетчика соответственно с входом выбора модуля и входом синхронизации, выходы первого 18, второго 19, третьего 20 и четвертого 21 элементов совпадения соединены с входами шифратора 22 двоичного кода, информационные выходы и выход переноса которого являются информа- ционными выходами и выходом переноса корректора кода.

Структурная схема сумматоров 4 и - 10 (фиг.З) содержит четыре однотипных комбинационных схемы 23 формирования двоичных разрядов декады, управляемые сигналами счет, реверс, перенос (заем), каждая из которых состоит из вентиля 24 прямой передачи, вентиля 25 прямого счета, вентиля 26 обратного счета и вентиля 27 установки кода перехода 27. Кроме того, сумматор содержит два элемента, формирующих первый и четвертый двоичные разряды декады . при прямом 28 и обратном 29 счете,

реализующих функцию неравнозначность (сложение по модулю .

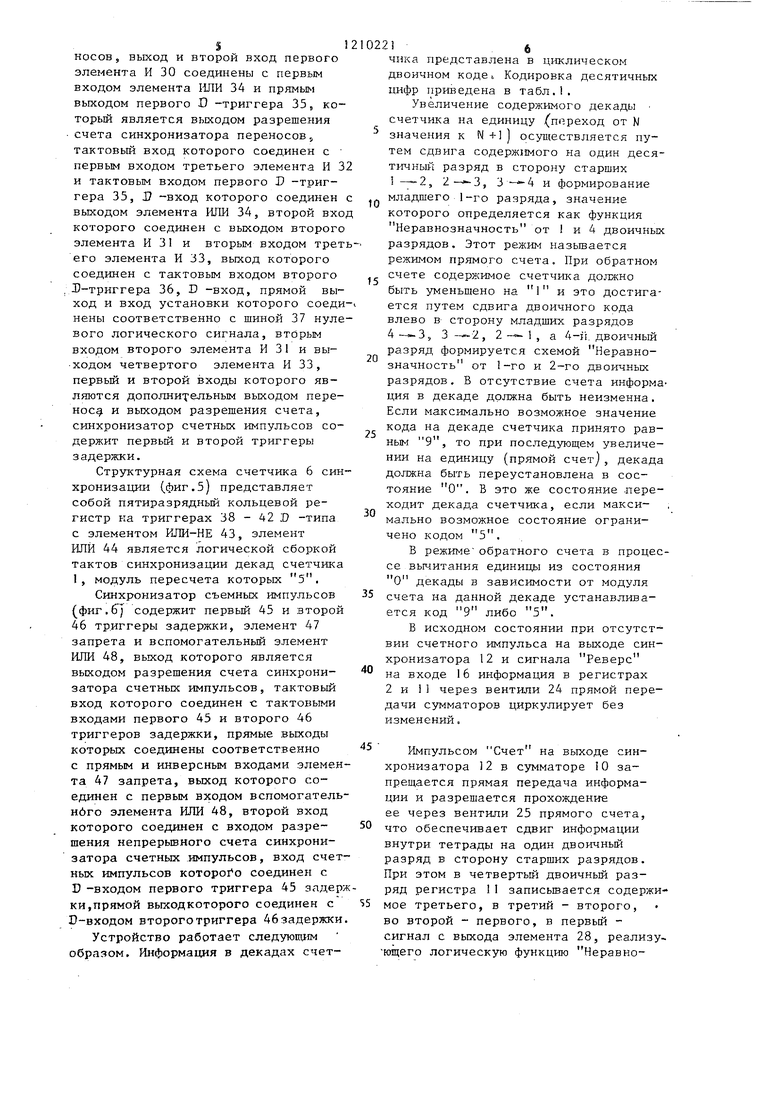

Синхронизатор переносов (фиг.4) содержит четыре элемента И 30 - 33, элемент ИЛИ 34 и два D -триггера 35

и 36, первые входы первого 30 и

второго 31 элементов И являются соответственно входом переноса и входом синхронизации синхронизатора пере

S1

носов, выход и второй вход первого элемента И 30 соединены с первым входом элемента ИЛИ 34 и прямым выходом первого Л -триггера 35 который является выходом разрешения счета синхронизатора переносов, тактовый вход которого соединен с первым входом третьего элемента И 32 и тактовым входом первого D -триггера 35, I -вход которого соединен с выходом элемента ИЛИ 34, второй вход которого соединен с выходом второго элемента И 31 и вторым входом треть его элемента И 33, выход которого соединен с тактовым входом второго D-триггера 36, D -вход, прямой выход и вход установки которого соединены соответственно с шиной 37 нулевого логического сигнала, вторым входом второго элемента И 31 и вы- ходом четвертого элемента И 33, первый и второй входы которого являются дополнительным выходом переносу и выходом разрешения счета, синхронизатор счетных импульсов содержит первый и второй триггеры задержки.

Структурная схема счетчика 6 синхронизации (фиг.5) представляет собой пятиразрядный кольцевой регистр на триггерах 38 - 42 D -типа с элементом ИЛИ-НЕ 43, элемент ИЛИ 44 является логической сборкой тактов синхронизации декад счетчика 1, модуль пересчета которых 5.

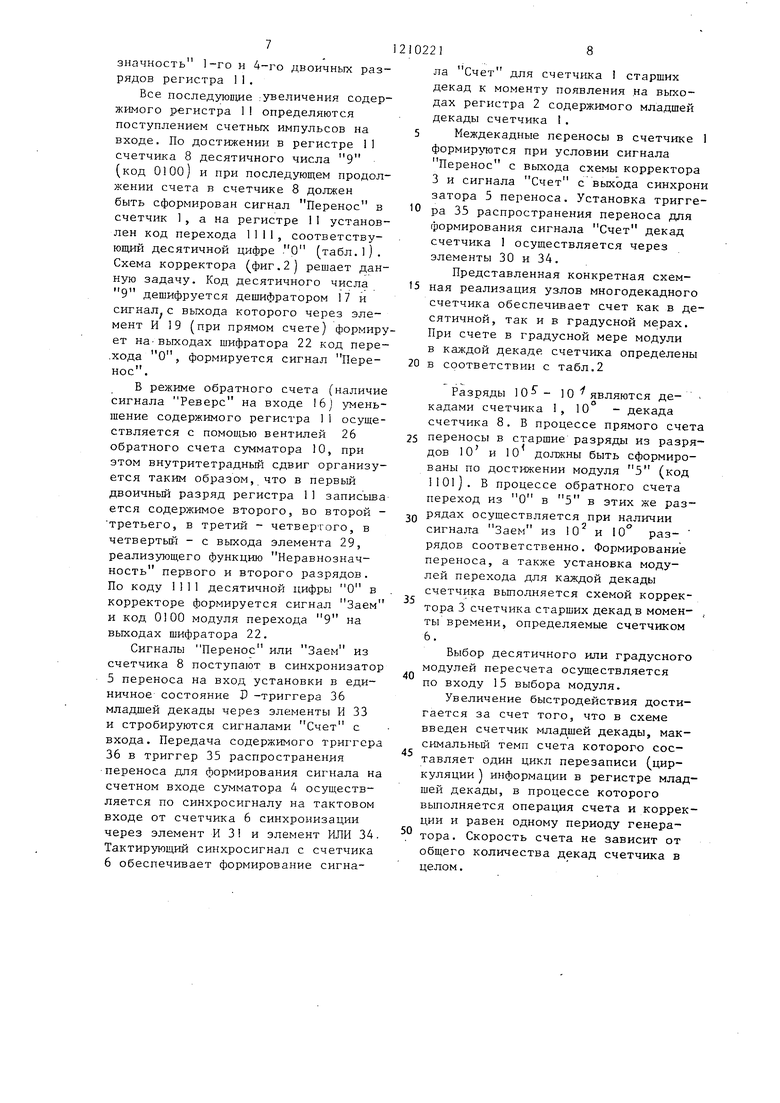

Синхронизатор съемных импульсов (фиг. содержит первый 45 и второй 46 триггеры задержки, элемент 47 запрета и вспомогательный элемент ИЛИ 48, выход которого является выходом разрешения счета синхронизатора счетных импульсов, тактовый вход которого соединен с тактовыми входами первого 45 и второго 46 триггеров задержки, прямые выходы которых соединены соответственно с прямым и инверсным входами элемента 47 запрета, выход которого соединен с первым входом вспомогатель- нбго элемента ИЛИ 48, второй вход которого соединен с входом разрешения непрерьгоного счета синхронизатора счетных импульсов, вход счетных импульсов которого соединен с D -входом первого триггера 45 задержки,прямой вьгходкоторого соединен с Г-входом второго триггера 46 задержки.

Устройство работает следующим образом. Информация в декадах счет22 ,6

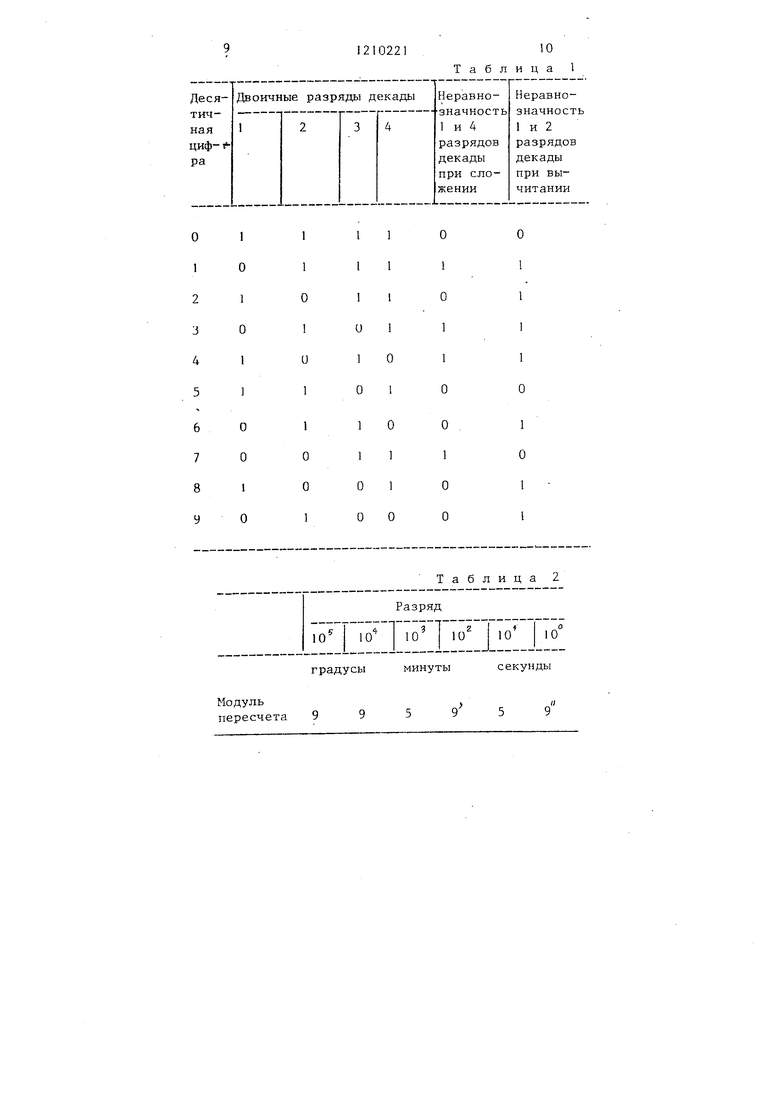

чнка представлена в циклическом двоичном кодеь Кодировка десятичных цифр приведена в табл.1.

Увеличение содержимого декады счетчика на единицу (переход от N значения к N +1 ) осуществляется путем сдвига содержимого на один десятичный разряд в сторону старших -2, 2---3, и формирование младшего 1-го разряда, значение которого определяется как функция Неравнозначность от 1 и 4 двоичных разрядов. Этот режим назьшается режимом прямого счета. При обратном счете содержимое счетчика должно

0

5

быть уменьшено на

и это достига

ется путем сдвига двоичного кода влево в сторону младших разрядов 4 --3,, 3 --2, 2 1 , а 4-1. двоичный разряд формируется схемой Неравнозначность от 1-го и 2-го двоичных разрядов. В отсутствие счета информация в декаде должна быть неизменна. Если максимально возможное значение кода на декаде счетчика принято равным 9 , то при последующем увеличении на единицу (прямой счет, декада должна быть переустановлена в состояние О. В это же состояние .переходит декада счетчика, если максимально возможное состояние ограничено кодом 5.

В режиме обратного счета в процессе вычитания единицы из состояния О декады в зависимости от модуля счета на данной декаде устанавливается код 9 либо 5.

В исходном состоянии при отсутствии счетного импульса на выходе синхронизатора 12 и сигнала Реверс на входе 16 информация в регистрах 2 и 11 через вентили 24 прямой передачи сумматоров циркулирует без изменений.

Импульсом Счет на выходе синхронизатора 12 в сумматоре 10 запрещается прямая передача информации и разрешается прохождение ее через вентили 25 прямого счета,

tjTo обеспечивает сдвиг информации внутри тетрады на один двоичный разряд в сторону старших разрядов. При этом в четвертый двоичный разряд регистра 1I записывается содержимое третьего, в третий - второго, во второй - первого, в первый - сигнал с выхода элемента 28, реализу- ющего логическую функцию Неравно7

зиачность 1-го и 4-го двоичных разрядов регистра 11.

Все последуюпще .увеличения содержимого регистра 1I определяются поступлением счетных импульсов на входе. По достижении в регистре 11 счетчика 8 десятичного числа 9 (код OlOO) и при последующем продолжении счета в счетчике 8 должен быть сформирован сигнал Перенос в счетчик 1, а на регистре 11 установлен код перехода 1111, соответствующий десятичной цифре О (табл.1). Схема корректора (фиг.2 решает данную задачу. Код десятичного числа 9 дешифруется дешифратором 17 и сигнал с выхода которого через элемент И 19 (при прямом счете) формирует на- выходах шифратора 22 код пере- .хода О, формируется сигнал Перенос.

В режиме обратного счета (наличие сигнала Реверс на входе 16) уменьшение содержимого регистра 11 осуществляется с помощью вентилей 26 обратного счета сумматора 10, при этом внутритетрадный сдвиг организуется таким образом, что в первый двоичньй разряд регистра 11 записьша ется содержимое второго, во второй - третьего, в третий - четвертого, в четвертый - с выхода элемента 29, реализующего функцию Неравнозначность первого и второго разрядов. По коду 1111 десятичной цифры О в корректоре формируется сигнал Заем и код 0100 модуля перехода 9 на выходах шифратора 22.

Сигналы Перенос или Заем из счетчика 8 поступают в синхронизатор

5переноса на вход установки в единичное состояние Р -триггера 36 младшей декады через элементы И 33 и стробируются сигналами Счет с входа. Передача содержимого триггера 36 в триггер 35 распространения переноса для формирования сигнала на счетном входе сумматора 4 осуществляется по синхросигналу на тактовом входе от счетчика 6 синхронизации через элемент И 3I и элемент ИЛИ 34 Тактирующий синхросигнал с счетчика

6обеспечивает формирование сигна2218

ла Счет для счетчика 1 старших декад к моменту появления на выходах регистра 2 содержимого младшей декады счетчика I.

5 Междекадные переносы в счетчике 1 формирчтотся при условии сигнала Перенос с выхода схемы корректора 3 и сигнала Счет с выхода синхрони затора 5 переноса. Установка тригге0 ра 35 распространения переноса для формирования сигнала Счет декад счетчика 1 осуществляется через элементы 30 и 34.

Представленная конкретная схем5 ная реализация узлов многодекадного счетчика обеспечивает счет как в десятичной, так и в градусной мерах. При счете в градусной мере модули в каждой декаде счетчика определены

0 в соответствии с табл.2

Разряды 10 являются де- кадами счетчика I, 10° - декада счетчика 8, В процессе прямого счета

5 переносы в старшие разряды из разрядов 10 и 10 должны быть сформированы по достижении модуля 5 (код 1101. В процессе обратного счета переход из О в 5 в этих же разQ рядах осуществляется при наличии сигнала Заем из 10 и 10° раз- рядов соответственно. Формирование переноса, а также установка модулей перехода для каждой декады счетчика вьтолняется схемой корректора 3 счетчика старших декад в момен- , ты времени, определяемые счетчиком 6.

Выбор десятичного или градусного модулей пересчета осуществляется по входу 15 выбора модуля.

Увеличение быстродействия достигается за счет того, что в схеме введен счетчик младшей декады, мак- симальньш темп счета которого составляет один цикл перезаписи (циркуляции ) информации в регистре млад- щей декады, в процессе которого вьтолняется операция счета и коррекции и равен одному периоду генера тора. Скорость счета не зависит от общего количества декад счетчика в целом.

5

0

do о

Фиг.З

1210221

30

3t

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННОГО ИНТЕРВАЛА | 1991 |

|

RU2040854C1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| СПОСОБ И УСТРОЙСТВО СЧЕТА ИМПУЛЬСОВ | 2015 |

|

RU2604334C2 |

| Запоминающее устройство | 1985 |

|

SU1325564A1 |

| Умножитель частоты | 1983 |

|

SU1151959A1 |

3S o

L

I

фиг.В

Составитель О.Скворцов Редактор И.Дербак Техред Т.Тулик , Корректор Л.Натай

531/59

Тираж 818Подписное

ВНШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-33, Раушская наб., д.А/5

Филиал гаш Патент , г.Ужгород, ул.Проектная,

| Шляпоберский В.И.Элементы дискретных -систем связи.- М.: Изд-во МО СССР, 1965 | |||

| Электронные цифровые часы-календарь | 1977 |

|

SU792212A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-02-07—Публикация

1984-06-06—Подача