1

Изобретение отпосится к области вычислительной техники и может быть использовано для контроля и обнаружения неисправиостей в логических элементах ЭВМ.

Известно устройство 1 для диагностики неисправностей в логических схемах, содержащее блок формирования диагностических наборов, дешифратор, блок управления, блок фиксации результатов проверок, первую и вторую группы преобразователей.

Недостатками известного устройства являются его ограниченные функциональные возможности, обусловленные тем, что оно может локализовать только неисправности типа постоянный нуль и постоянная единица.

Иаиболее близким к изобретению по технической сущности и достигаемому результату является устройство 2 для диагиостики неисправностей в логических схемах, содержащее тактовый генератор, счетчик импульсов, блок вычисления синдрома, дешифратор, элементы ИЛИ, счетчики неисправностей и блок идентификации неисправностей, пр.ичем выход тактового генератора соединен с входом счетчика имиульсов, выходы эталонной и диагностируемой логических схем соединены через блок вычисления синдрома с входами дешифратора, выходы которого через элементы ИЛИ соединены с входами счетчиков неисправностей, группы входов и индикационные

выходы блока идентификации неисправностей соединены соответственно с выходами счетчиков неисправностей ц выходами устройства, а запрещающий выход блока идентификации неисправностей соединен с входом тактового генератора.

Недостаток известного устройства состоит в том, что оно не позволяет диагностировать логические схемы «мпульсно-потенциального типа, что сужает функциопальные возмолсности устройства.

Цель изобретения - расширение функциональных возможностей устройства, а именно

обеспечение возможности диагиостики неисправностей логических схем импульсно-потенциального типа.

Поставленная цель достигается тем, что устройство содержит коммутатор, элементы

И и дополнительный генератор импульсов, причем первая и вторая группы входов коммутатора соединены соответственно с входом устройства и с выходом дополнительного генератора импульсов, входы которого соедийены с выходом генератора тактовых импульсов и с запрещающим выходом блока идентификации неисправностей, выходы счетчика импульсов и выходы коммутатора соединены соответственно с первыми и вторыми входами элементов И, а выход каждого элемента

И соединен с соответствующим входом эталонной и проверяемой логических схем,

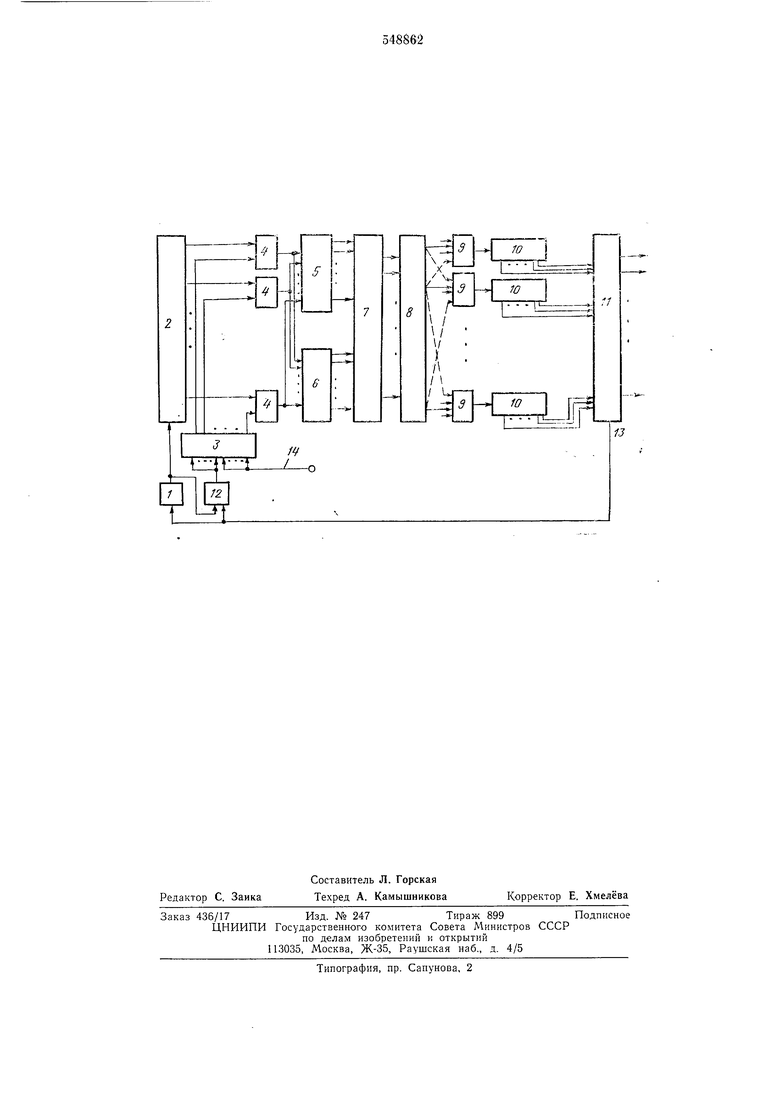

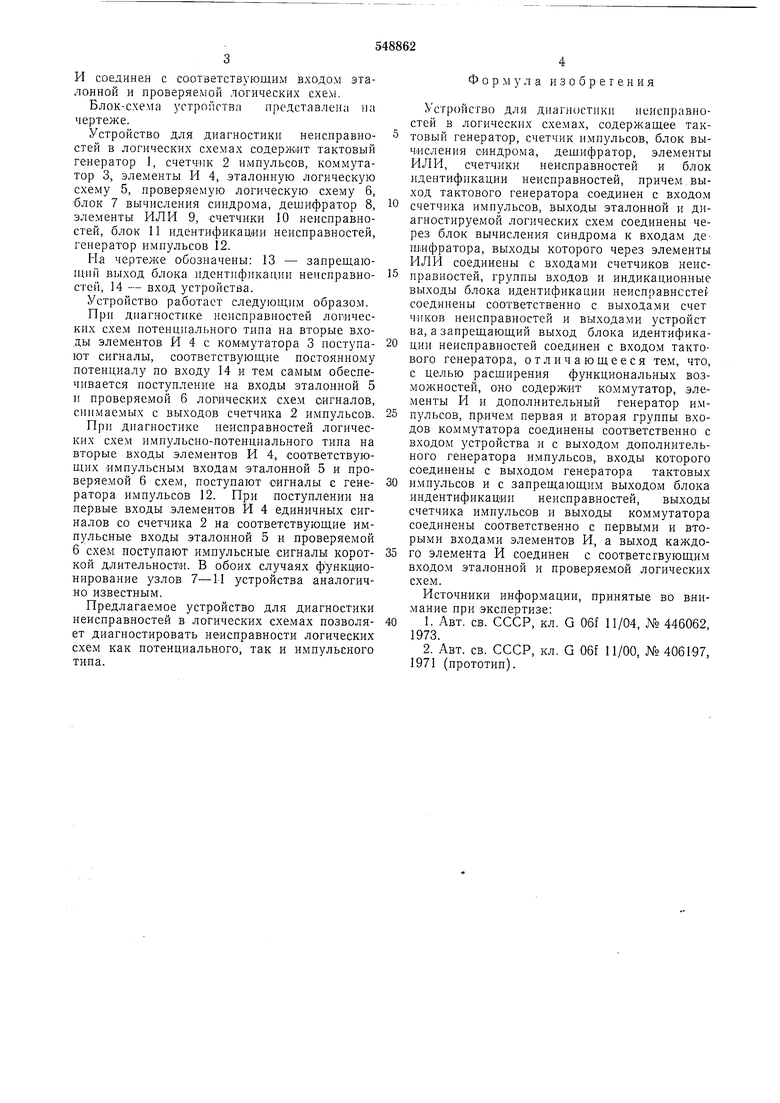

Блок-схема устройств;- представлена на чертеже.

Устройство для диагностики неисправностей в логических схемах содержит тактовый генератор 1, счетчик 2 имп)льсов, коммутатор 3, элементы И 4, эталонную логическую схему 5, проверяемую логическую схему 6, блок 7 вычисления синдрома, дешифратор 8, элементы ИЛИ 9, счетчики 10 неисправностей, блок 11 идентификации неисправностей, генератор импульсов 12.

На чертеже обозначены: 13 - запрещаюН1ИЙ выход блока идентификации неисправностей, 14 - вход устройства.

Устройство работает следующим образом.

При диагностике неисправностей логических схем потенциального типа на вторые входы элементов И 4 с коммутатора 3 поступают сигналы, соответствующие постоянному потенциалу но входу 14 и тем самым обеспечивается поступление на входы эталонной 5 и проверяемой 6 логических схем сигналов, сннмаемых с выходов счетчика 2 импульсов.

При диагностике неисправностей логических схем импульсно-потенциальпого типа на вторые входы элементов И 4, соответствующих импульсным входам эталонной 5 и проверяемой 6 схем, поступают сигналы с генератора импульсов 12. При поступлении на первые входы элементов И 4 единичных сигналов со счетчика 2 на соответствующие импульсные входы эталонной 5 и проверяемой 6 схем поступают импульсные €игналы короткой длительности. В обоих случаях функционирование узлов 7-II устройства аналогично известным.

Предлагаемое устройство для диагностики неисправностей в логических схемах позволяет диагностировать неисправности логических схем как потенциального, так и импульсного типа.

Формула изобретения

Устройство для диагностики неисправностей в логических схе.мах, содержащее тактовый генератор, счетчик импульсов, блок вычисления синдрома, дешифратор, элементы ИЛИ, счетчики неисправностей и блок идентификации неисправностей, причем. выход тактового генератора соединен с входом

счетчика импульсов, выходы эталонной и диагностируемой логических схем соединены через блок вычисления синдрома к входам дешифратора, выходы которого через элементы ИЛИ соединены с входами счетчиков неисправностей, группы входов и индикационные выходы блока идентификации неисправнссте соединены соответственно с выходами счет чиков неисправностей и выходами устройст ва, а запрещающий выход блока идентификации неисправностей соединен с входом тактового генератора, отличающееся тем, что, с целью расширения функциональных возмол ностей, оно содержит коммутатор, элементы И и дополнительный генератор импульсов, причем первая и вторая группы входов коммутатора соединены соответственно с входом устройства и с выходом дополнительного генератора имлульсов, входы которого соединены с выходом генератора тактовых

импульсов и с запрещающим выходом блока ицдентификации неисправностей, выходы счетчика импульсов и выходы коммутатора соединены соответственно с первыми и вторыми входами элементов И, а выход кал дого элемента И соединен с соответсгвующим входом эталонной и проверяемой логических схем.

Источники информации, принятые во внимание при экспертизе:

1. Авт. св. СССР, кл. G 06{ 11/04, № 446062, 1973.

2. Авт. св. СССР, кл. G 06f 11/00, № 406197, 1971 (прототип).

/4

1О

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1141414A1 |

| Устройство для диагностики неисправностей в логических схемах | 1978 |

|

SU744582A2 |

| Устройство для контроля и диагностики логических схем | 1981 |

|

SU972516A1 |

| Устройство для контроля и диагностики цифровых блоков | 1976 |

|

SU605216A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля неисправностей аппаратуры | 1981 |

|

SU966668A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| УСТРОЙСТВО для ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ В ЛОГИЧЕСКИХ СХЕМАХ | 1973 |

|

SU406197A1 |

| Способ контроля логических устройств | 1989 |

|

SU1709256A1 |

Авторы

Даты

1977-02-28—Публикация

1975-01-07—Подача