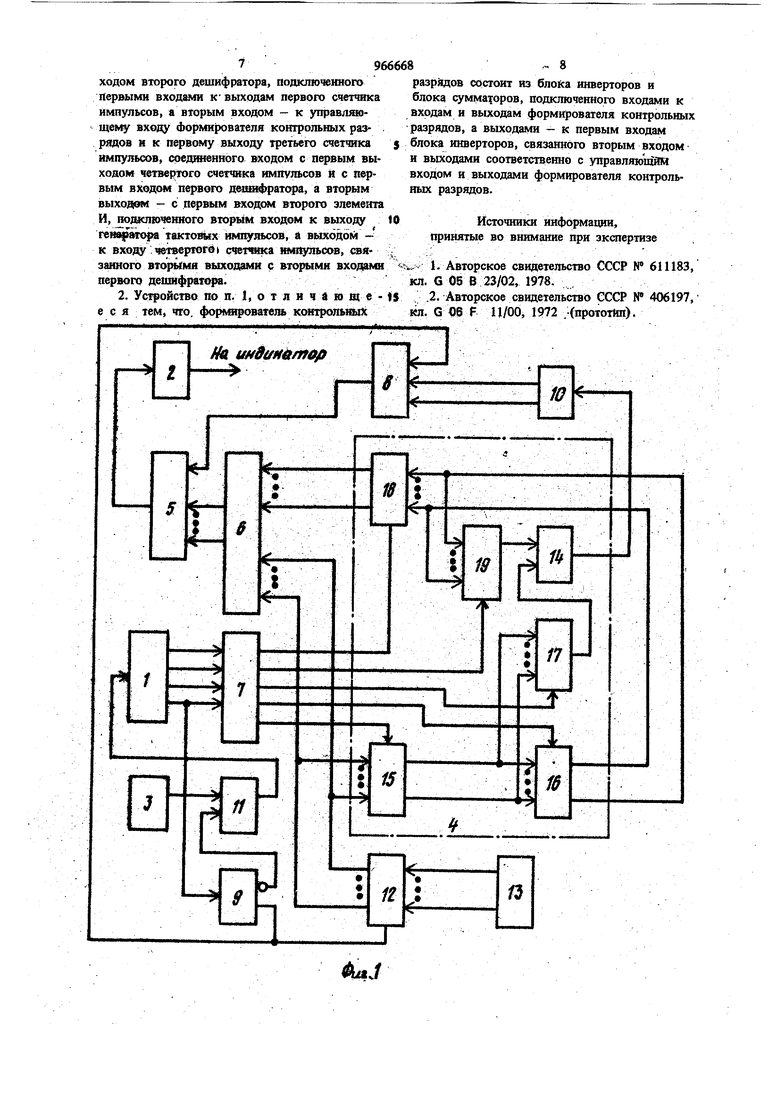

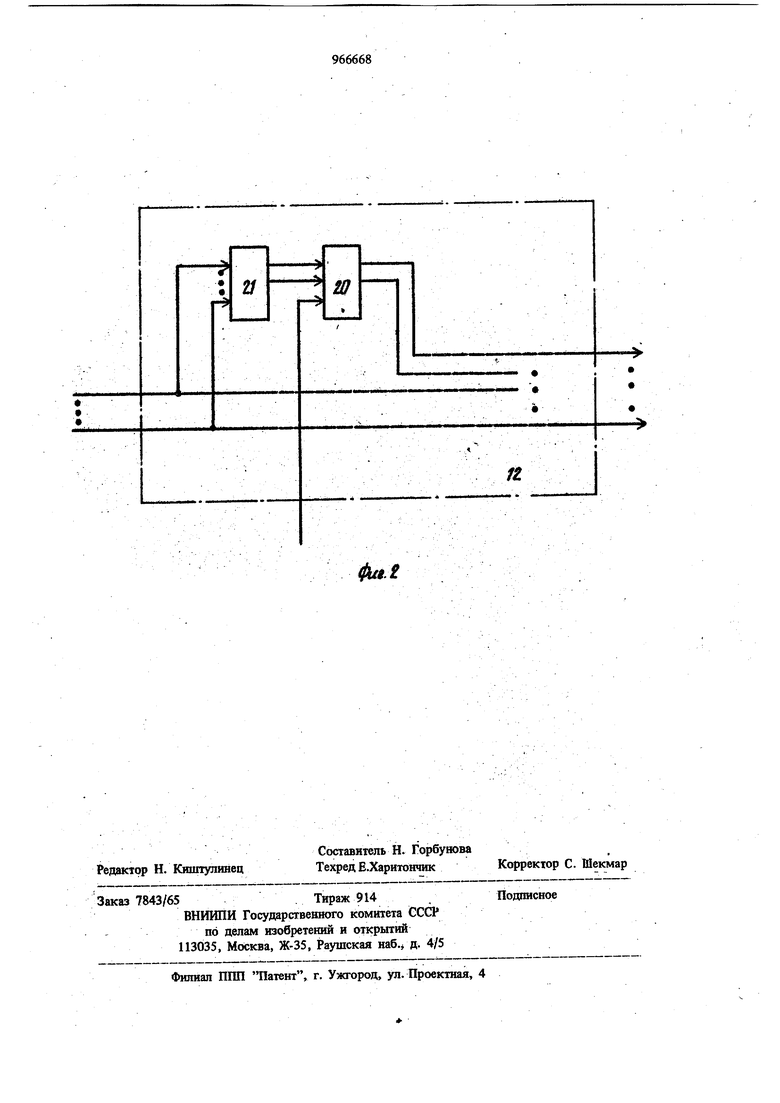

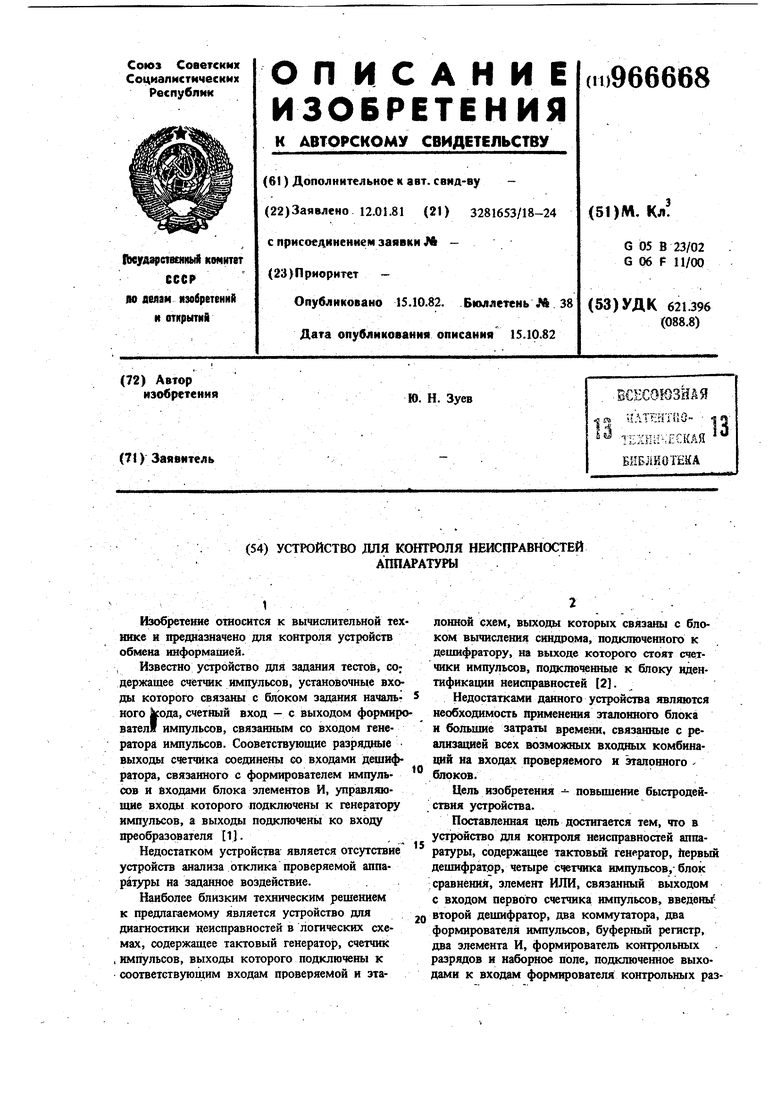

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ НЕИСПРАВНОСТЕЙ , Изобретение относится к вычислительной тех юпсе и предназначено для контроля устройств обмена информацией. . Известно устройство для задания тестов, со; держащее сч(етчик импульсов, установочные входы которого связаны с блоком задания начального |:ода, счетный вход - с выходом формиро вателя импульсов, связаиным со входом генератора импульсов. Сооветствующие разрядные выходы счетчика соединены со входами дешифратора, связанного с формирователем импульсов и входами блока элементов И, управляющие которого подключены к генератору импульсов, а выходы подключены ко входу преобразователя 1J. Недостатком устройства является отсутствие устройств анализа отклика проверяемой аппаратуры на заданное воздействие.. Наиболее близким техническим решением к предлагаемому является устройство для диагностики неисправностей в логических схемах, содержащее тактовый генератор, счетчик , импульсов, выходы которого подключены к соответствующим входам проверяемой и зтаАППАРАТУРЫлонной схем, выходы которых связаны с блоком вычисления синдрома, подключенного к дешифратору, на выходе которого стоят счетчики импульсов, подключенные к блоку идентификации неисправностей 2. Недостатками дшшого устройства являются необходимость применення зтаяонного блока и большие затраты времени, связанные с реализацией всех возможных входных комбинаций на входах {доверяемого и эталонного блоков. Цель изобретеиня - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для контроля неисправностей аппаратуры, содержащее тактовый генератор, первый дешнфратрр, четыре счетчика импульсов,-блок сравнения, злемент ИЛИ, связанный выходом с входом первого счетчика импульсов, введены второй дешифратор, два коммутатора, два формирователя импульсов, буферный регистр, два элемента И, формирователь контрольных . разрядов и наборное поле, подключенное выходами к входам формирователя контрольных раз396рядов, соединенного .выходами с первыми информационными входами блока сравнения и с информационными входами буферного регистра, нодключенного управляющим входом к пе вому выходу первого дешифратора, а выхода ми - к информационным входам первого фор мирователя импульсов и первого коммутатора связанного управляющим входом с вторым выходом первого дешифратора, а выходами . с информационными входами второго коммутатора и второго формирователя шкшульорВо подключенного управ шощим входом к третьему вь1ходу первого дешифратора, а выходом - к первому входу элемента ИЛИ, соединенного вторым входом с выходом первого формирователя импульсов, подключенного управляющим входом к четвертому выходу , первого дешифратора, обязанного пятым выходом с управляющим входом atoporo коммутатора, подключенного выходами к вто рым информационным входам блока сравнения, соёданенного выхр;сшМи с первыми входами первого элемента И, шязанного выходом с входом второго счвтчика имВЕуяьсов, а вторым входом - с выходом второго дешиф ратора, подключенного аервьп«и входами к выходам первого счетчшса ташуявсов, а вторым входом - к у1фавляницему входу форми рователя контролшых разрядов и к первому выходу 1 етьего счетчика импульсов, соединенного входом с первым выходом четвфтого счетчика vaaifyjBicas и с а&рвьш JtxopfiM дешифратора, а Выходом с первым входом второго элемента/И) шд- ч ключенного ВХ1ЩОМ к выхоф гейераtopa тактаВых ймнулБссш, а Вшодом - к входу четвертого счетчика- имоульсов, чжязннного выходами с вторыми ВХОДЕВАЯИ первого депйфратора, Форм{ ватель контрольных разрядснв состоит из блока инверторов и блока сумматароъ, Е1бда(яю ю1шого взиШига к Входам и выходам фс)рм1}рсюателя1со1{трольных р ядов, а выходаш - k входш бпока инверторов, связаншпэвтс ш входом и Выходами соответственно is управпякшдпм юсо- дом и выходами фо|1 шроват«ия контрольных разрядов. На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема формирователя контрольшах разрядов. Устройство содержит четвертый счетчик 1 имцульсов, второй счетчик 2 импульсов, тактовый генератор 3, контролируемое устройство 4, первый элемент И 5, блок б сравнения первый и второй дешифраторы 7 и 8, третий и первый счетчики 9 и 10 импульсов, второй элемент И 11, формирователь 12 контрольШ.1Х разрядов, наборное поле 13, элемент или 14, буферный регистр 15, первый коммутатор 16, первый формирователь .17 импульсов, второй коммутатор 18, второй формирова-. тель 19 импульсов. Формирователь контрольных разрядов содержит блок 20 инверторов, блок 21 сумматоров. Устройство работает следующим образом. Информация, набираемая на наборном поле 13, поступает на ннформащюнные входы формирователя 12 контрольных разрядов, :где в блоке. 21 мматоров (по модулю 2) ШформаДионнре слово делится на байты, щш каждого из которых формщзуется свой конт|роЯы&г Й разряд суммирования по моду лю 2 всех разрящ в& yf KaoTO байта. Полученные taKiiM образом i iOHii)cU{bi& ie разряды поступают на взарды бпока 20 шшерторов, который устроен таким образом, чго контрольные .разряды поступают на его выхода нешшертирова1шыми в случае, есш ш управляющий вход формирователя 12 постунайт V лог1аческай нуль и инвертированными, есм ш ув ашшюншй вход форкшрователя 12 логачеекая единица. В eyymtSK на; выхо ||к рмярша1«ля 12 . KOHTpo i&ix |1аз{ ядов : е шрушя 1информа РННЫЙ код, (СТЬЯШ1Й из ННф6|ЙИаЦИбШ{ОГО СЯО; ва и кон1фош 1шх , причем дфи нали чии лоппескоЙ на у1фавляющем входе формирователя 12 кон льные разряды инвертируются, а при наличии яошческого нуля по- ; ступают на ф мироватёля нейнвертирова1й |)1ми. В исходном x)@uyQeHtd и () выход третьего счетчика 9 находавгя В ёршиком состоянии, сяе ствйё этогб Ш«Ьш& иШульш с выхода тактового reH€f Et(D 3 ароХОдят через Вт6(|рй Mil ш вххщ чэтвертого счетца Iv В качеспзе -чатвертого счетчика испошг зуется коящбвЬй 9еть1резфйзрядный счетчик, с . выхода коюрого пьсл оватеяьность двоичных комбинаций поступает на вход перво1Х ;;,дещифратора 7, на выХбде KOTojporo фбрмируется программа оаровбркй, выдаваемая в Виде логических ш Шравляющие входы перв нчэ и Втор{нх коммутаторов 16 и 18, первого и второго формирователей 17 и19 импульсов (по модулю 2) и буферного регистра15 контролируемого регистра устройства 4. Информащюнные и контролыше разряды с выхода ф ч ш1рователя 12 контрольна разрядов поступают .на вход кшалй выхода контролируемого устройства 4 и на первые информационные (эталонные) входы блока 6 сравнения. Проверка контролируемого устройства 4 осуществляется за два цикла. В течение каждого цикла четвертый счетчик 1 осуществляет сдвиг логической единицы из младшего разряда в старыош. На протяжении первого цикла 596 выход первого разряда третьего счетчика 9 находи ся в нулевом состоянии и информационный код с . неинвертированными контропьньи ш-разрядами с. выхода формирователя 12 проходит через выходной (выход второго коммутатора 18) и входной (выход регистра), каналы контролиру емого устройства 4 и поступает на вторые (контрольные ) информавионные входы блока 6 сравнения, на выходах , в случае совпадзшя контрольных и соответствующих эталонных разрядов, формируются лсотеские единицы. Прн прохождении ииформаоккгаого :кода с неинверт фованнь{ми котропыаып га :разрядами через выходной и входвЫ каналы выхода исправных первого в второго форШрователей 17 и 19 (по ыоуупха 2), щходятся в состоянии логического нуля и позтому первьШ счетчик Ш не изменяет своего состошшя. При этом т первые и второй входа второго дешифратора 8 посгупают логические нул§{. Второй деошфратор оргашгаован так, что форкофует на выходе логическую единицу в случае, ест на два его входа поступают лотичесжие единицы, а }{а третий вход - зюгическйй uyni ийи в случае, есш1 ш все три входа поступают яоги юс1С1 нули. При всех осхаяьйых входшдх ях агорой деага4(ф формирует на выхо- де (юский куль. 1§ случае ишравносш {сон ролйруемогб агагаратуры в конце ва входы вервого эпйи ta М 5 поступают еданица с да | ешиф{ &тс 8 и яоп{че киё еда: HH tebie mttnyjE cbt авй нйя и на ее выхо ф| м фуется первшЙ пот tscKsA иШуяы; С91 1 йеяия. Первый modi завершае1ея 1ем, Ш лшШёский едшшчшй налпуазл е яефв&т выходд, cuOTBeTciiayio ro ctapse )ЯДу. четвертого 1, utoci naet на вход третьего счётч)1ка 9, на первом выходе которйго появляется логичеС1с&я eoiaница. Второй цикл проверки отлй«шётся от первого тем, KOHltpojmpyebioe устройство 4 проходат йнфо|рМшре1бййый код с инвертированными кошрбльными р рядамй. При зтом. первьга и второй форкгаровашга 17 и 19 импульсов формируют по одному импульсу ошибки, которые через элемент ИЯИ 14 поступает на вход первого счеЛиКа Ш. На первые входа первого дешифратора В . ступают логические едшшцы, а на третий вход - логический НУЛЬ. На выходе второго дешифратора 8 формируется лоп чес1сая еди ница и в случае неискаженного прохожде1шя информаднонного кода через контролируемое устройство 4 на выходе первого злеме1па И 5 формируется второй импульс сов 1адеш{я. Второй счетчик 2, в случае прихода двух импульсов совпадения, выдает сигнал исправности контролируемого устройства на индикатор. В конце второго цикла проверки на вход третьего счетчика 9 приходит второй с первого выхода (старшего разряда) первого счетчика 1 и второй (штерспь й) выход второго разряда третьего счетчика 9 переходтг в состояние логического нуля. При зтом прекра1цается поступлшие тактовых нмп Еьсов на вход «твертого счетчика 1 и щюверка завершается. Йредпагаемое ycrpc ctBOt ю сравнению с известным позволяет за счет последовательного включения входного и выходного каналрв коятрол1фуемого устройства, допол штелыюго введения деш11фрат фа, счетчиков, схемы И, ; яаборнОго поля, рмярователя контрольнь х разрядов рпта1Эовать двух1р1кловый программный контроль, значитеюно сокращаю1 а1й время . ; Формула изобретения : I. Устройство Для ксжтроля неисправностей а1Шфа1:пш1,гСоде{1ЖШ 1ее шстовьШ , iepBbrit де)Шфф«1тор, счетчю импупьср, &КЖ « юш узлемект ИДИ. (яязанный ыт | ходом с входом nepBbfQ «летчика импульсов, О т ji и Ч а ю щ е е ip я 1, что, ioBtiiati n &1С11к дабс1 н{я устройства, в него) введйш ВПФ6Й депшфратчф : коммутат, дав фо| м1фовате11Я импулАою, буфе1 1ый pt- Г пкф дэа soeMeHta И, ф91п1С1{ оватёль miinponi fOtx peapnioB .и 1юпе {(одкточеняое . WBOOpfttm к вход фсфмиро8ат еяя койхрольmtsi , еЬ К1/актся ш . тат iiei i fi i i№o№ttit сргл- . ае№яяя 9 liaboftJtiayKa I фсфжяо featetf «««( уара&ляияцим вхоясм к в рэсму шоищу первого деишфрйто {п, а йнихошош --к 1Ь1бо1)|Кша1оннь1М входам первого ф((пё)га Шйпутеов п KOMMytai e, стяза1«с1ГО У1фШптцйм входом с вторым Bibixoiioiit fKfooTO , а вь1хо{ й -т i входакш вторбго kOhOitytaiopa я Btopofo opiaspOftettaa . i и угаудьсов, ш даслюче1вого у1фажп j дом к Т ретьему выходу первого дешмфрамра. i а выходе - к входу ээтемепп ИЛИ; (юеДинёпжнго вюрым 1&Ходом е выходом вф- . вого формирователя ямпульсов, подклю яяогО управляющим входом к четвертому ВЫХОДУ первого дешифратора, связанного; пятым выходом с управляющим входом второго коммутатора. подключенного выходами к вторым нЯформаця Онньпи входам блОка сравнения, соешшошого выходами с первыми входами пбрво :о элемента И, связанного выходом с входом второго .счетчика импульсов, а вторым входом - с выходом второго дешифратора, подключенного Кервыкш входами к выходам первого счетчика импульсов, а вторым входом - к управляющему входу Формирователя контрольных раз- . рядов н к первому выходу третьего счетчика импульсов, средююнного входом с первым выходом четвертого счетчика импульсов и с первым входом первого д хшфратора, а вторым выходти - с первым входом второго элемента И, даслюченного вторым входом к выходу пщрюоря тактовых имт гльсов, а выходом - к входу .четвертогв счегшка шм гльсов, связанного вторь(мя выходами с входами первого дешифратора.

2. Устройство по п. 1, отличдющее с я тем, что. форАШрователь коктролышх

Л iM9i/ttii/if

разрядов состоит из блока инверторов и блока сумматоров, подключенного входами к входам и выходам формирователя контрольных разрядов, а выходами - к первым входам блока инверторов, связанного вторым входом и выходами соответственно с управляющим входом и выходами формирователя контрольных разрядов.

Источники информации, принятые во внимание при зкспертизе

,. 1. Авторское свидетельство СССР N 611183, кл. G 05 В 23/02, 1978. .

.2. Авторское свидетельство СССР № 406197, кл. G 06 F И/00, 1972 .-(прототип).

Ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| Устройство сопряжения с магистралью последовательного интерфейса | 1983 |

|

SU1275417A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Микропрограммное устройство управления | 1980 |

|

SU898431A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Устройство для сопряжения ЭВМ с абонентом по последовательному каналу связи | 1987 |

|

SU1442997A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Устройство для управления трехфазным тиристорным регулятором мощности | 1988 |

|

SU1667035A1 |

6

/У

Ify

и

19

11

;

16

и

:

Авторы

Даты

1982-10-15—Публикация

1981-01-12—Подача