1

Изобретение относится к цифровой вычислительной технике, в частности к средствам автоматизации контроля и поиска неисправностей в устройствах с дискретным характером функционирования.

Известно устройство для контроля и диагностики цифровых блоков 1, содержащее тактовый генератор, двоичный счетчик импульсов, диагностируемую логическую схему, эталонную логическую схему, блок вычисления синдрома, счетчики по числу возможных неисправностей и блок идентификации неисправностей.

К недостаткам известного устройства следует отнести сравнительно низкую разрешающую способность диагностирования, поскольку идентификация неисправностей проводится только на основе анализа топологии схемы и без учета конкретных входных реакций диагностируемой логической схемы и эталонной модели, а также громоздкость и сложность, так как при диагностировании каждого типа логической схемы к устройству необходимо подключить заранее разработанный блок вычисления синдрома.

Известно также наиболее близкое по технической сущности к изобретению устройство для контроля и диагностики 2, содержащее блок сравнения, управляемый генератор, счетчик, дешифратор, регистр неисправностей.

блок индикации и эталонный блок. В нем группа выходов эталонного блока соединена с первой группой входов блока сравнения, вторая группа входов которого служит первой группой входов устройства, а выходы регистра неисправностей - с входами блока индикации. Установочный вход регистра неисправностей является информационным входом устройства. Первый выход генератора подключен

к входу счетчика, выходами соединенного с входом дешифратора. Первый вход генератора является управляющим входом устройства. Недостаток такого устройства в его ограниченных диагностических возможностях.

Цель изобретения - увеличение разрещающей способности диагностирования.

Это достигается тем, что в устройство введен коммутатор, причем группа выходов дешифратора соединена с управляющими входами эталонного блока и с управляющими входами коммутатора, выходы блока сравнения- с информационными входами коммутатора, группа выходов которого подключена к единичным входам регистра неисправностей,

управляющий выход коммутатора соединен с вторым управляющим входом генератора, третий управляющий вход которого связан с управляющим выходом дешифратора, а второй выход генератора - с управляюшнм входом

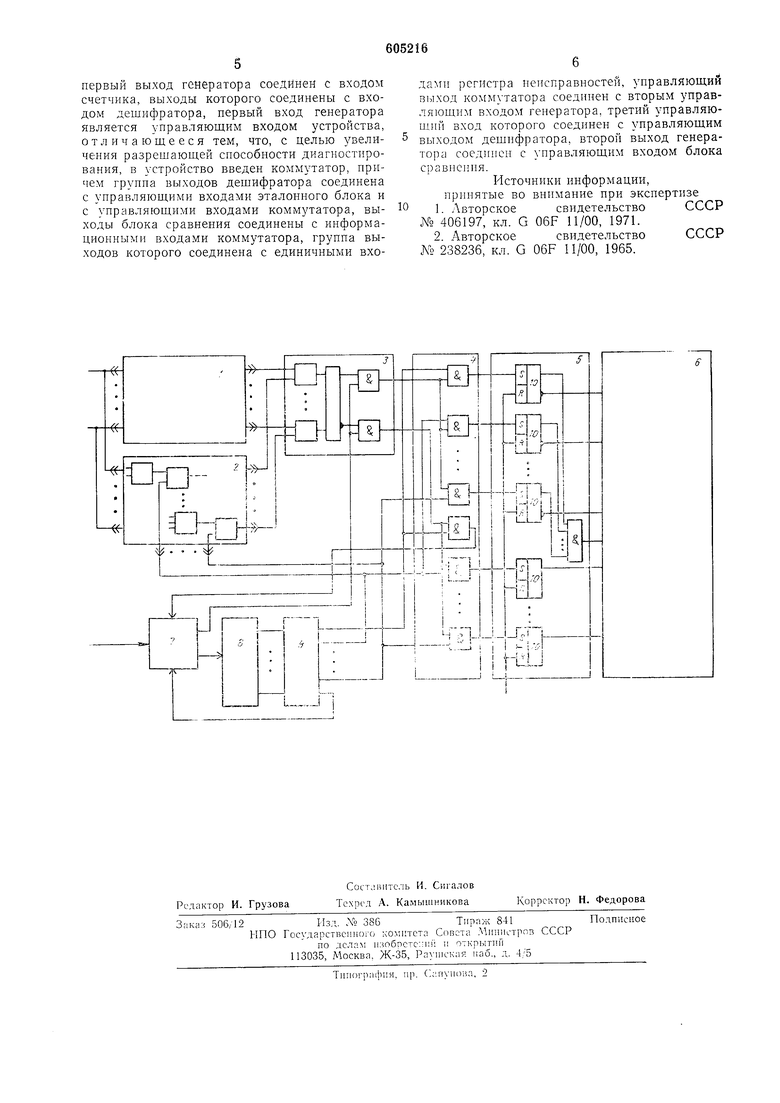

блока сравнения. Структурная схема устройства представлена на чертеже. Первая групна входов устройства соединена с входами нодключенного на время диагностирования контролируемого блока 1 и эталонного блока 2. Эталонный блок 2 представляет собой блок, состоящий из тех же самых элементов, из которых выполнен контролируемый блок, причем каждый выход внутреннего элемента соединен с входом управляемого (на чертеже не показан) инвертора, выход которого в зависимости от управляющего сигнала является либо инверсией выхода, либо нет. Для организации поочередного инвертирования выходных сигналов внутренних компонент эталонного блока используются заправляющие входы эталонного блока. Соответствующие входы контролируемого блока и эталонного блока соединены друг с другом, а выходы подключены к блоку 3 сравнения. Выходы блока сравнения соединены с информационными входами коммутатора 4, функциями которого является распределение сигналов сравнения и несравнения от блока 3 сравнения по номерам внутренних компонентов эталонного блока и соответственно контролируемого блока. Сигналы сравнения после коммутации подаются на вход регистра 5 неисправностей, выходы которого подключены к блоку 6 индикации. Управляемый генератор 7 соединен с входом счетчика 8, выходы которого подключены к дешифратору 9, а выходы дешифратора - к управляющим входам эталонного блока 2 и коммутатора 4. Работает устройство следующим образом. На входы контролируемого и эталонного блока поступают одинаковые входные воздействия, которые принадлежат полному контролируемому тесту. Одновременно с подачей каждого входного набора входные реакции контролируемого блока сравниваются с выходными реакциями. Если реакции контролируемого блока при правильной работе эталонного блока совпадают, поступает следующий входной набор. В случае несовпадения сравнение проводится последовательно: при неправильной работе 1-го компонента, 2-го, 3-го и т. д. Такой режим реализуется следующим образом. При сравнении выходных реакций контролируемого и эталонного блока из коммутатора 4 подается сбрасывающий импульс на вход «Стоп управляемого генератора 7 и моделирование неисправностей на данном входном наборе не проводится. При несравиении (выходные реакции контролируемого и эталонного блока отличаются) сбрасывающий импульс не поступает и на счетчик 8 от управляемого генератора 7 проходит серия импульсов. После дешифратора 9 соответствующий потенциал подается одновременно на эталонный блок 2 (для управления инвертированием) и коммутатор 4 (для распределения результатов сравнения по триггерам 10 регистра 5 неисправностей). Переход к следующему входному набору производится либо при совпадении выходных реакций контролируемого и эталонного блоков при контроле исправного блока либо после окончания диагностирования всех неисправностей. Результаты сравнения выходных реакций подаются на блок 5 для дальнейшего анализа. Сущность алгоритма выделения подозреваемых в неисправности компонентов состоит в следующем. В исходном состоянии (в начале процедуры диагностирования) подозреваются все компоненты. Начальной установкой триггеры регистра неисправностей занимают нулевое состояние, которое означает, что соответствующие компоненты включены в число подозреваемых. Компонент исключается из числа подозреваемых, если хотя бы на одном входном наборе выходные реакции эталонного и контролируемого блоков не совпадают в момент моделирования неисправности соответствующего компонента. Псключение из числа подозреваемых реализуется путем установки соответствующих триггеров в единичное состояние при появлении сигналов несравнения. Таким образом, первоначальная область подозреваемых компонентов, которая охватывает все компоненты контролируемого блока, в процессе диагностирования постепенно сужается до подмножества различных неисправностей. Состояния триггеров одиночных неисправностей на протяжении всей процедуры диагностирования фиксируют попадание - непопадание соответствующих компонентов контролируемого блока в число подозреваемых. Если в результате проведения процедуры ни один компонент не попал в число подозреваемых (т. е. все триггеры установились в состояние единицы), а выходные реакции эталонного и контролируемого блоков не совпадают, то делается вывод о наличии кратной неисправности. Использование предлагаемого устройства позволяет резко сократить время поиска неисправных компонент в цифровых устройствах различных типов (комбинационных и с памятью) за счет полной автоматизации процесса поиска неисправностей. Формула изобретения Устройство для контроля и диагностики ифровых блоков, содержащее блок сравнеия, управляемый генератор, счетчик, дешифатор, регистр неисправностей, блок индикаии и эталонный блок, нричем группа выхоов эталонного блока соединена с нервой руппой входов блока сравнения, вторая група входов которого является нервой группой ходов устройства, выходы регистра неисправостей соединены с входами блока индикации, становочный вход регистра неисправностей вляется информацнонным входом устройства,

первый выход генератора соедййём с входом счетчика, выходы которого соединены с входом дешифратора, первый вход генератора является управляющим входом устройства, отличающееся тем, что, с целью увеличения разрешающей способности диагностирования, в устройство введен коммутатор, причем группа выходов дешифратора соединена с управляющими входами эталонного блока и с управляющими входами коммутатора, выходы блока сравнения соединены с информационными входами коммутатора, группа выходов которого соединена с единичными входами регистра неисправностей, управляющий выход комментатора соединен с вторым управляющим входом генератора, третий управляющий вход которого соединен с управляющим выходом дешифратора, второй выход генератора соединен с управляющим входом блока сравнения.

Источники информации, принятые во внимание при экспертизе

1.АвторскоесвидетельствоСССР № 406197, кл. G 06F 11/00, 1971.

2.АвторскоесвидетельствоСССР № 238236, кл. G 06F 11/00, 1965.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1141414A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

Авторы

Даты

1978-04-30—Публикация

1976-10-13—Подача