1

Изобретение относится к автоматике и ВЬ1числительной технике и может быть использовано для повышения надежности резервированных вычислительных машин, автоматической обработки и управления.

Известно устройство для связи между вычислительными блоками системы, в состав которого входят схемы управления и сдвигающие регистры 1.

В известном устройстве производится перестройка на уровне вычислительных блоков с целью управления потоками информации, а не с делью повышения ее надежности. При отказах вычислительных блоков система теряет работоспособность.

Наиболее близким к изобретению до технической суш,ности и достигаемому результату является многоканальное устройство для связи вычислительных узлов в системе, содержаш,ее группу матриц связи, группу регистров фиксации, входы и выход каждой матрицы связи соединены соответственно с выходами предыдуш,их и входом последующего вычислительных узлов, выход каждого последнего из вычислительных узлов, соответствующих одному каналу, соединен с соответствующим входом блока переключения каналов 2.

Недостатком известного устройства является ненадежность при разрывах в связях меж2

ду блоками системы и то, что при поиске работоспособной структуры узлы исправных каналов не исключаются из дальнейшей процедуры поиска, что увеличивает время поиска.

Целью изобретения является повыщение надежности и быстродействия устройства.

Поставленная цель достигается тем, что каждый канал содерл ит группу сдвигающих

регистров, группу элементов ИЛИ, элементы И и НЕ, причем выход последнего из вычислительных узлов, соответствующих одному каналу, соединен через элемент НЕ с первым входом элемента И этого канала и с входами

группы элементов ИЛИ других каналов, выходы элементов ИЛИ группы соединены с входами соответствующих регистров фиксации группы, выходы которых соединены с входами сдвигающих регистров группы, соединенных последовательно, выход каждого сдвигающего регистра группы одного канала соединен с заправляющим входом соответствующей матрицы связи своего канала и с входами соответствующих элементов ИЛИ

групп других каналов, вторые входы элементов И всех каналов соединены с входом устройства.

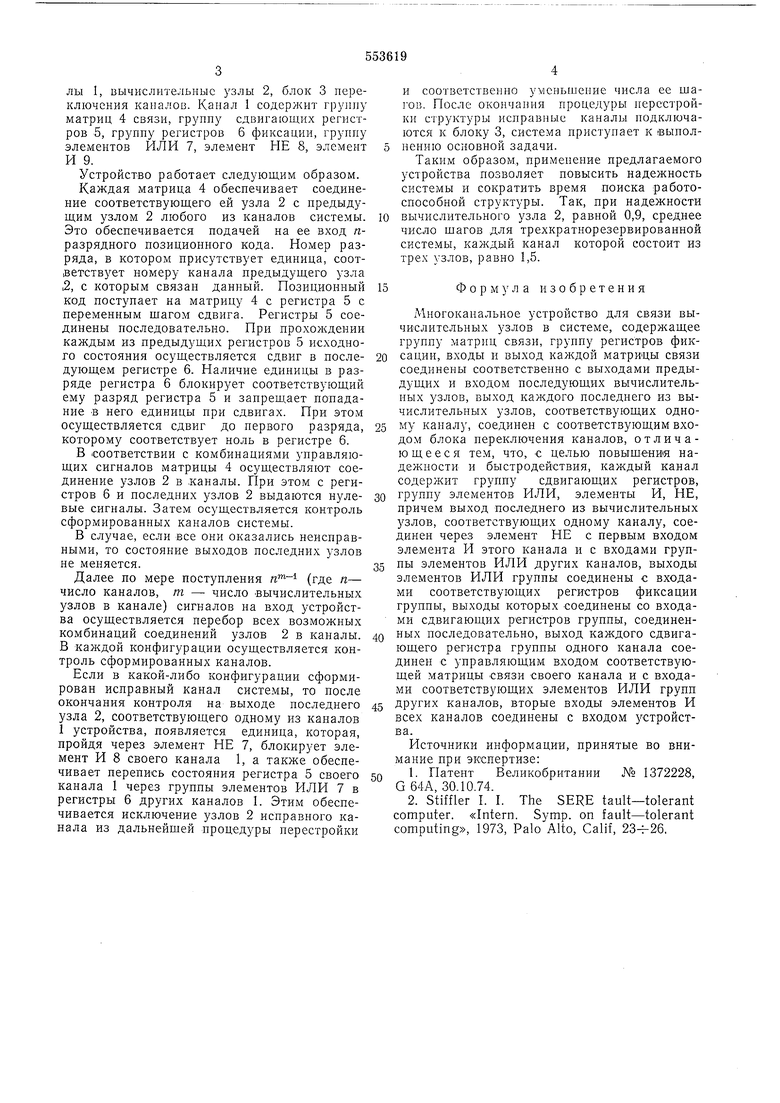

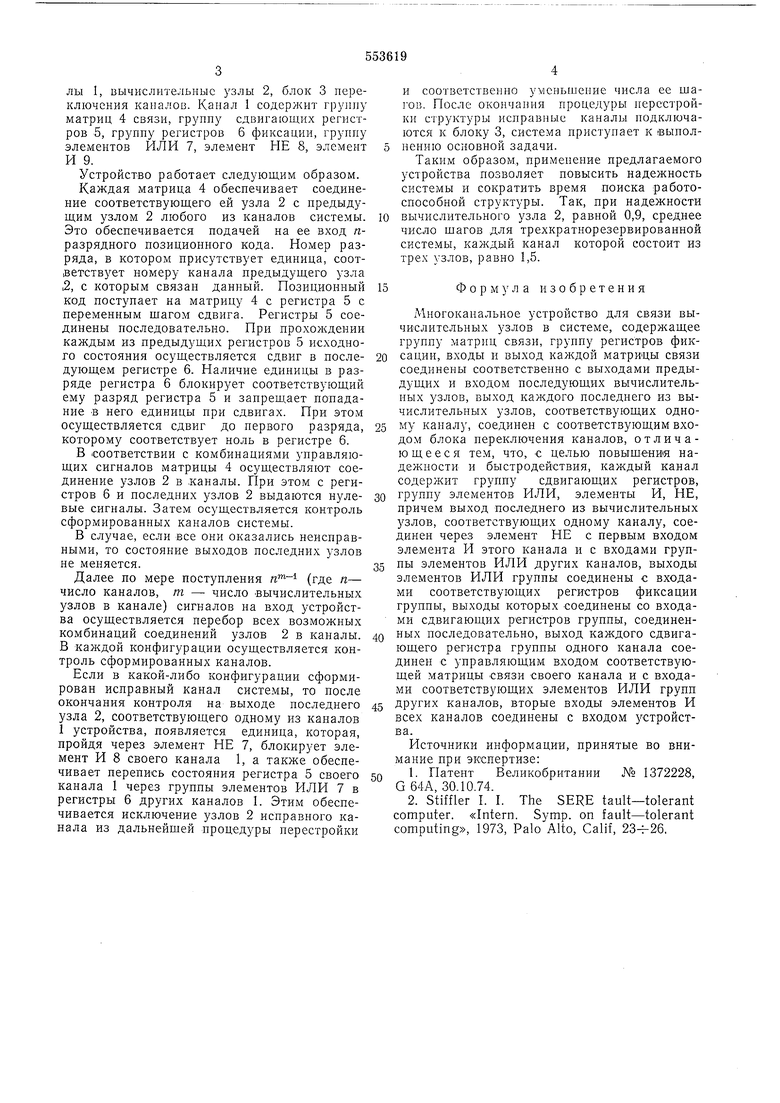

На чертеже представлена блок-схема многоканального устройства для связи вычислительных узлов в системе, содержащего каналы 1, вычислительные узлы 2, блок 3 переключения каналов. Канал 1 содержит группу матриц 4 связи, группу сдвигающих регистров 5, группу регистров 6 фиксации, группу элементов ИЛИ 7, элемент НЕ 8, элемент И 9.

Устройство работает следующим образом. Каждая матрица 4 обеспечивает соединение соответствующего ей узла 2 с предыдущим узлом 2 любого из каналов системы. Это обеспечивается подачей на ее вход празрядного позиционного кода. Номер разряда, в котором присутствует единица, соответствует номеру канала предыдущего узла ,2, с которым связан данный. Позиционный код поступает на матрицу 4 с регистра 5 с цеременным щагом сдвига. Регистры 5 соединены последовательно. При прохождении каждым из предыдущих регистров 5 исходного состояния осуществляется сдвиг в последующем регистре 6. Наличие единицы в разряде регистра 6 блокирует соответствующий ему разряд регистра 5 и запрещает попадание в него единицы при сдвигах. При этом осуществляется сдвиг до первого разряда, которому соответствует ноль в регистре 6.

В соответствии с комбинациями управляющих сигналов матрицы 4 осуществляют соединение узлов 2 в каналы. При этом с регистров 6 и последних узлов 2 выдаются нулевые сигналы. Затем осуществляется контроль сформированных каналов системы.

В случае, если все они оказались неисправными, то состояние выходов последних узлов не меняется.

Далее ло мере поступления п™- (где п- число каналов, т - число вычислительных узлов в канале) сигналов на вход устройства осуществляется перебор всех возможных комбинаций соединений узлов 2 в каналы. В конфигурации осуществляется контроль сформированных каналов.

Если в какой-либо конфигурации сформирован исправный канал системы, то после окончания контроля на выходе последнего узла 2, соответствующего одному из каналов 1 устройства, появляется единица, которая, пройдя через элемент НЕ 7, блокирует элемент И 8 своего канала 1, а также обеспечивает церепись состояния регистра 5 своего канала 1 через группы элементов ИЛИ 7 в регистры 6 других каналов 1. Этим обеспечивается исключение узлов 2 исправного канала из дальнейщей процедуры перестройки

и соответственно уменьшение числа ее щагов. После окончания процедуры перестройки структуры исправные каналы подключаются к блоку 3, система приступает к сыполнению основной задачи.

Таким образом, применение предлагаемого устройства позволяет повысить надежность системы и сократить время поиска работоспособной структуры. Так, при надежности

вычислительного узла 2, равной 0,9, среднее число шагов для трехкратнорезервированной системы, каждый канал которой состоит из трех узлов, равно 1,5.

Формула изобретения

Многоканальное устройство для связи вычислительных узлов в системе, содержащее группу матриц связи, груипу регистров фиксации, входы и выход каждой матрицы связи соединены соответственно с выходами предыдущих и входом последующих вычислительных узлов, выход каждого последнего из вычислительных узлов, соответствующих одному каналу, соединен с соответствующим входом блока иереключения каналов, отличающееся тем, что, € целью повыщениЯ надежности и быстродействия, каждый канал содержит группу сдвигающих регистров,

группу элементов ИЛИ, элементы И, НЕ, причем выход последнего из вычислительных узлов, соответствующих одному каналу, соединен через элемент НЕ с первым входом элемента И этого канала и с входами группы элементов ИЛИ других каналов, выходы элементов ИЛИ группы соединены с входами соответствующих регистров фиксации группы, выходы которых соединены со входами сдвигающих регистров группы, соединенных последовательно, выход каждого сдвигающего регистра группы одного канала соединен с управляющим входом соответствующей матрицы связи своего канала и с входами соответствующих элементов ИЛИ групп

других каналов, вторые входы элементов И всех каналов соединены с входом зстройства.

Источники информации, принятые во внимание при экспертизе:

1. Патент Великобритании № 1372228, G 64А, 30.10.74.

2. Stiffler I. I. The SERE tault-tolerant computer. «Intern. Symp. on fault-tolerant computing, 1973, Palo Alto, Calif, .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для переключения резервных блоков системы | 1976 |

|

SU605217A1 |

| Устройство для выбора работоспособной структуры вычислительного комплекса | 1980 |

|

SU1037256A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Дублированная вычислительная система | 1990 |

|

SU1783528A1 |

| Устройство для сдвига информации | 1989 |

|

SU1607017A2 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для контроля специализированных вычислительных машин | 1974 |

|

SU636622A1 |

| Трехкаскадная коммутирующая система | 1984 |

|

SU1226481A1 |

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| Трехкаскадная коммутирующая система | 1989 |

|

SU1622886A1 |

Авторы

Даты

1977-04-05—Публикация

1975-07-25—Подача