Изобретение относится к области автоматики и вычислительной техники и может быть использовано в многопроцессорных вычислительныхсистемах

Цель изобретения - повьпиение быстродействия трехкаскадной коммутирующей системы за счет одновременного поиска всех каналов связи.

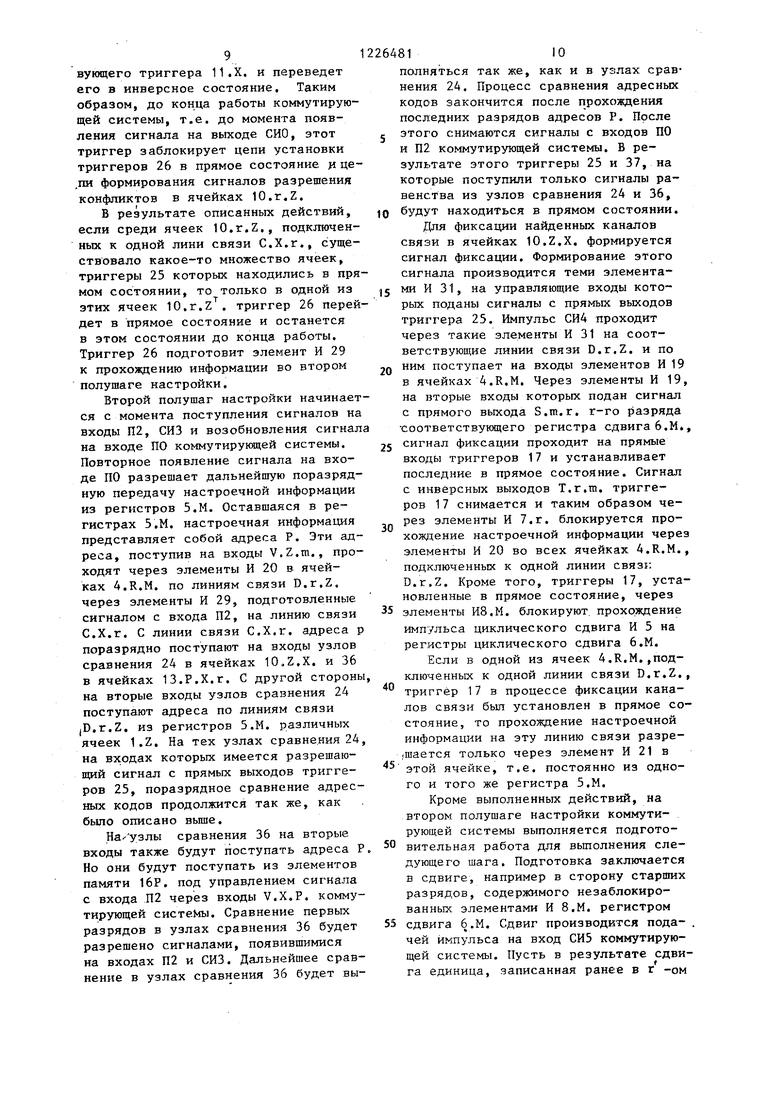

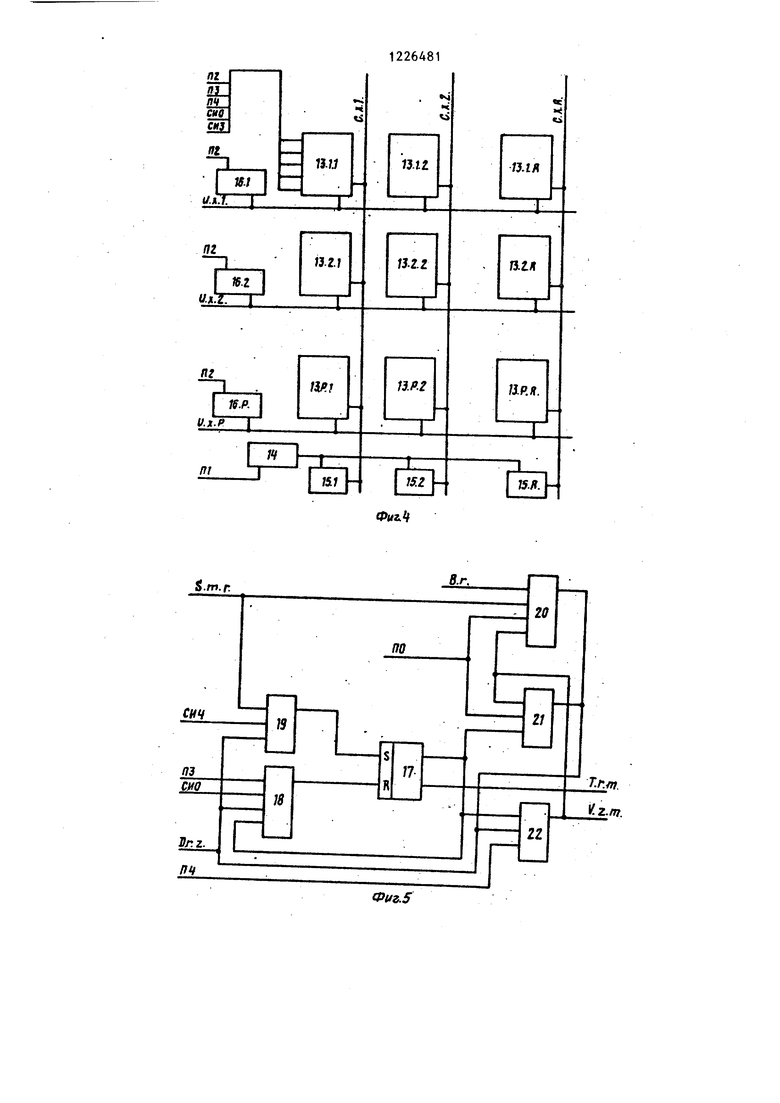

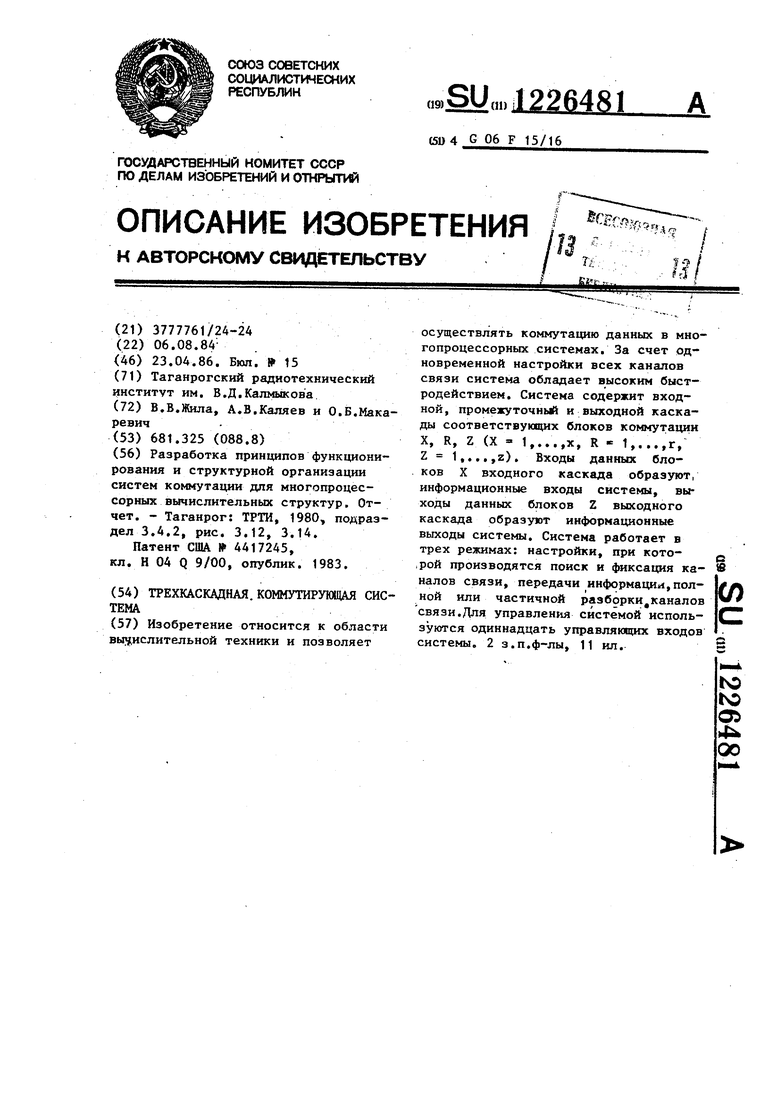

На фиг,1 представлена структурная схема трехкаскадной неблокирующей коммутирующей системы; на фиг.2-4 - функциональные схемы блоков коммутации соответственно выходного, промежуточного и входного каскадов; на фиг.5-7 - функциональные схемы ячеек коммутации соответственно выходного, промежуточного и входного каскадов; на фиг.8 - функциональная схема узла сравнения; на фиг.9 - функциональная схема узла ускоренного распространения сигнала занятости входной коор- щнатной шины; на фиг.10 - функциональная схема узла разборки канала связи; на фиг.11 - временная диаграмма управляющих сигналов, необходимых для выполнения одного шага настройки коммутирующей системы.

Предлагаемая коммутирующая система (фиг.1) содержит Z блоков коммутации 1.1, 1.2,...,1.2, образующих вы- ходной каскад, R блоков коммутации 2.1,2.2,...,2.R, образующих промежуточный каскад, х блоков коммутации 3.1, 3.2,...,3.x, образующих входной каскад, р.х информационных входов системы (И.X.р),являющихся одновременно входами данных блоков коммутации 1.x входного каскада, m.z информационных выходов системы (V.z.tn.), являющихся одновременно выходами данных блоков коммутации выходного каскада, линии связи (С.х.г.) между блоками 1.x и 1.R входного и промежуточного каскадов, соединяющие выходы данных блоков 1.X входного каскада с входами данных блоков 1.R промежуточного каскада, и линий связи (D. r,z.) между блоками 1.R и 1,Z промежуточного и выходного каскадов, соединяющие соответствующие выходы данных блоков 1.R с входами данных блоков I.Z. При этом ...,z, Р 1,...,р; R 1,...,;; ,...,х; М 1 ,.. I ,П1.

Коммутирующая система содержит также следующие управляющие входы: СИО - вход начальной установки исходного состояния системы; ПО - вход

настройки; П1 - первый вход синхронизации, соответствующий первому полушагу настройки; П2 - второй вход синхронизации, соответствующий второму полушагу настройки; СИ1 - первый вход запуска для запуска узлов сравнения; СИ2 - вход разблокировки для разрешения конфликта при занятии линий связи C.X.R; СИЗ - второй вход

запуска для запуска узлов сравнения во втором полушаге настройки; СИ4 - вход фиксации каналов связи; СИЗ - вход поиска незаблокированных каналов связи; ПЗ - вход разборки каналов связи; П4 - вход разрешения передачи информации.

Каждый блок 1.Z (фиг.2) выходного каскада состоит из матрицы ячеек 4.R.M. коммутации и узла управления,

содержащего группу элементов памяти 5.М. индентификаторов входов, группу регистров циклического сдвига 6,М., первую группу элементов И7.г., вторую

группу элементов И8.М. У блока I.Z. через S.m.r. обозначены прямые выходы г-ьгх разрядов регистров циклического сдвига 6.М.

Каждый блок 2.г. промежуточного каскада (фиг.З) состоит из узлов ус

коренного распространения сигнала занятости 9.Х., матрицы ячеек 10.Z.X. коммутации, группы триггеров 11.X. и группы элементов И12.Х.

Каждый блок З.Х. (фиг.4) входного

каска,ца состоит из матрицы ячеек

13.Р.R., коммутации элемента 14 идентификатора блока коммутации, группы ключей 15.R. и элементов памяти 16.Р. идентификаторов входов.

В свою очередь каждая ячейка

4.R.M. (фиг.З) состоит из триггера 17 коммутации, узла разборки каналов связи 18, элементов И 19-22. Через Т.г.т. обозначен инверсньм выход триггера 17, являющийся выходом занятости ячейки.

Ка;«дая ячейка 10.Z.X. (фиг.6) сос- тоит из элемента ИЛИ 23, узла сравнения 24, триггеров 23 коммутации и

26 управления, элемента запрета 27, узла 28 разборки каналов связи,элементов И 29-32. Кроме того, в каждом коммутирующем узле 10.Z.X. имеется вход F.Z.X. признака занятости

входной координатной шины и выход Е. Z.X. занятости ячейки, необходимых для разрешения конфликта при распределении линий связи С,Х,г.

3

Каждая ячейка 13.Р.R. (фиг.7) состоит из элемента И 33, узла 34 разборки канала связи, элемента ИЛИ 35 узла сравнения 36 и триггера 37 коммутации.

Узлы сравнения 24 и 36 выполнены по идентичной схеме (фиг.8) и состоя из сумматора 38 по модулю два, элементов И 39 и 40 и элемента ИЛИ 41. Обозначения, указанные на входах и выходах узла сравнения без скобок, относятся к узлу сравнения 24, а обозначения в скобах - к узлу сравнения 36.

Узлы ускоренного распространения сигнала занятости входной координатной шины (фиг.9) состоят из элементов ИЛИ 42 X.Z., а узлы разборки каналов связи (фиг.10) - из элемента И 43, элемента задержки 44 на один такт, например D-триггера, и элемента ИЛИ 45. Входы узла разборки каналов связи обозначены через 46-49, а входы - 50.

Предлагаемая трехкаскадная комму- 1тирующая система может работать в трех режимах: в режиме настройки, пр котором производится поиск фиксации каналов связи, в режиме передачи информации и в режиме полной или час- тичной разборки каналов связи, ставших ненужными.

Поиск и фиксация каналов связи в режиме настройки осуществляется в коммутирующей системе под воздейст- вием программы коммутации и управля- КШЦ1Х сигналов, появляющихся на соответствующих управляющих входах системы в соответствии с временной диаграммой, изображенной на фиг.11. Про- грамма коммутации представляет собой упорядоченное в соответствии с расположением выходов V.z.m. коммутирующей системы множество пар (р.х.), идентифицирующих те входы И.х.р. ком мутирующей системы, с которыми необходимо соединить соответствующий выход V.z.m. В дальнейшем предполага

ется, что X является адресом блока З.Х., в котором расположен нужный вход, ар- адрес нужного входа в пределах этого блока. Кроме того, предполагается, что перед началом работы тем или иным способом программа коммутации записана в регистры 5.m. таким образом, что в каждом регистре хранится ровно одна пара (р.х.). Эта пара указывает с каким входом

г

И.х.р. коммутирующая система должна соединить выход V.z.m., к которому подключен данный регистр 6.М. Предполагается также, в элементах памя- ти 14 и 16.р. какого блока 3.x. хранятся соответственно адреса х этих блоков и адреса р входов И.х.р. коммутирующей системы. Эта информация может быть зафиксирована жестко,если элементы памяти выполнены в виде постоянных запоминающих устройств, либо может записываться в них по мере необходимости, если эти элементы памяти выполнены в виде регистров.

Работа коммутирующей системы в режиме настройки начинается с установки всех триггеров и регистров циклического сдвига 6.М. в исходное состояние. Это осуществляется импульсом, поданным на вход СИО коммутирующей системы. Этот импульс устанавливает в инверсное состояние триггеры 11 .X.,триггеры 17 через узлы разборки каналов связи 18 в каждой ячейке 4.R.M.,тригеры 25 через узлы разборки каналов связи 28 и элемент ИЛИ 23, триггеры 26 через узлы разборки каналов связи 28 в каждой ячейке lO.ZiX. и триггеры 37 через узлы разборки каналов связи 34 и элементы ИЛИ 35 в каждой ячейке 13.Р.г. Кроме того, этот импульс,поступая на входы регистров циклического сдвига 6.М., записывает в них соответствующий код, содержащий только одну единицу в том разряде, к .входу которого подключен вход СйО. Таким образом, после записи этих кодов в регистрах 6.М., расположенных в пределах одного блока I.Z., не будет существовать одинаковых кодов. В дальнейшем предполагается, что в регистрах сдвига 6.1. единица записана в первом разряде в регистрах сдвига 6,2 - во втором и т.д. Наконец, в регистрах сдвига 6.М. единица записана в разряде М. После записи кодов потенциал с прямого выхода S.m.r. разряда, содержащего единицу, каждого регистра 6.М. поступает на соответствующие элементы И 19 и 20 и готовят их к приему информации.

Дальнейшая работа коммутирующей системы в режиме настройки непосредственно связана с поиском и фиксацией каналов связи в соответствии с программой коммутации. Особенностью работы предлагаемой коммутирующей сиетемы в этом режиме является то, что в системе ведется поиск одновременно всех необходимых каналов связи. Однако, несмотря на это, для завершения полного процесса поиска и фиксации всех требуемых каналов связи необходимо выполнить R шагов настройки. Это связано с тем, что для каждой пары (р.Х) существует R различных каналов связи через промежуточный каскад коммутирующей системы. Для неблокирующей трехкаскадной коммутирующей системы по крайней мере один из них будет незаблокированным независимо от того, в каком порядке производится поиск этих каналов,

Каждый шаг настройки выполняется за два полушага. В течение первого полушага производится поиск каналов

связи через блоки 2.R. промежуточного 20 gee линии связи С.Х.г., связанные с

каскада к блокам З.Х. входного каскада. На втором полушаге производится поиск каналов связи для конкретных входов И.х.р. в коммутирующих блоках З.Х., образование ветвящихся в коммутирующих блоках 2.R. каналов связи с выходами V.Z.m., если в подключенных JC ним регистрах 5.М. хранится одинаковая адресная информация, и фиксаций найденных каналов во всех коммутирующих блоках коммутирующей системы.

Первый полушаг первого шага настройки начинается подачей на входы ПО,

25

30

этим блоком. По линиям связи С.Х.Г. соответствуювще адреса X поступают на вторые входы узлов сравнения 24. Сигналы, существующие на входах ПО и СИ1, разрешают сравнение первых разрядов адресных кодов. Сравнение производится следующим образом. Сумматор 38 по модулю два суммирует содержимое поступивших разрядов. Если поступившие разряды одинаковы, то сигнал появится на инверсном выходе элемента 38, если разные - то на прямом. Сигнал СИ1, пройдя через элемент ИЛИ 41, и сигнал ПО, поступив на управляющие входы элементов И 39 и 40, разрешают передачу резуль татов сравнения на соответствующие входы триггера 25. В зависимости от результатов сравнения триггер установится в прямое или останется в инверсном состоянии. Те узлы сравнения 24, на входы которых поступили одинаковые эначения первых разрядов адресов X, устанавливают соединенные с ними триггеры 25 в прямое состояние и сигналы, появившиеся на прямых входах этих триггеров, разрешают дал нейшее сравнение адресных кодов на этих узлах сравнения. Каждый следующий сигнал равенства подтверждает прямое состояние триггера 25. Сигнал неравенства, выработанный узлом срав нения 24 на любом шаге сравнения, пройдя через элемент ИЛИ 23, установит триггер 25 в инверсное состояние тем самым прекращает дальнейшее срав нение адресов X в данном узле сравне ния 24. После выдачи на сравнение

П1 и СИ1 управляющих сигналов, изображенных на временной диаграмме (фиг.11). Сигнал, поступая на выходные вентили регистров 6.т. разрешает вьщачу хранящейся в них программной информации на соответствуюш 1й выход V.Z.ra. коммутирующей системы. Этот же сигнал поступает на входы всех элементов И 20 во всех ячейках A.R.M. В результате те элементы И 20, на вторые входы которых поступил сигнал с прямых выходов S.m.r. трех разрядов циклического сдвига 6.М., которые хранят единицы, будут подготов- лены к приему настроечной информации, так как на третьи управляюш 1е входы этих элементов поступает разрешающий сигнал с выхода B.t. элементов И 7.г. Среди всех элементов И 20, подключенных входом к одному и тому же выходу V.Z.ra., будет только один подготовлен к приему информации. Аналогично среди всех элементов И 20, подключенных к одной линии связи D.r.Z.,

будет только один подготовлен к передаче информации. Настроечная информация из каждого регистра 5.М. поразрядно начнет поступать по подключенному к этому регистру выходу V,Z.т, через подготовленный для нее элемент И 20 по соответствующей линии связи D.r.Z.Ha входы узлов сравнения 24, расположенных в ячейках 10.Z,X.,подключенных к одной линии связи. Естественно, что прежде всего будут поступать адреса X блоков З.Х.

С другой стороны сигнал с входа П1, поступая на входы элементов памяти 14 в блоках З.Х., разрешает поразрядную передачу адресов X всех блоков З.Х. Адрес X элемента памяти 14 в каждом блоке З.Х. через ключ 15„К. поступает одновременно на

этим блоком. По линиям связи С.Х.Г. соответствуювще адреса X поступают на вторые входы узлов сравнения 24. Сигналы, существующие на входах ПО и СИ1, разрешают сравнение первых разрядов адресных кодов. Сравнение производится следующим образом. Сумматор 38 по модулю два суммирует содержимое поступивших разрядов. Если поступившие разряды одинаковы, то сигнал появится на инверсном выходе элемента 38, если разные - то на прямом. Сигнал СИ1, пройдя через элемент ИЛИ 41, и сигнал ПО, поступив на управляющие входы элементов И 39 и 40, разрешают передачу результатов сравнения на соответствующие входы триггера 25. В зависимости от результатов сравнения триггер установится в прямое или останется в инверсном состоянии. Те узлы сравнения 24, на входы которых поступили одинаковые эначения первых разрядов адресов X, устанавливают соединенные с ними триггеры 25 в прямое состояние и сигналы, появившиеся на прямых входах этих триггеров, разрешают дальнейшее сравнение адресных кодов на этих узлах сравнения. Каждый следующий сигнал равенства подтверждает прямое состояние триггера 25. Сигнал неравенства, выработанный узлом сравнения 24 на любом шаге сравнения, пройдя через элемент ИЛИ 23, установит триггер 25 в инверсное состояние, тем самым прекращает дальнейшее сравнение адресов X в данном узле сравнения 24. После выдачи на сравнение

всех разрядов адресов X в соответствии с временной диаграммой снимается сигнал с входа III и временно снимается с входа ПО. В результате в прямом состоянии останутся трлько те триггеры 25, на которые все время поступали только сигналы равенства с узлов сравнения 24,

Так как адреса X, поступившие на один блок 2,R., однозначно определяют линии связи С.Х.Г., соединяющие этот блок с блоками З.Х. входного каскада, можно бьшо бы считать, что канал связи через промежуточный блок определен. Однако из-за того, что к одному коммутирующему блоку 3,Х,, подключено р входов, возникает большая вероятность поступления из различных блоков 1,Z, .на ячейки 10,Z,X, подключенных к одной линии связи С,Х,г. пар (Р,Х) с равными X, но неравными Р, На первом полушаге настройки эти пары различить нельзя,т,е, все триггеры 25 ячеек 10.Z,X,, получивших равные X, не зависимо от дальнейших Р будут установлены в прямое состояние. Таким образом, возникает конфликт за занятие линии связи С,X.г Для разрешения этого конфликта и для создания возможности поиска канала связи в коммутирующих блоках З.Х, во втором полушаге настройки необходимо принять решение, какую же из выделенных на первом полушаге настройки установкой триггеров.25 в прямое состояние линий связи D.r,Z, подключить к линии связи С.Х.г, в предлагаемой

коммутирующей системе принято, что к незанятой линии связи С.Х.г. из всех претендукщих на подключение к ней на данном шаге линий связи С.Х.г. выбирается та, у которой значение параметра Z будет наименьшем. Этот выбор осуществляется во время подачи импульса на вход СИ2. Этот импульс поступает на вход элементов И 12.Х., подготовленных сигналами с прямых выходов соответствующих триггеров 11.Х На выходе G.X. каждого элемента И 12.Х. формируется импульс, который поступает на элементы И 27 и 32 всех ячеек 10.Z,X,, подключенных к соответствующей линии связи С.Х.г. Тогда предположим, что триггеры 25 коммутирующих

узлов lO.I.X,, 10,2,X,10,Z-1.X,

подключенных соответственно к линиям связи D,r,1., D,r,2,,.,,,D,r.z -1,, установлены в инверсное состояние.

триггер 25 ячейки 10,Z ,Х. установлен в прямое состояние, а триггеры 25:: всех остальных ячеек lO.Z.X, (при ), подключенных к той же линии

связи C,X,R., установлены либо в прямое, либо в инверсное состояние. Тогда элементы запрета 27 в ячейках 10,Z,X, ( ) будут блокированы сигналами с прямых выходов триггеров 25,

Элемент запрета 27 в ячейке 10.z ,Х, будет подготовлен к прохождению информации, так как на его управляющий вход поступает разрешакнций сигнал с прямого выхода триггера 25, На блокирующий вход этого элемента запрета 27 сигнал не поступает, так как в ячейках 10,Z,X, () сигнал F,Z,X. занятости входной шины вырабатываться не будет, т.е. их триггеры 25 находятся в инверсных состояниях в силу принятых выше предположений. Следовательно, на выходе F,z -1 узла 9,Х, ускоренного распространения сигнала занятости входной координатной шины

сигнал будет отсутствовать. Таким образом, импульс, поступающий с выхода соответствующего элемента И 12,X,, пройдя через элемент запрета 27 в ячейке lO.Z .X,, перебросит в прямое

состояние триггер 26. Кроме того, в этой же ячейке на элементе И 32 сформируется признак занятости входной шины. Этот признак поступит с выхода E.Z . ячейки 10.Z.X, на соотвгтствующий вход узла 9.Х. ив одного такта распространится на все входы F.Z. ячеек lO.Z.X, при и заблокирует элементы запрета 27, расположенные в этих ячейках, и таким

.образом запретит переход в прямое

состояние триггеров 26 во всех ячейках 10,Z,X, ( ) независимо от состояния их триггеров 25, Время прохождения признака .занятости на все

входы соответствующих ячеек через узлы 9,Х. ускоренного распространения сигнала занятости входной шины регулируется подбором максимального зна- чения Т параметра t, исходя из того,

что все переходные процессы в системе при распространении сигнала занятости входной шины должны закончиться намного раньше окончания импульса СИ2. Сигнал занятости, возникающий в

элементе 32 любой ячейки lO.r.Z,, .пройдя через уэел 9.Х, ускоренного распространения сигнала занятости, поступит на инверсный вход соответст9

вующего триггера 11,Х, и переведет его в инверсное состояние. Таким образом, до конца работы коммутирующей системы, т.е. до момента появления сигнала на выходе СИО, этот триггер заблокирует цепи установки триггеров 26 в прямое состояние, к це .пи формирования сигналов разрешения конфликтов в ячейках lO.r.Z.

В результате описанных действий, если среди ячеек lO.r.Z., подключенных к одной лини связи С.Х.Г., существовало какое-то множество ячеек, триггеры 25 которых находились в прямом состоянии, то только в одной из этих ячеек lO.r.Z . триггер 26 перейдет в прямое состояние и останется в этом состоянии до конца работы. Триггер 26 подготовит элемент И 29 к прохождению информации во втором полушаге настройки.

Второй полушаг настройки начинается с момента поступления сигналов на входы П2, СИЗ и возобновления сигнал на входе ПО коммутирукнцей системы. Повторное появление сигнала на входе ПО разрешает дальнейшую поразрядную передачу настроечной информации из регистров 5,М. Оставшаяся в регистрах 5.М. настроечная информация представляет собой адреса Р. Эти адреса, поступив на входы V.Z.m., проходят через элементы И 20 в ячейках 4.R.M. по линиям связи D.r.Z. через элементы И 29, подготовленные сигналом с входа П2, на линию связи С.Х.г. С линии связи С.Х.г. адреса р поразрядно поступают на входы узлов сравнения 24 в ячейках 10,Z.X. и 36 в ячейках 13.Р.Х.г. С другой стороны на вторые входы узлов сравнения 24 поступают адреса по линиям связи jD.r.Z. из регистров 5.М. различных ячеек I.Z. На тех узлах сравнения 24 на входах которых имеется разрешающий сигнал с прямьгх выходов триггеров 25, поразрядное сравнение адресных кодов продолжится так же, как было описано вьш1е.

На узлы сравнения 36 на вторые входы также будут поступать адреса Р Но они будут поступать из элементов памяти 16Р. под управлением сигнала с входа П2 через входы V.X.P. коммутирующей системы. Сравнение первых разрядов в узлах сравнения 36 будет разрешено сигналами, появившимися на входах П2 и СИЗ. Дальнейшее сравнение в узлах сравнения 36 будет вы2648110

полняться так же, как и в узлах сравнения 24. Процесс сравнения адресных кодов закончится после прохождения последних разрядов адресов Р. После J этого снимаются сигналы с входов ПО и П2 коммутирующей системы. В результате этого триггеры 25 и 37, на которые поступили только сигналы равенства из узлов сравнения 24 и 36,

10 будут находиться в прямом состоянии.

/-(ля фиксации найденных каналов связи в ячейках 10.Z.X. формируется сигнал фиксации. Формирование этого сигнала производится теми элемента15 ми И 31, на управляющие входы которых поданы сигналы с прямых выходов триггера 25. Импульс СИ4 проходит через такие элементы И 31 на соответствующие линии связи D.r.Z. и по

2Q ним поступает на входы элементов И 19 в ячейках 4.R.M. Через элементы И 19, на вторые входы которых подан сигнал с прямого вькода S.m.r. г-го разряда соответствуняцего регистра сдвига 6.М,,

25 сигнал фиксации проходит на прямые входы триггеров 17 и устанавливает последние в прямое состояние. Сигнал с инверсных выходов Т.г.га. триггеров 17 снимается и таким образом через элементы И 7,г. блокируется про- хож;цение настроечной информации через элементы И 20 во всех ячейках 4.R.M., подключенных к одной линии связи D.r.Z. Кроме того, триггеры 17, установленные в прямое состояние, через

35 элементы И8.М. блокируют, прохождение импульса циклического сдвига И 5 на регистры циклического сдвига 6.М.

Если в одной из ячеек 4.R.M.,подключенных к одной линии связи D.r.Z., триггер 17 в процессе фиксации каналов связи был установлен в прямое состояние, то прохождение настроечной информации на эту линию связи разре- шается только через элемент И 21 в

этой ячейке, т.е. постоянно из одного и того же регистра 5.М.

Кроме выполненных действий, на втором полушаге настройки коммутирующей системы выполняется подгото50 вительная работа для вьшолнения следующего шага. Подготовка заключается в сдвиге, например в сторону старших разрядов, содержимого незаблокиро- ванньк элементами И 8.М. регистром

55 сдвига 6.М. Сдвиг производится пода- . чей импульса на вход СИ5 коммутирующей системы. Пусть в результате сдвига единица, записанная ранее в г -ом

30

40

разряде регистра сдвига 6.М., перейдет в ()-и разряд и соответственно сигнал с прямого выхода (г -ь1) го разряда этого регистра поступит на вход ячейки 4,г -ь1,т,, подключенной к линии связи D,r -i-1.Z. Если к этой линии связи подключена ячейка 4.R.M, (г г -bl) , в которой триггер 17 находится в прямом состоянии, то никаких изменений в ячейках 4.г -ь1,т. не произойдет. Если же среди ячеек 4.R,M., подключенных к линии связи D..Z., не существует узла с находящимся в прямом состоянии триггером 17, то элемент И 20 ячейки 4.,m. будет подготовлен к передаче настроечной информации с выхода V.Z.m. на линию связи D.r -bl.Z.

В результате выполненных действий коммутирующая система готова к следующему шагу настройки, на котором проверяется возможность построения заблокированных на текущем шаге настройки каналов связи через другие блоки 10.Z.X. промежуточного каскада.

Очередной шаг настройки выполняется в основном точно так же, как и описанный первый шаг. Отличие состоит лишь в том, что к зафиксированным на предыдущих шагах каналам связи ячейкам lO.Z.X. могут подключать новые ветви, если по ранее зафиксированным каналам связи и по новым ветвям поступает одинаковая настроечная информация. При этом для. ранее зафиксированных каналов настроечная информация поступает из соответствующи регистров 5.М. по следующему маршруту: выход V.Z.m. коммутирующей системы, элемент И 21 ячейки 4.R.M. с триггером 17 в прямом состоянии, линия связи D.r.Z., элемент И 29 в ячейке 10.Z.X. с триггером 26, находящимся в прямом состоянии, линии связи С.Х.Г., входы соответствующих узлов сравнения 24. Настроечная информация для новых ветвей поступает по последующим маршрутам: регистры 5.М., выходы V.Z.m. коммутирующей системы, незаблокированные элементы И 20, линии связи D.r.Z., входы соответствующих узлов сравнения 24. В дальнейшем процесс сравнения идет так жеt как описано ранее. Следует подчеркнуть, что состояние фиксации уже найденного канала связи в коммутирующей системе подтверждается на каждом шаге настройки.

После выполнения R шагов настройки в .неблокируемой трехкаскадной коммутирующей системе будут зафиксированы все требуемые по программе коммутации каналы связи.

В режиме передачи информации, который начинается подачей на вход П4 соответствующего сигнала, информация проходит с входа И.Х.Р. через линии

связи, элемент И 33, линию связи D.r.Z., элемент И 22 на выход V.Z.m. коммутирующей системы.

Для общей разборки каналов связи в коммутирующей системе необходимо

подать импульс на вход СИО. В результате коммутирующая система перейдет в исходное состояние, как было описано вьш1е. Для частично разборки каналов связи в режиме разборки каналов

Q связи необходимо подать управляющие сигналы на вход ПЗ коммутирующей системы и на тот вход И.Х.р., каналы связи от которого необходимо разобрать. В результате этого через узел 18

J разборки каналов связи будет сброшен в инверсное состояние триггер 17,через узел 28 разборки каналов связи и элемент ИЛИ 23 - триггеры 25 и 26 и через узел 34 разборки каналов связи и элемент ИЛИ 35 - триггер 37 и, таким образом, будут разобраны соответствующие каналы связи через коммутирующую систему.

Предлагаемая трехкаскадная 1чОмму- тирующая система позволяет произво0

5

дить поиск одновременно всех

ta

каналов связи, соединяющих РХ входов с Mz выходами за R шагов работы системы. Шаг работы системы состоит из количества тактов, достаточных для хождения 1о§(р.х.)-разрядного кода идентификатора входа, плюс два до- полнительньк такта, обусловленных алгоритмом работы системы. Таким образом, поиск Mz каналов связи в предла гаемой коммутирукнцей системе займет (log,j(PX) .-ь 2)R тактов.

Формула изобретения

50 1. Трехкаскадная коммутирующая система, содержащая входной, промежуточный и выходной каскады, каждый из которых содержит группу блоков коммутации, входы данных блоков ком55 мутации входного каскада являются информационными входами системы, выходы данных блоков коммутации выходного каскада являются информационными выходами системы, выходы данных каждого блока коммутации входного каскада подключены к соответствующим входам данных блоков коммутации промежуточного каскада, выходы данных каждого блока коммутации промежуточного каскада подключены к соответствующим входам данньк блоков коммута ции выходного каскада, каждый блок коммутации содержит матрицу ячеек коммутации и узел управления, информационные входы.ячеек коммутации каж/дого столбца матрицы объединены и образуют вх.од соответствующего разряда данных блока коммутации,информационны выходы ячеек коммутации каждой строки матрицы объединены и образуют выход соответствующего разряда данных блока коммутации, причем каждый узел . коммутации содержит триггер коммутации и первый элемент И, вькод которого является информационным выходом узла коммутации, первый и второй входы первого элемента И соединены с прямым выходом триггера коммутации и с информационным входом ячейки коммутации соответственно, отличающаяся тем, что, с целью повышения быстродействия системы за сче одновременного поиска нескольких каналов связи, в каждую ячейку коммутации блоков коммутации входного и промежуточного каскадов введены узел сравнения, узел разборки канала связи и элемент ИЛИ, выход которого подключен к входу сброса триггера коммутации, выход которого подключен к входам разрешения узла сравнения и узла разборки канала связи, выходы Равно и Неравно узла сравнения и выход узла разборки канала связи соединены с входом установки триггера коммутации и с первым и вторым входами элемента ИЛИ соответственно, первый информационный вход узла сравнения соединен с информационным входом узла разборки канала связи и с информационным входом ячейки комму- тации, выход первого элемента И подключен к второму информационному входу узла сравнения, третьи входы первых элементов И всех ячеек коммутации соединены с входом разрешения передачи информации системы, ячейка.коммутации блока коммутации

выходного каскада содержит узел разборки канала связи, с второго по четвертый элементы И, причем в каждой ячейке коммутации блока коммутации

5

0

5

0

5

0

5

0

выходного каскада первый вхол, третьего элемента И является входом блокировки ячейки коммутации, выходы третьего и четвертого элементов И ячейки коммутации выходного каскада объединены и подключены к информаци- о 1ному входу узла разборки канала связи и первым входам второго элемента И, второй вход которого объединен с вторым входом третьего элемента И и является входом выборки ячейки коммутации выходного каскада, выход занятости которой соединен с инверсным выходом триггера коммутации, входы установки и сброса которого подключены к выходам узла разборки канала связи и второго элемента И соответственно, третий вход которого соединен с входом фиксации каналов связи системы, прямой выход триггера коммутации ячейки коммутации выходного каскада соединен с входом разрешения узла разборки канала связи

-И с первым входом четвертого элемента И, второй вход которого объединен с третьим входом третьего элемента И и соединен с выходом первого элемента И, третий и четвертый входы соответственно четвертого и третьего элементов И ячейки коммутации выходного каскада объединены и соединены с входом настройки системы, первый и второй входы синхронизации всех узлов разборки каналов связи соединены с входом разборки каналов связи и с входом начальной

.установки системы соответственно, первый и второй входы стробирования узлов сравнения входного каскада соединены с вторыми входами синхронизации и запуска системы соответственно, каждая ячейка коммутации промежуточного каскада дополнительно содержит с второго по четвертый элементы И, элемент запрета и триггер управления; входы установки.и сброса которого подключены к выходам элемента запрета и узла разборки канала ячейки коммутации промежуточного каскада связи соответственно, а выход - к первому входу второго элемента И, выход которого подключен к второму входу первого элемента И, выход которого объединен с выходом третьего элемента И и подключен к второму входу второго элемента И,выход триггера контроля ячейки коммутации промежуточного каскада подключен к первым входам элемента запрета.

15

третьего и четвертого элементов И, выход четвертого элемента И соединен с выходом занятости ячейки коммутации промежуточного каскада, вход признака отсутствия канала связи которой подключен к вторым входам четвертого элемента И и элемента запрета,третий инверсный вход которого является входом признака занятости координатной шины

ячейки коммутации промежуточного каска-JQ ветствующего столбца матрицы блока

да,третий и второй входы второго и третьего элементов И соответстве:нно соединены с вторым входом синхронизации и входом фиксации каналов связи системы соответственно, первый и второй входы синхронизации узлов сравнения ячеек коммутации промежуточного каскада соединены с входом настройки и первым входом запуска системы соответственно, узел управления каждого блока коммутации входного каскада содержит группу элементов памяти идентификаторов входов, выходы которых соединены с входами соответствующих разрядов данных блока коммутации, элемент памяти идентификатора блока коммутации и группу ключей,выходы которых соединены с выходами соответствующих разрядов данных блока коммутации, информационные и управляющие входы ключей группы подключены к выходам разрядов элемента памяти идентификатора блока коммутации, вход считывания которого соединен с первым входом синхронизации системы, входы считывания элементов памяти идентификаторов входов группы объединены и соединены с вторым входом синхронизации системы, узел управления каждого блока коммутации промежуточного каскада содержит группу узлов ускоренного распространения сигнала занятости, труппу триггеров и группу элементов И, причем в каж-- дом узле ускоренного распространения сигнала занятости первые вхо; ,ы элементов И группы подключены к выходам соответствующих триггеров группы, входы сброса которых соединены с входом начальной установки системы, вторые входы элементов И группы соединены с входом разблокировки системы, выходы элементов И группы подключены к входам признака отсутствия канала связи ячеек коммутации блока коммутации промежуточного каскада соответствующего столбца матрицы, выходы занятости ячеек коммутации каждого столбца матрицы промеж точнии ка н1226481 . б

ного каскада подключены к входам соответствующих схем ускоренного распространения сигнала занятости групрьгх подключены к входам установки соответствующих триггеров группы, а остальные выходы - к входам признака занятости координатной шины с второй по последнюю ячеек коммутации соот

коммутации, узел управления каждого блока коммутации выходного каскада содержит группу регистров циклического сдвига, входы синхронизации которых соединены с входом начальной установки системы, первую группу элементов И, выходы которых подключены к последовательным информационным входам соответствующих регистров циклического сдвига группы, выходы разрядов которых подключены к входам выбора ячейки коммутации соответст- вукхцих ячеек коммутации, группу элементов памяти идентификаторов входов системы, выходы которых подключены к соответствующим выходам координатных шин,блоки коммутации выходного каскада, а входы считывания соединены с входом настройки системы, вторую группу элементов И, входы которых .соединены с выходами занятости ячеек коммутации, а выходы - с входами блокировки ячеек коммутации, первые входы элементов И первой группы соединены с входом поиска незаблокированных какалов связи, а остальные входы подключены к выходам занятости ячеек коммутации, причем узел разборки канала связи содержит элемент И, с первого по третий входы которого являются информационным входом, входом разрешения и первым входом синхронизации узла разборки каналов связи соответственно, элемент задержки, элемент ИЛИ, первый вход которого подключен через элемент задержки к выходу элемента И, а второй вход и выход являются вторым входом синхронизации и выходом узла разборки каналов связи соответственно.

2. Система поп.1, отличающаяся тем, что узел сравнения содержит элемент ИЛИ, первый и второй входы которого являются входом разрешения и вторым входом стробиро- вания соответственно, сумматор по модулю два, первый и второй входы которого являются первым и вторым

информационными входами узла соответственно, первый и второй элементы И, выходы которых являются выходами Равно и Неравно узла, выход элемента ШШ подключен к первым входам первого и второго элементов И, вторые входы которых подключены к прямому и инверсному выходам сумматора по модулю два, третий вход первого элемента И является первым входом стробирования узла.

3, Система по П.1, отличающаяся тем, что узел ускорения распространения сигнала занятости

содержит группу элементов ИЛИ, выходы которых являются выходами с второго по старший разряд схемы, выход первого разряда схемы соединен с входом первого разряда схемы, входы первого и второго разрядов схемы подключены к двум первым входам первого элемента ИЛИ, первые входы остальных элементов Ш1И являются входами с третьего по последний разрядов схемы, остальные входы элементов ИЛИ соединены с выходами элементов ИЛИ, номера которых меньше номера данного элемента ИЛИ на величину, равную степени двойки.

.З

3

W

CM /ТЧ1

nt

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| Трехкаскадная коммутирующая система | 1989 |

|

SU1622886A1 |

| Коммутатор для многокаскадных коммутирующих систем | 1988 |

|

SU1582345A1 |

| Специализированный процессор | 1990 |

|

SU1705834A1 |

| Коммутирующая сеть | 1986 |

|

SU1411766A1 |

| Программирующая среда | 1979 |

|

SU813412A1 |

| Устройство для моделирования систем массового обслуживания | 1987 |

|

SU1432551A1 |

| Ячейка памяти | 1984 |

|

SU1233214A1 |

| Коммутирующее устройство | 1973 |

|

SU478439A1 |

| СЕТЬ ДЛЯ МАРШРУТИЗАЦИИ СООБЩЕНИЙ | 1996 |

|

RU2115162C1 |

Изобретение относится к области вычислительной техники и позволяет осуществлять коммутацию данных в многопроцессорных системах. За счет одновременной настройки всех каналов связи система обладает высоким быстродействием. Система содержит входной, промежуточный и выходной каскады соответствующих блоков коммутации X, R, Z (X 1,...,х, R 1,...,г, Z 1,...,z). Входы данных блоков X входного каскада образуют, информационные входы системы, выходы данных блоков Z выходного каскада образуют информационные выходы системы. Система работает в трех режимах: настройки, при кото- ,рой производятся поиск и фиксация ка- в налов связи, передачи информации, полной или частичной разборки,каналов связи.Для управления системой используются одиннадцать управляющих входов системы. 2 з.п.ф-лы, 11 ил. (Л ю to Oi 4 00

f.i.

С. .r

ю

tu

1ГЖг.6

Я9

СМГ

Д2 W5

J6

ПЗ

TW

С.Д.Г

J7

/7

JJ

I4Z. 7

il.l.-l

.2.-/Гд. 1П Tw

15 1... ,Л

.1д.

ггд. г

f.r.A.

Фиг.8

1-2 МО

WигичusСоставитель А.Ушаков Редактор С.Льокова Техред Л.Олейник Корректор Л,Патай

Заказ 2136/50 . Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Фиг 10

Фн&.Л

| Разработка принципов функционирования и структурной организации систем коммутации для многопроцессорных вычислительных структур | |||

| Отчет | |||

| - Таганрог: ТРТИ, 1980, подраздел 3.4.2, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США 4417245, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1986-04-23—Публикация

1984-08-06—Подача