щей инструкции и буферного регистра данных, с вторыми информационными входами первого и второго сумматоров, первый вход первого элемента И соединен с выходом первого элемента, ИЛИ, а выход -.с единичным входом первого триггера, выход которого является первым контролирующим выходом процессора, первый вход первого элемента ИЛИ соединен с первым выходом дешифратора микроопераций и первыми входами второго и третьего элементов И, выход которого является первым выходом запросов процессора, второй вход первого элемента ИЛИ соединен с вторым выходом дешифратора микроопераций и управляющим йходом регистра адреса текущей инструкции, информационный вход которого подключен к выходу первого регистра адреса перехода, управляющим входом соединенного с выходом второго элемента И, управляющим входом первого регистра кода , операции обмена и первым информационным входом первого переключательного элемента, управляющий вход которого соединен с выходом первого регистра кода операции обмена и управляющими входами первого узла шинных формирователей и первого коммутатора, первые информационные входы первого и второго коммутаторов соединены с информационным входом-выходом узла регистров оперативной информации, вторые информационные входы - соответственно с выходами первого и второго узлов шинных формирователей, информаиионные входы которых подключены соответственно к выходам буферного регистра инструкций и буферного регистра данных, информационные входы которых соединены соответственно с выходами первого и второго коммутаторов, а управлякадие входы - соответственно с выходами первого и второго переключательных элементов, информационные входы первого и второго регистров кода операции обмена соединены соответственно с первой и второй группой выходов дешифратора микрооперацийj второй выход которого соединен с первым входом четвертого элемента И,.третий и четвертый выходы - соответственно с первым и вторым входами второго элемента ИЛИ и первыми входами пятого и шестого элементовИ, выход которого соединен с управляющими входами второго регистра адреса перехода, регистра кода операции обмена и первым информационным входом второго переключательного элемента, управляющим входом подключенного к управляющим входам второго коммутатора и второго узла шинных формирователей, выход второго элемента ИЛИ соединен с первым входом седьмого элемента И, выходом подключенного к единичному входу второго триггера, выход котоIporo и выход пятого элемента И являются соответственно вторым контролирующим выходом и выходом запросов процессора, выходи второго регистра адреса перехода и второго регистра кода операции обмена, информационный вход-выход второго узла шинных формирователей и второй информационный вход второго переключательного элемента образуют второй вход-выход процессора, управляющие входы узла регистров оперативной инЛормаиии, второго сумматора, арифметико-логического узла, группа управляющих входор и группа выходов арифметикологического узла соединены соответственно с пятым-седьмым выходами, третьей группой выходов и первой группой входов дешифратора микроопераций, седьмой выход которого подключен к управляю цему входу первого сумматора, а четвертая группа выходов и вторая группа входов - соответственно к первому адресному входу памяти микропрограмм и выходу регистра хранения текущей инструкции, управляющий вход которого соединен с выходом четвертого элемента И, а информационный Вход - с вторым адресным входом памяти микропрограмм и выходом буферного регистра инструкций, выходы первых регистра адреса перехода и регистра кода операции обмена , информаиионный вход-выход первого узла шинных формирователей и второй информационный вход первого : переключательного элемента образуют первый вход-выход процессора,вторые входы первого-седьмого элементов И, нулевые входы первого и второго триггеров, синхронизир1тощие входы памяти программ и дешифратора микроопераций соединены с синхронизирующим входом процессора, выход памяти микропрограмм соединен с третьей группой входов дешифратора микроопераций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления и отладки микропрограмм процессора | 1984 |

|

SU1168937A1 |

УСТРОЙСТВО ДЯЯ ОБМЕНА ИНФОРМАЦИЕЙ, содержащее процессор, элемент ИЛИ-НЕ, выход которого соединен через формирователь синхроимпульсов с синхронизирующим входом процессора, задающий генератор, блок памяти программ, блок памяти данных, блок хранения запросов, включакхаий первый и второй элементы И и первый триггер,причем вход-выход блока памяти программ соединен через первую магистраль с первым входомвыходом процессора, второй вход-выход которого соединен через вторую магистраль с входом-выходом блока памяти данных и входом-выходом устройства, в блоке хранения запросов выход первого элемента И соединен с нулевым входом первого триггера, а первый вход второго элемента И соединен с выходом задающего генератора и первым входом элемента ИЛИ-НЕ, отличающееся тем, что, с целью повьшения быстродействия устройства, в него введен блок приостанова, содержащий два элемента И, и элемент ИЛИ, а в блок хранения запросов введен второй триггер, причем в блоке приостанова выход первого элемента ИЛИ соединен с вторь1М входом элемента ИЛИ-НЕ, а первый и второй входы - соответственно с выходами первого и второго элементов И, первые входы которых подключены соответственно к первому и второму контролирующим выходам прюиессора, а вторые входы - соответственно к единичным выходам первого и второго триггеров и шинам запроса первой и второй магистралей, единичные входы первого и второго триггеров соединены соответственно с первым и вторым выходами запросов процессора, первый вход первого элемента И соединен с выходом задающего генератора, а второй вход - с шиной готовности первой магистрали, второй вход и выход второго элемента И подключены соответственно к шине готовности вт рой магистрали и нулевому входу второго триггера, причем процессор содержит регистр адреса текущей инструкции, первый сумматор, дешифратор микроопераций, два регистра адреса перехода, два регистра кода операций обмена, семь элементов И, два триггера, два элемента ИЛИ, бу.ферный регистр инструкций, два узла шинных формирователей, два коммута- . тора, два переключааельных-.элемента, регистр хранения текущей инструкции и память микропрограмм, сл буферный регистр данных, арифметико-логический узел и узел регистров :о эь оперативной информации, причем первые информационные входы первого и второго сумматоров .соединены соответственно с выходом регистра адреса текущей инструкции и выходом узла регистров оперативной информации, выходы - соответственно с информационными входами первого и второго регистров адреса перехода, информационный вход-выход арифметикологического узла соединен через внутреннюю магистраль процессора с информационным входом-выходом узла регистров оперативной информации, с выходами регистра хранения теку

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах с асинхронным обменом

информации между комплексами системы.

Известны устройства для обмена информаиии, содержатие шифратор, блок синхронизагии обмена, регистр информации, элемент ИЛИ и группу каналов обмена, каждый из которых состоит из блока подготовйи канала, блока обработки запросов, счетчика текущего адреса и блока управления СП,

Недостатками данных устройств являются большие аппаратурные затраты и низкая производительность.

Наиболее близким по технической сущности к предлагаемому является устройство обмена информацией, содержащее процессор, вход-выход которого соединен через магистраль с входом-выходом устройства и входом-выходом блока памяти,формирователь синхроимпульсов, первым входом соединенный с выходом коммутатора, а первьтм выходом - с входом процессора, задающий генератор, подключенный первым выходом к первому входу коммутатора, и блок управления, состоящий из триггера, двух элементов И и элемента ИЛИ, причем первый вход первого элемента И соединен с выходом процессора, второй вход и выход - соответственно с вторыми выходом и входом формирователя синхроимпульсов и первым входом триггера, выходом подключенного к второму входу коммутатора, а вторым входом - к выходу второго элемента И, первый вход которого соединен с вторым выходом задающего генератора, а второй вход - с выходом элемента ИЛИ первый и второй входы которого соединены соответственно с выходом блока памяти и входом готовности устройства Г21 .

Цель изобретения - повьпиение быстродействия устройства.

Поставленная цель достигается тем,что в устройство, содержащее элемент ИЛИ-НЕ, выход которого соединен через формирователь синхроимпульсов с синхрониэйруквдим входом процессора, задающий генератор,блок памяти программ, блок памяти данных, блок хранения запросов, включающий первый и второй элементы И и первый триггер, причем вход-выход блока памяти программ соединен через первую магистраль с первым входом-выходом процессора, второй вход-выход которого соединен через вторую магистраль с звходом-выходом блока, памяти данных и входом-выходом устройства, в блоке хранения запросов выход первого элемента И соединен; с нулевым входом первого триггера, а первый вход второго элемента И соединен с выходом задающего генератора .и первым входом элемента ИЛИ-НЕ, введен блок приостанова, содержащий два

элемента И и элемент ИЛИ, а в блок хранения запросов введен второй триггер, причем в блоке приостанова выход первого элемента ИЛИ соединен с вторым входом элемента ИЛИ-НЕ, а первый и второй входы - соо1;ветстве но с выходами первого и второго элементов И, первые входы которых подключены соответственно к первому и второму контролирующим выходам процессора, а вторые входы - соответственно к единичным выходам первого и второго триггеров и теинам запроса . первой и второй магистралей, в .единичные входы первого и второго триггеров соединены соответственно с первым и вторым выходами запросов процессора, первый вход первого эле°мента И соединен с выходом задающего генератора, а второй вход - с готовности первой магист|)али, второй вход и выход второго элемента И подключены соответственно к IjFHe готовности второй магистрали и, нулевому входу второго триггера, причем процессор содержит регистр адреса текущей инструкции, первый сумматор, дешифратор микроопераций, два регистра адреса перехода, два регистра кода операцииобмена,семь. элементов И, два триггера,два элемента ИЛИ, буферный регистр инструкций, два узла шинных формировс1телей два коммутатора, два переключательных элемента, регистр хранения текущей инструкции, память микропрограмм, буферный регистр данных, арифметико-логический узел и узел регистров оперативной информации, причем первые информационные входы первого и второго сумматоров соединены соответственно с выходом регистра адреса текущей инструкции и выходом узла регистров оперативной информации, выходы - соответственно с информационнь5«1и входами первого и второго регистров адреса перехода, информационный вход-выход арифметико-логического узла соединен через внутреннюю магистраль процессора с информационным входом-выходом узла регистров оперативной информации, с выходами регистра хранения текущей инструкции и буферного регистра ,.с вторыми информационными входами первого и второго сумматоров, первый вход первого элемента И соединен с выходом первого элемента ИЛИ а выход- с единичным входом первого триггера, выход которого является первым контролирующим выходом процессора, первый вход первого элемента ИЛИ соединен с первьт выходом дешифратора микроопераций и первыми входами второго и третьего элементов И, выход которого является первым выходом запросов процессора, второй вход первого элемента ИЛИ соединен

с вторым выходом дешифратора микроопераций и управляющим входом регистра адреса текущей инструкции, информаиионный вход которого подключен к выходу первого регистра адрес перехода, управляющий входом соединенного с выходом второго элемента И, управляющим входом первого регистра кода операций обмена и первым информаиионным входом первого переключательного элемента, управляющий вход которого соединен с выходом первого регистра кода операций обмена и управляющими входами первого узла шинных формирователей и первого коммутатора, первые информационные входы первого и второго коммутаторов соединены с информационным входом-выходом узла регистров оперативной информации, вторые информационные входы - соответственно с выходами первого и второго узлов шинных формирователей, информационные входы которых подключены соответственно к выходам буЛерного регистра инструкций и буферного регистра данных, информационные входы которых соединены соответственно с выходами первого и второго коммутаторов, а управляющие входысоответственно с выходами первого и второго переключательных элементов, информационные входы первого и второго регистров кода операгии обмена соединены соответственно с первой и второй группой выходов дешифратора микроопераций, второй вьтход которог соединен с первым входом четвертого элемента И, третий и четвертый выходы - соответственно с первым и , вторым входами второго элемента ИЛИ и первыми входами пятого и шестого элементов И, выход которого соедине с управляющими входами второго регитра адреса перехода, регистра кода операций обмена и первым информационным входом второго переключательного элемента, управляющим входом подключенного к управляющим входам второго коммутатора и второго узла шинных формирователей, выход второг элемента ИЛИ соединен с первым входом седьмого элемента И, выходом подключенного к единичному входу втрого триггера, выход которого и выход пятого элемента И являются соответственно вторым контролирующим выходом и выходом запросов процессора, выходы второго регистра адреса перехода и второго регистра кода операции обмена, информационный вход-выход второго узла шинных формирователей и второй информационный вход второго переключательного элемента образуют второй вход-выход процессора, управляющие входы узла регистров оперативной информации, второго сумматора, арифметико-логи

ческого узла, группа управляющих входов и группа выходов арифметикологического узла соединены соответственно с пятым-седьмым выходами, третьей группой выходов и первой группой входов дешифратора микроопераций, седьмой выход которого подключен к управляющэму входу первого сумматора, а четвертая группа выходов и вторая группа входов соответственно к первому адресному входу памяти микропрограмм и выходу регистра хранения текущей инструкции, управляющий вход которого соединен с выходом четвертого злемеНта И, а информационный вход с вторым адресным входом памяти микропрограмм и выходом буферного регистра инструкции, выходы первых регистра адреса перехода и регистра кода операции обмена, информационЕ№тй вход-выход первого узла шинных формирователей и второй информационный .вход первого переключательного элемента образуют первый вход-выход пропессора, вторые входы первогоседьмого элементов И, нулевые входы первого и второго триггеров, синхронизирующие входы памяти программ и дешифратора микроопераций соединены с синхронизирующим входом процессора выход памяти микропрограмм соединен с третьей группой входов дешифратора микроопераций.

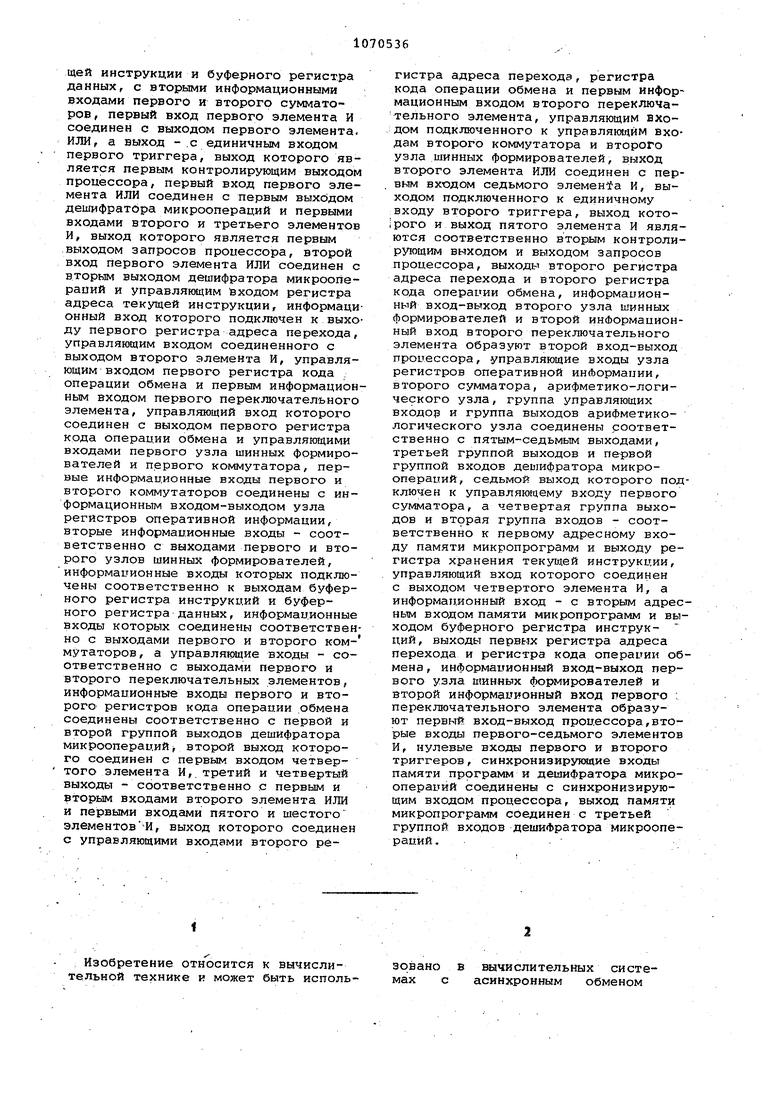

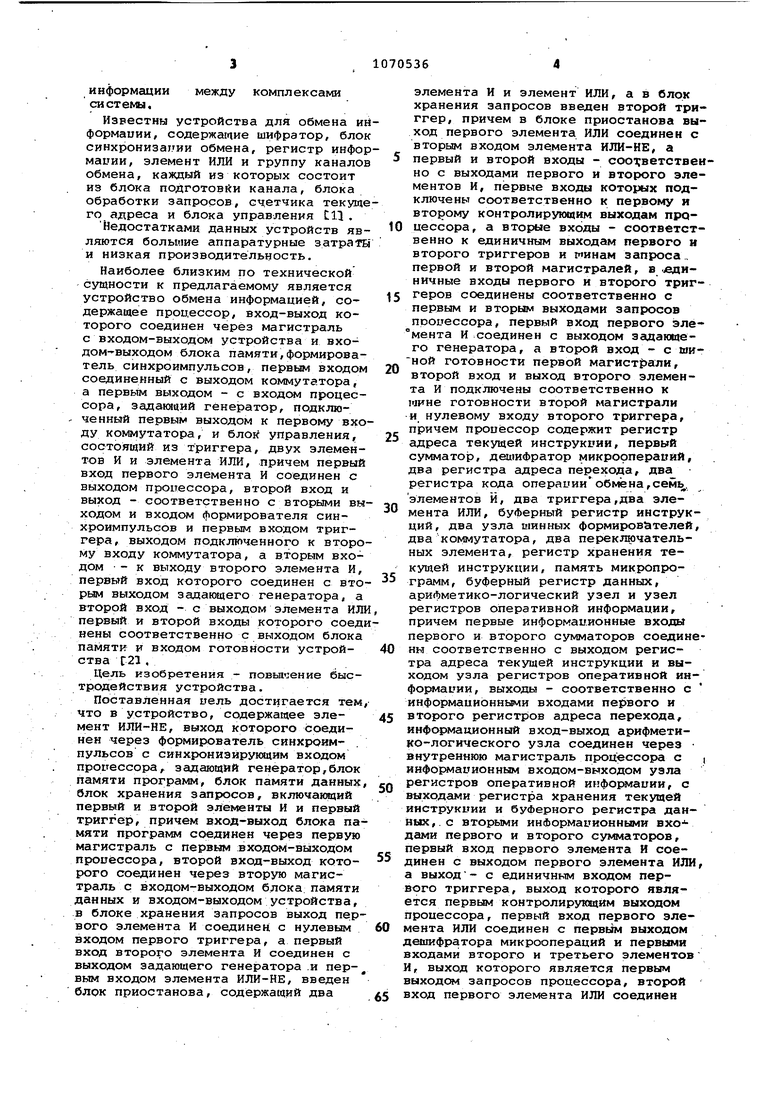

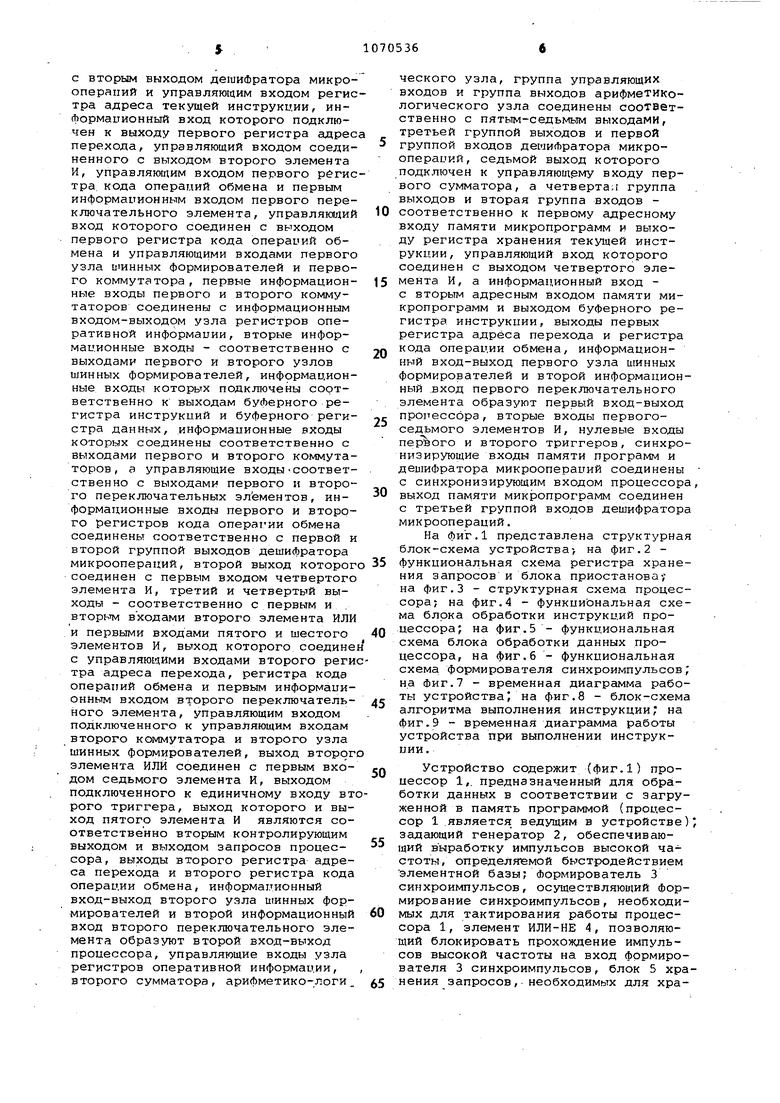

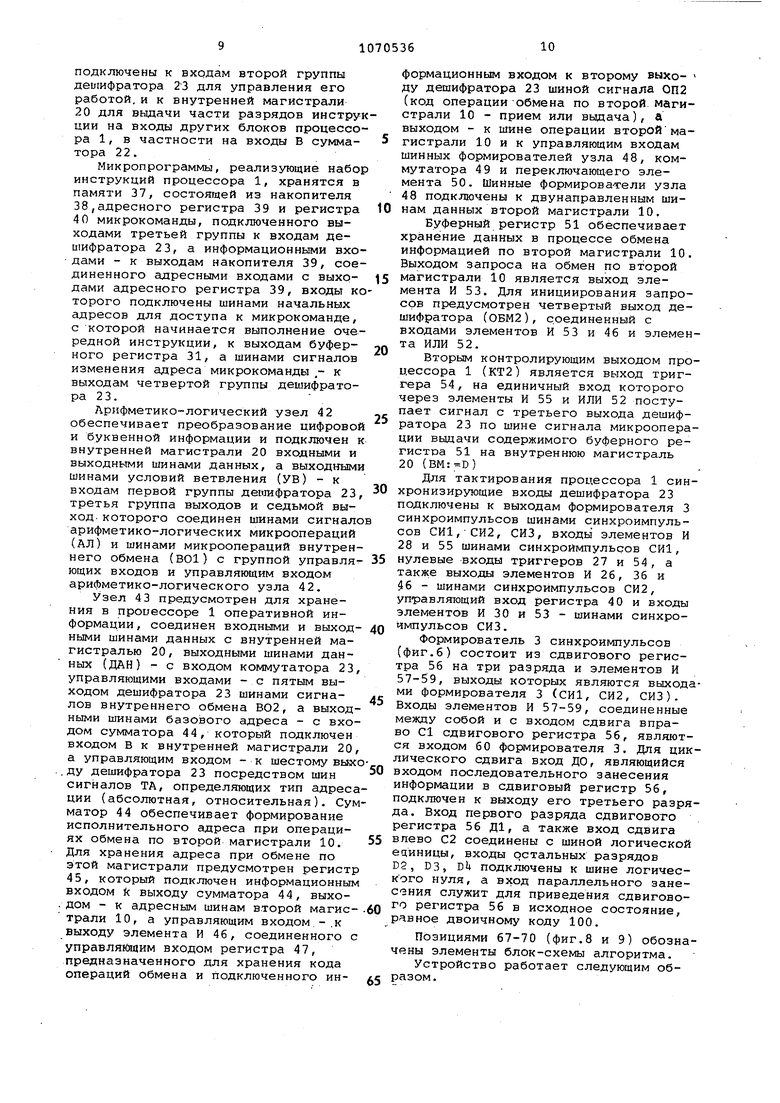

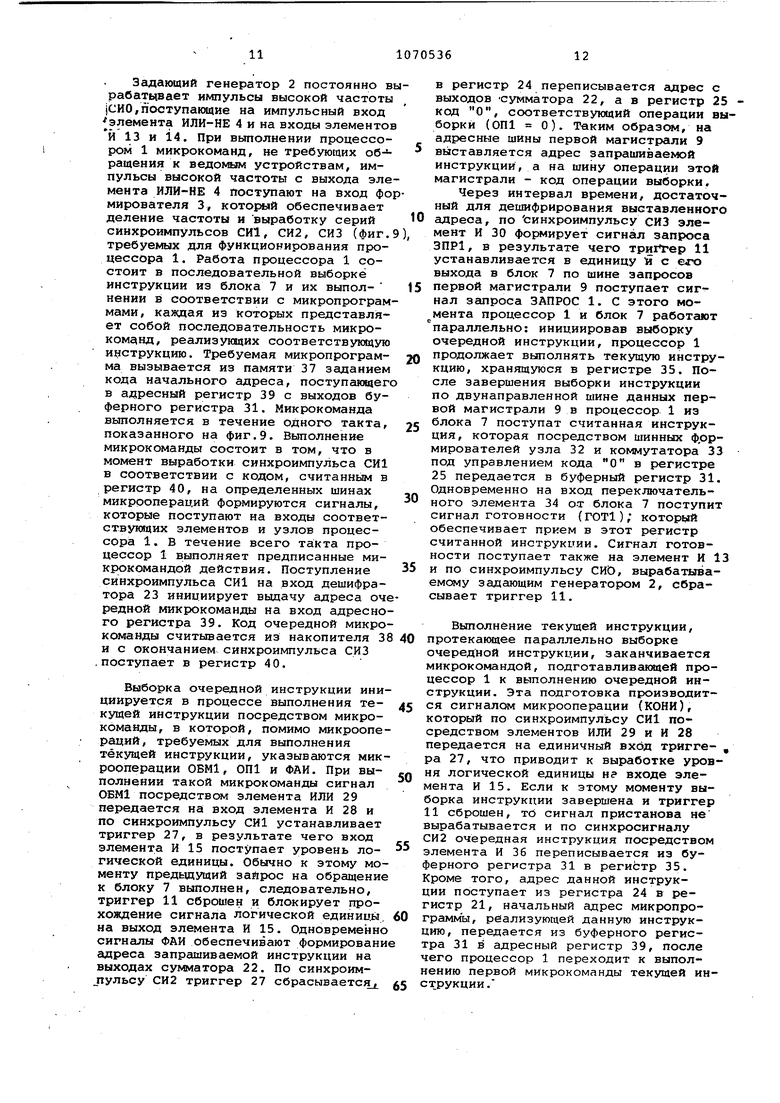

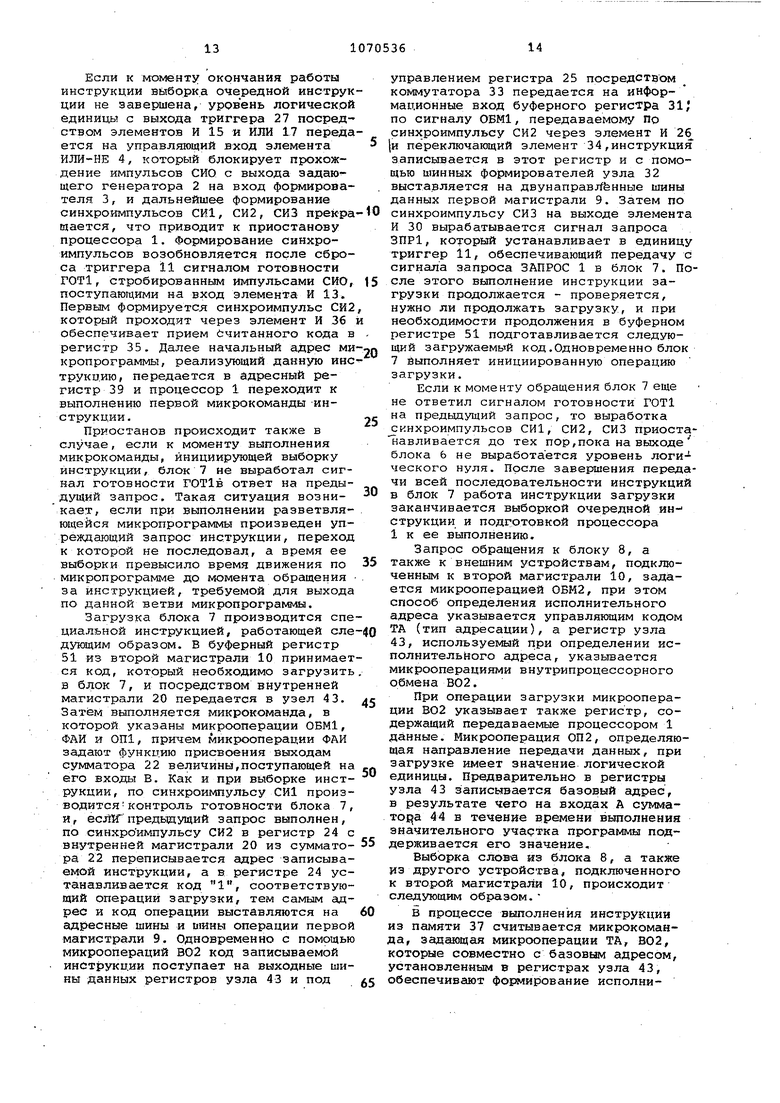

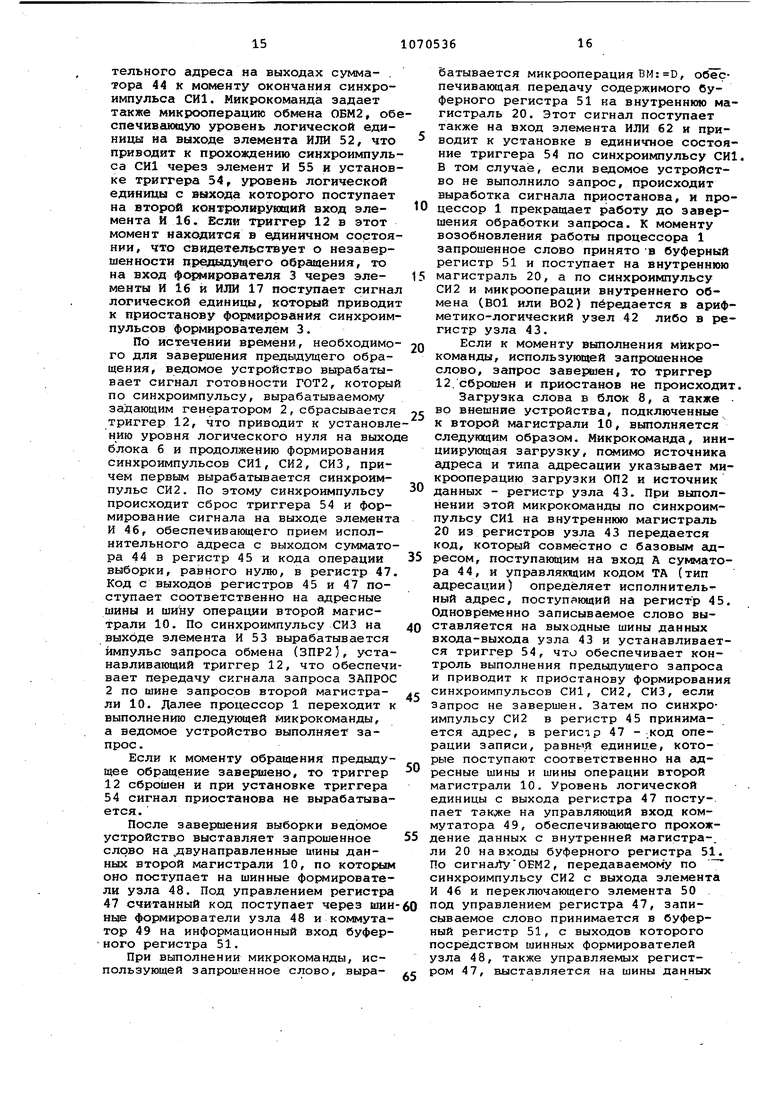

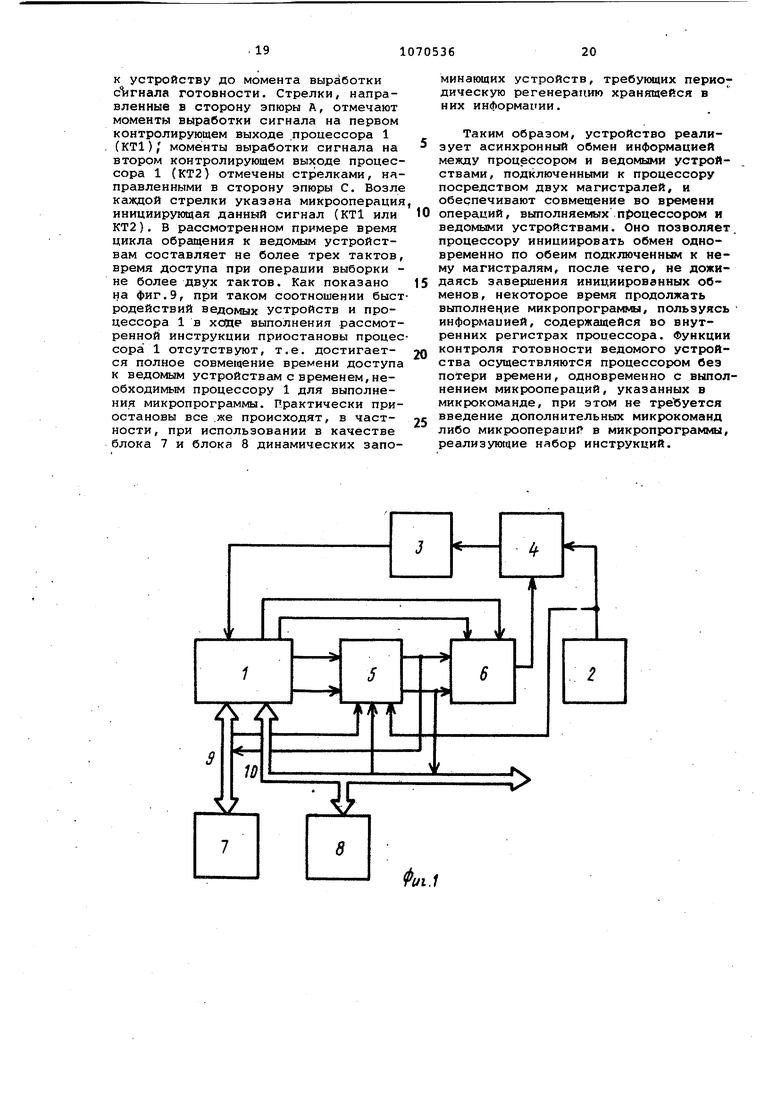

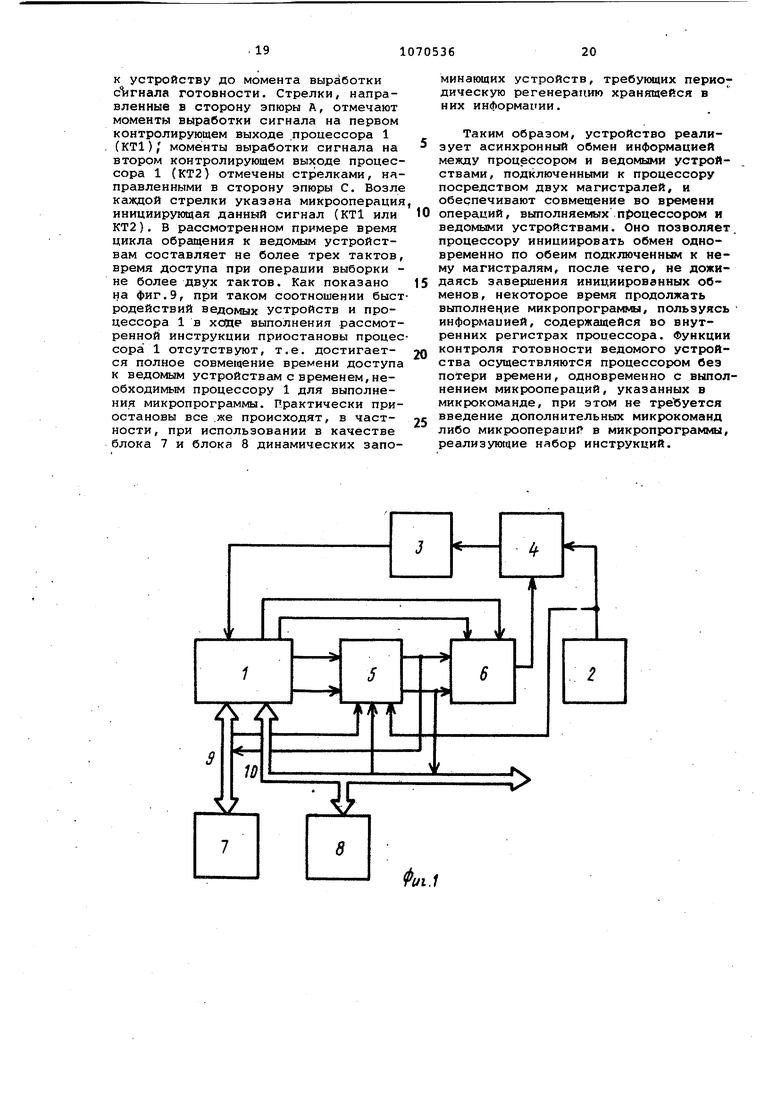

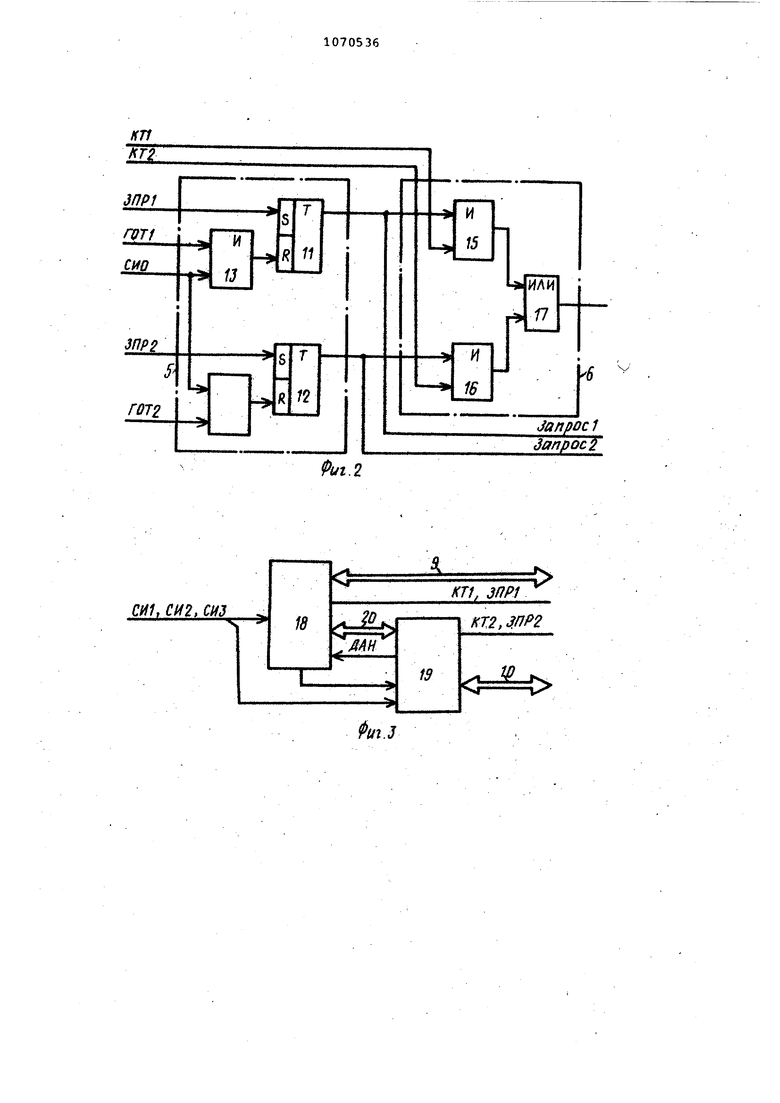

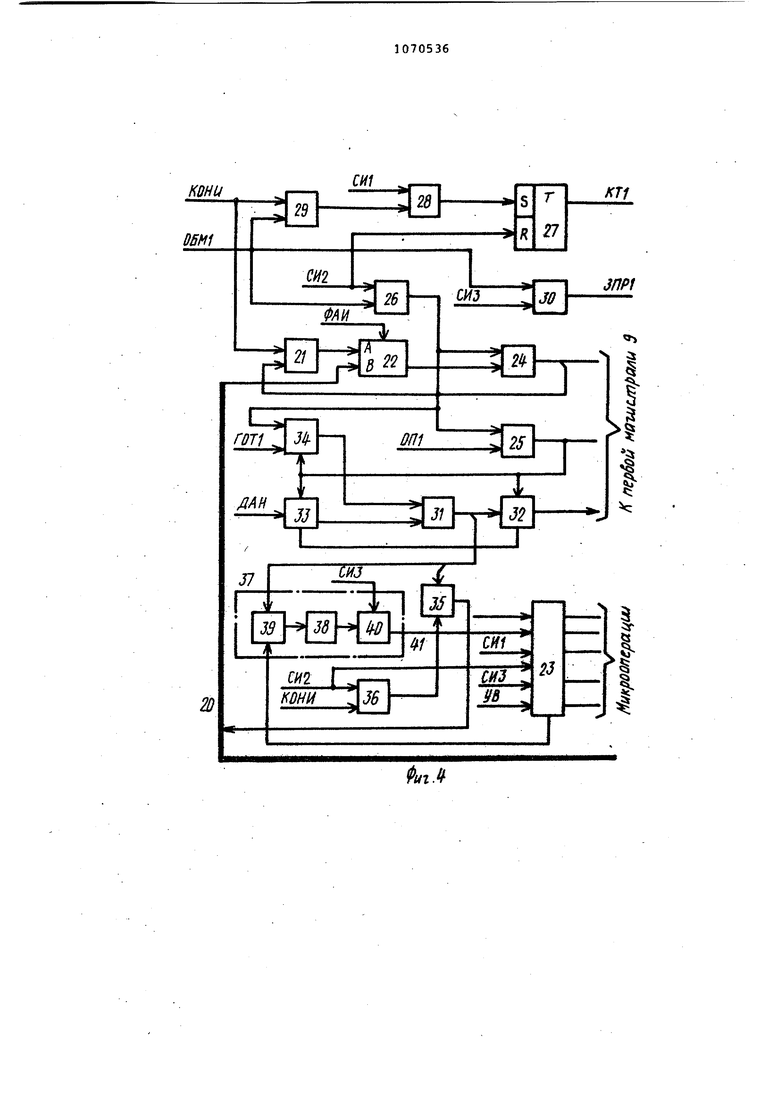

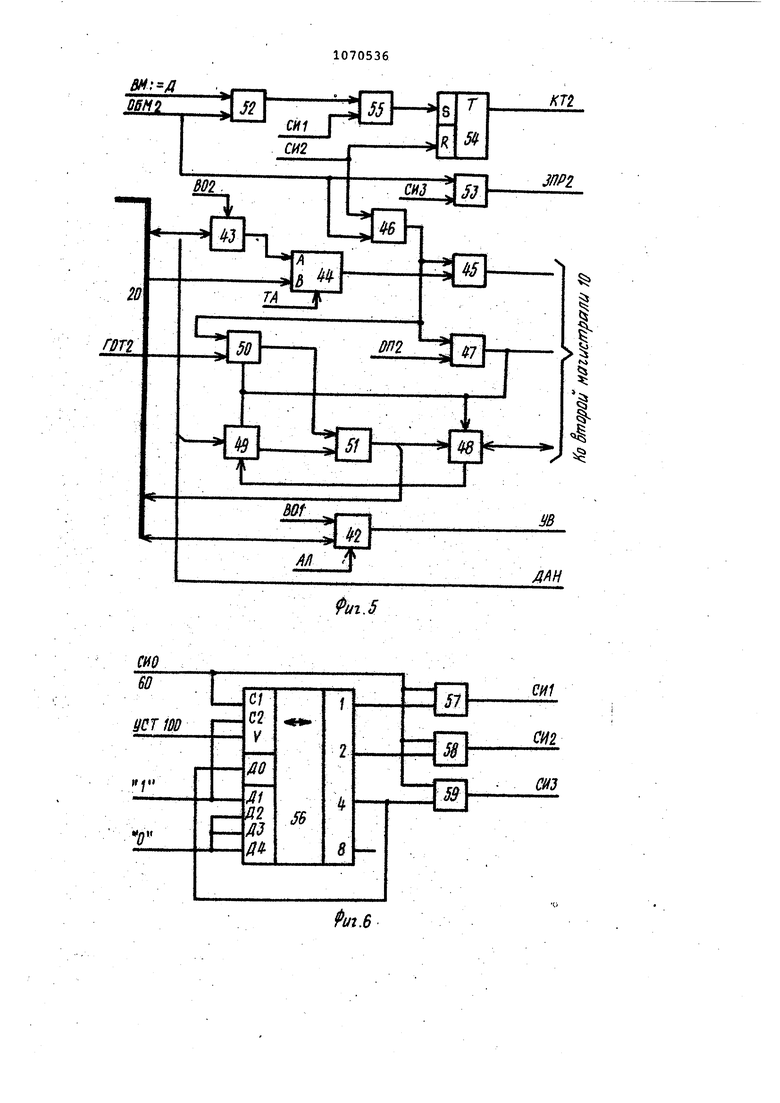

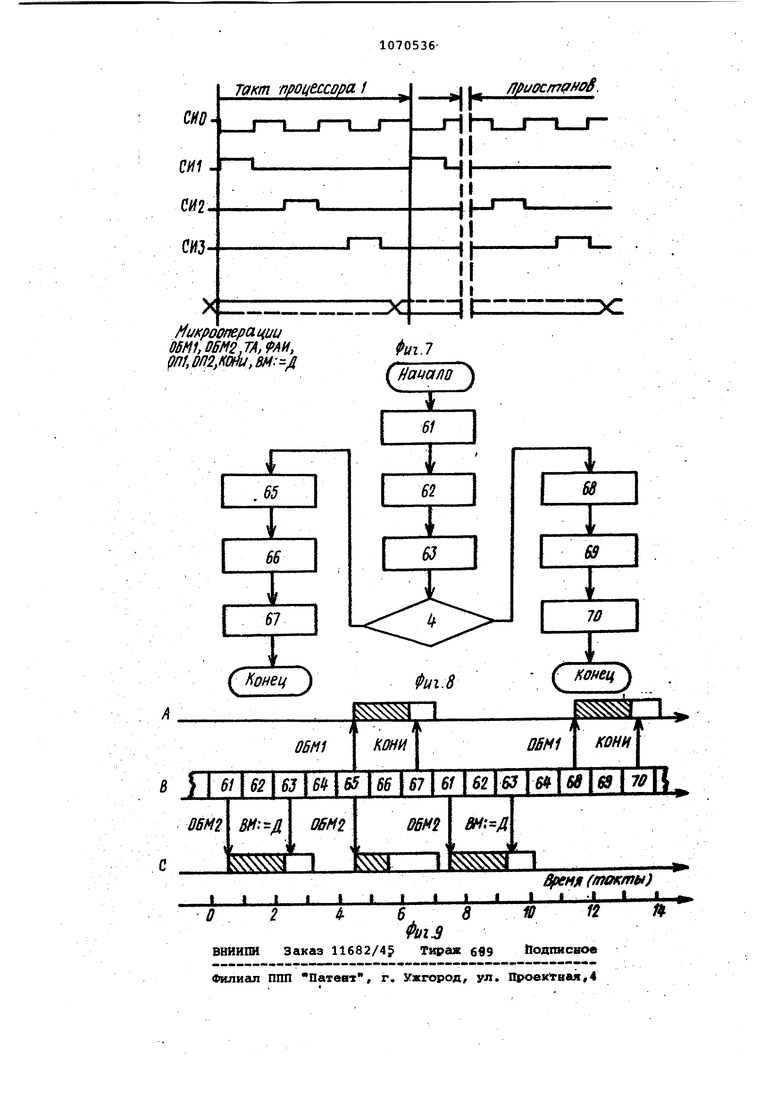

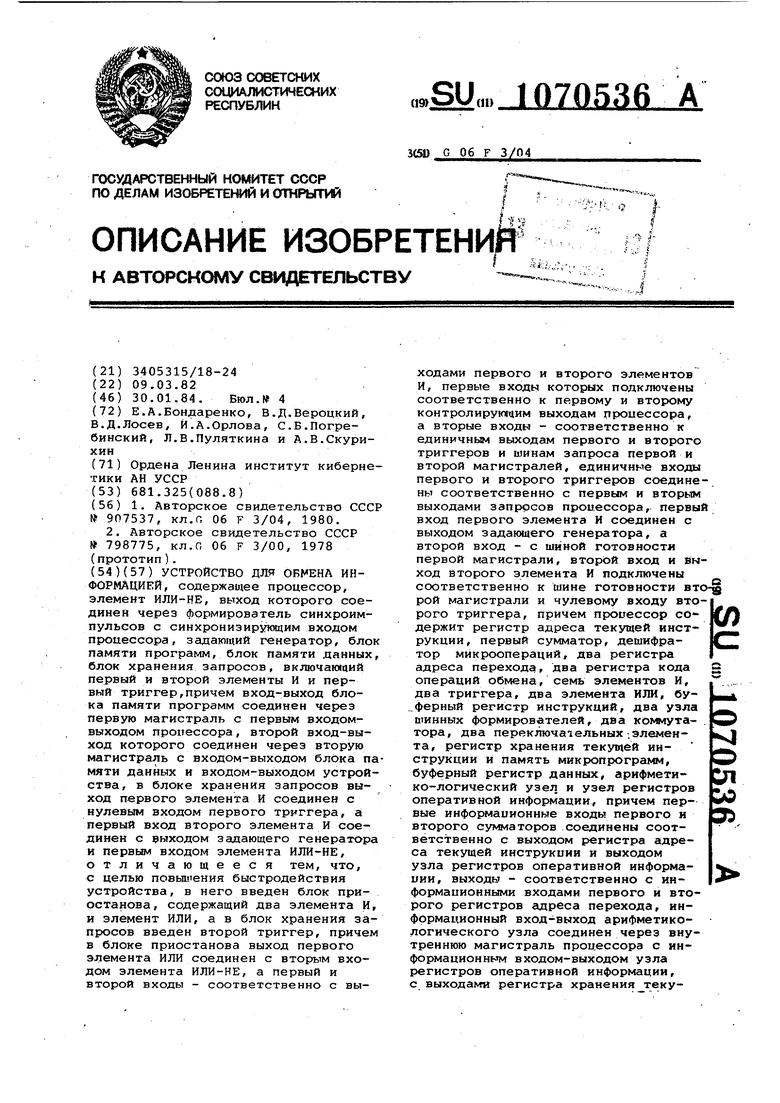

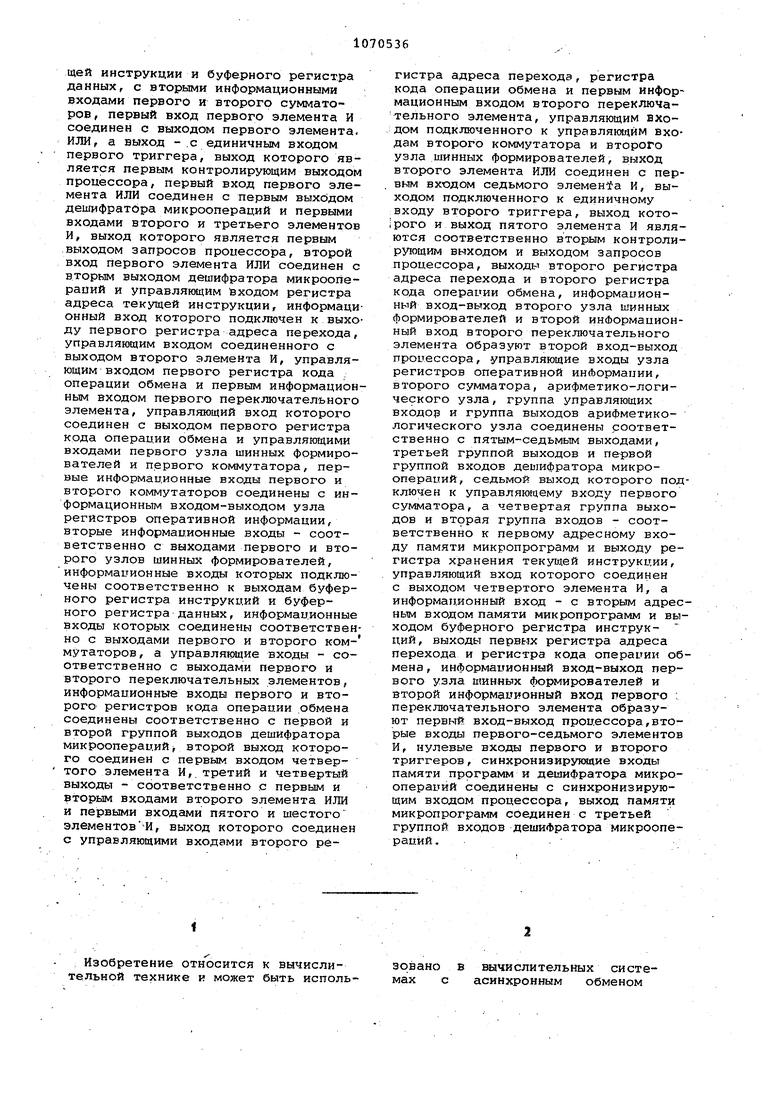

На фигЛ представлена структурная блок-схема устройства) на фиг.2 функциональная схема регистра хранения запросов и блока приостановау на фиг.З - структурная схема процессора; на фиг.4 - функциональная схема блока обработки инструкций процессора; на фиг.5 - функциональная схема блока обработки данных процессора, на фиг.б - функциональная схема формирователя синхроимпульсов; на фиг.7 - временная диаграмма работы устройстваJ на фиг.8 - блок-схема алгоритма выполнения инструкции; на фиг.9 - временная диаграмма работы устройства при выполнении инструкции .

Устройство содержит (фиг.1) процессор 1,. Предназначенный для обработки данных в соответствии с загруженной в память программой (процессор 1 является ведущим в устройстве задающий генератор 2, обеспечивающий выработку импульсов высокой частоты, определяемой быстродействием элементной базы; Формирователь 3 синхроимпульсов, осуществляющий формирование синхроимпульсов, необходимых для тактирования работы процессора 1, элемент ИЛИ-НЕ 4, позволяющий блокировать прохождение импульсов высокой частоты на вход формирователя 3 синхроимпульсов, блок 5 хранения запросов, необходимых для хранения запросов в течение времени их вьтолнения; блок 6 приостанова, осутцествлякиций блокировку подачи импульсов высокой частоты в формирователь 3 на время заверитения ведомым устройством операции обмена; блок 7 памяти программ, предназначенный для хранения программ, записанных на языке инструкций процессора 1; блок 8 памяти данных, необходимых для при ема программ пользователя, хранения промежуточных результатов обработки а также служебной инЛюрмаиии, требуемой для работы операционной системы.

Первая магистраль 9 обеспечивает связь процессора 1 с блоком 7 памяти программ, вторая магистраль 10 с блоком 8 памяти данных. Кроме того,, -по второй магистрали 10 осутцествляётся связь процессора 1 с внешними устройствами (накопителями на магнитных дисках, лентах, дисплеями электромеханическими устройствами ввода-вывода), комплект которых выбирается пользователем. Все внешние устройства подключены параллельно блоку 8.

Блоки и устройства, подключенные к магистралям 9 и 10, являются ведомыми. Каждая из магистралей 9 и 10 включает в себя адресные шины, обеспечивающие передачу адреса ведомому устройству, двунаправленные шины данных для передачи ведомому устройству записываемого слова и для передачи в Процессор 1 запрошенного слова, юину запросов для передачи запрюсов ведомому устройству, шину готовности для передачи процессору 1 сигнала готовности, шину операции для указания ведомому устройству типа выполняемой операции (чтение или запись) и шину начального сброса для приведения ведомого устройства в исходное состояние. BJJOK 5 запросов содержит (фиг.2) триггеры 11 и 12 элементы И 13 и 14. Блок 6 приостанова состоит из элементов И 15 и 16 и элемента ИЛИ 17 (фиг.2).

Процессор 1 содержит два структурных блока (фиг.3): блок 18 обработки инструкций и блок 19 обработки данных, внутреннюю магистраль 20, причем регистр 21 адреса текущей инструкции, первый сумматор 22, дешифратор 23 микроопераций, первые регистр 24 адреса перехода и регистр 25 кода операции обмена, первый эЛемент И 26, первый триггер 27, втот рой элемент И 28, первый элемент ИЛИ 29, третий элемент И 30, буферный регистр 31 инструкций, первые узел 32 шинных формирователей, коммутатор 33, переключательный элемент 34, регистр 35 хранения текущей инструкции, четвертый элемент И 36, память 37 микропрограмм, состоящая из накопителя 38, адресного регистра 39 и регистра 40 микроопераций, шины 41 выхода памяти 37 микропрограмм, образуют блок 18 обработки инструкций процессора (фиг.4). Арифметико-логи5 ческий узел 42, узел 43 регистров оперативной информации, вторые сумматор 44 и регистр 45 адреса перехода, шестой элемент И 46, вторые, регистр 47 кода операции обмена, узел

10 48 шинных формирователей, коммутатор 49 и переключательный элемент 50i буферный регистр 51 данных, второй элемент ИЛИ 52, пятый элемент Н 53, второй триггер 54 и седьмой элемент

5 И 55 образуют блок 19 обработки данных процессора 1 (фиг.5).

Формирователь 3 синхроимпульсов содержит (фиг.6) сдвиговый регистр 56 и элементы И 57-59.

Q Регистр 21 обеспечивает хранение адреса текущей инструкции в течение времени ее выполнения. Дпя формирования адреса очередной инструкции . используется сумматор 22, которой

5 подключен первым инфо1 ацйонным входом (А) к выходу регистра 21, вторым информационным входом (В) - к внутренней магистрали 20, а управляющим входом - к восьмому выходу дешифратора 23 шинеи и сигналов формирования

адреса инструкции (ФАЙ), обеспечивающих выполнение сукматором 22 функций приращения адреса установленного на входе А, на +1 либо на величину, переданную на вход В, при5 своения адресу значения, равного одной из входных величин. Регистр 24 служит для хранения инструкции в процессе обращения к блоку 7 памяти программ. Регистр 25 обеспе0 чивает хранение кода операции обмена (выборка,загрузка) и подключен информационным входом к выходу дешифратора 23 шиной сигнала ОП1, устанавливаквдего тип операции обмена с блоком

5 7. Элемент И 26 обеспечивает формирование сигнала приема кодов в регистры 24 и 25. Выход регистра 24 подключен к адресным шинам-первой магистрали 9 и информационному вхол ЯУ регистра 21.

Первьвч выходом запросов процессора 1 является выход элемента И 30 (ЗПР1), обеспечивающего формирование сигнала запроса на обмен по магистрали 9, для инициирования которого пре5 дусмотрен выход дешифратора 23 ОБМ1.

Для хранения инструкции в процессе ее выполнения предназначен регистр 35, которой подключен ин0 формационным входом к выходу буферного регистра 31, а управляющим входом - к выходу элемента И 36, соединенного первым входом с шиной КОНИ (конец инструкции) второго выхода

5 дешифратора 23. Выходы регистра 35

подключены к входам второй группы дешифратора 23 для управления его работой.и к внутренней магистрали 20 для выдачи части разрядов инструкции на входы других блоков процессора 1, в частности на входы В сумматора 22.

Микропрограммы, реализующие набор инструкций процессора 1, хранятся в памяти 37, состоягдей из накопителя 38,адресного регистра 39 и регистра 40 микрокоманды, подключенного выходами третьей группы к входам дешифратора 23, а информационными входами - к выходам накопителя 39, соединенного адресными входами с выходами адресного регистра 39, входы которого подключены шинами начальных адресов для доступа к микрокоманде, с которой начинается выполнение очередной инструкции, к выходам буферного регистра 31, а шинами сигналов изменения адреса микрокоманды ,- к выходам четвертой группы дешифратора 23.

Арифметико-логический узел 42 обеспечивает преобразование цифровой и буквенной информации и подключен к внутренней магистрали 20 входными и выходными шинами данных, а выходшлми шинами условий ветвления (УВ) - к входам первой группы дешифратора 23, третья группа выходов и седьмой выход, которого соединен шинами сигнало арифметико-логических микроопераций (АЛ) и шинами микроопераций внутреннего обмена (ВО1) с группой управля ющих входов и управляющим входом арифметико-логического узла 42.

Узел 43 предусмотрен для хранения в процессоре 1 оперативной информации , соединен входными и выходными шинами данных с внутренней магистралью 20, выходными шинами данных (ДАН) - с входом коммутатора 23, управляющими входами - с пятым выходом дешифратора 23 шинами сигналов внутреннего обмена ВО2, а выходными шинами базо1вого адреса - с входом сумматора 44, который подключен входом В к внутренней магистрали 20, а управляющим входом - к шестому вьвсо.ду дешифратора 23 посредством шин сигналов ТА, определяющих тип адресации (абсолютная, относительная). Сумматор 44 обеспечивает формирование исполнительного адреса при операциях обмена по второй магистрали 10. Для хранения адреса при обмене по этой магистрали предусмотрен регистр 45, который подключен информационным входом k выходу сумматора 44, выхо. дом - к адресным шинам второй магистрали 10, а управляющим входом - .к выходу элемента И 46, соединенного с управляющим входом регистра 47, предназначенного для хранения кода операций обмена и Подключенного информационным входом к второму выходу дешифратора 23 шиной сигнала ОП2 (код операции-обмена по второЯ магистрали 10 - прием или выдача), а выходом - к шине операции второй магистрали 10 и к управляющим входам шинных формирователей узла 48, коммутатора 49 и переключающего элемента 50. Шинные формирова-тели узла 48 подключены к двунаправленным шинам данных второй магистрали 10.

Буферный регистр 51 обеспечивает хранение данных в процессе обмена информацией по второй магистрали 10. Выходом запроса на обмен по второй магистрали 10 является выход элемента И 53. Для инициирования запросов предусмотрен четвертый выход дешифратора (ОВМ2), соединенный с входами элементов И 53 и 46 и элемента ИЛИ 52.

Вторым контролирующим выходом процессора 1 (КТ2) является выход триггера 54, на единичный вход которого через элементы И 55 и ИЛИ 52 поступает сигнал с третьего выхода дешифратора 23 по шине сигнала микрооперации выдачи содержимого буферного регистра 51 на внутреннюю магистраль 20 ()

Для тактирования процессора 1 синхронизирующие входы дешифратора 23 подключены к выходам формирователя 3 синхроимпульсов шинами синхроимпульсов СИ1,-СИ2, СИЗ, входь элементов И 28 и 55 шинами синхроимпульсов СИ1, нулевые входы триггеров 27 и 54, а также выходы элементов И 26, 36 и 46 - шинами синхроимпульсов СИ2, управляющий вход регистра 40 и входы элементов И 30 и 53 - шинами синхроимпульсов СИЗ.

Формирователь 3 синхроимпульсов (фйг.6) состоит из сдвигового регистра 56 на три разряда и элементов И 57-59, выходы которых являются выходми формирователя 3 (СИ1, СИ2, СИЗ). Входы элементов И 57-59, соединенные между собой и с входом сдвига вправо С1 сдвигового регистра 56, являются входом 60 формирователя 3. Для циклического сдвига вход ДО, являющийся входом последовательного занесения информации в сдвиговый регистр 56, подключен к выходу его третьего разряда. Вход первого разряда сдвигового регистра 56 Д1, а также вход сдвига влево С2 соединены с шиной логической единицы, входы остальных разрядов D2, D3, Di подключены к шине логического нуля, а вход параллельного занесзния служит для приведения сдвигового регистра 56 в исходное состояние, равное двоичному коду 100.

Позициями 67-70 (фиг.8 и 9) обозначены элементы блок-схемы алгоритма.

Устройство работает следующим образом. Задающий генератор 2 постоянно в рабатывает импульсы высокой частоты |СИО,псх;тупающие на импульсный вход элемента ИЛИ-НЕ 4 и на входы элементов Й 13 и 14. При выполнении процессором 1 микрокоманд, не требующих об- ращения к ведомым устройствам, импульсы высокой частоты с выхода эле мента ИЛИ-НЕ 4 поступают на вход фо мирователя 3, который обеспечивает деление частоты и выработку серий синхроимпульсов СИ1, СИ2, СИЗ (фиг. требуемых для Функционирования процессора 1. Работа процессора 1 состоит в последовательной выборке инструкции из блока 7 и их выполнении в соответствии с микропрограм мами, каждая из которых представляет собой последовательность микрокоманд, реализующих соответствующую инструкцию. Требуемая микропрограмма вызывается из памяти 37 заданием кода начального адреса, поступающег в адресный регистр 39 с выходов буферного регистра 31. Микрокоманда выполняется в течение одного такта, показанного на фиг.9. Выполнение микрокоманды состоит в том, что в момент выработки синхроимпульса СИ1 в соответствии с кодом, считанным в регистр 40, на определенных шинах микроопераций формируются сигналы, которые поступают на входы соответствующих элементов и узлов процессора 1. В течение всего такта процессор 1 выполняет предписанные микрокомандой действия. Поступление синхроимпульса СИ1 на вход дешифратора 23 инициирует вьщачу адреса оч редной микрокоманды на вход адресно го регистра 39. Код очередной микро команды считывается из накопителя 3 и с окончанием синхроимпульса СИЗ .поступает в регистр 40. Выборка очередной инструкции ини циируется в процессе выполнения текущей инструкции посредством микрокоманды, в которой, помимо микроопе раций, требуемых для выполнения текущей инструкции, указываются микрооперации ОБМ1, ОП1 и ФАЙ. При выполнении такой микрокоманды сигнал ОБМ1 посредством элемента ИЛИ 29 передается на вход элемента И 28 и по синхроимпульсу СИ1 устанавливает триггер 27, в результате чего вход элемента И 15 поступает уровень логической единицы. Обычно к этому моменту предьщущий зайрос на обращение к блоку 7 выполнен, следовательно, триггер 11 сброшен и блокирует прохождение сигнала логической единицы, на выход элемента И 15. Одновременно сигналы ФАЙ обеспечивают формировани адреса запрашиваемой инструкции на выходах сумматора 22. По синхроим пульсу СИ2 триггер 27 сбрасывается в регистр 24 переписывается адрес с выходов Сумматора 22, а в регистр 25 код О, соответствующий операции выборки (ОП1 0). Таким образом, на адресные шины первой магистрали 9 выставляется адрес запрашиваемой инструкции, а на шину операции этой магистрали - код операции выборки. Через интервал времени, достаточный для дешифрирования выставленного адреса, по синхроимпульсу сИЗ элемент И 30 формирует сигнал запроса ЗПР1, в результате чего триЛ-ер 11 устанавливается в единицу и с выхода в блок 7 по шине запросов первой магистрали 9 поступает сигнал запроса ЗАПРОС 1. С этого момента процессор 1 и блок 7 работают параллельно: инициировав выборку очередной инструкции, процессор 1 продолжает выполнять текущую инструкцию, хранящуюся в регистре 35. После завершения выборки инструкции по двунаправленной шине данных первой магистрали 9 в процессор 1 из блока 7 поступат считанная инструкция, которая посредством шинных формирователей узла 32 и коммутатора 33 под управлением кода в регистре 25 передается в буферный регистр 31. Одновременно на вход переключательного элемента 34 от блока 7 поступит сигнал готовности (ГОТ1); который обеспечивает прием в этот регистр считанной инструкции. Сигнал готовности поступает также на элемент И 13 и по синхроимпульсу СИО, вырабатываемому задающим генератором 2, сбрасывает триггер 11. Выполнение текущей инструкции, протекающее параллельно выборке очередной инструкции, заканчивается микрокомандой, подготавливаняцей процессор 1 к выполнению очередной инструкции. Эта подготовка производится сигналом микрооперации (КОНИ), который по синхроимпульсу СИ1 посредством элементов ИЛИ 29 и И 28 передается на единичный вход тригге- , ра 27, что приводит к выработке уровня логической единицы н входе элемента И 15. Если к этому моменту выборка инструкции завершена и триггер 11 сброшен, то сигнал пристанова не вырабатывается и по синхросигналу СИ2 очередная инструкция посредством элемента И 36 переписывается из буферного регистра 31 в регистр 35. Кроме того, адрес данной инструкции поступает из регистра 24 в регистр 21, начальный адрес микропрограммы, реализующей данную инструкцию, передается из буферного регистра 31 в адресный регистр 39, после его процессор 1 переходит к выполению первой микрокоманды текущей интрукции .

Если к моменту окончания работы инструкции вйборка очередной инструкции не завершена, уровень логической единицы с выхода триггера 27 посредством элементов И 15 и ИЛИ 17 передается на управляющий вход элемента ИЛИ-НЕ 4, который блокирует прохождение импульсов СИО с выхода задаю щего генератора 2 на вход формирователя 3, и дальнейшее формирование синхроимпульсов СИ1, СИ2, СИЗ прекра вдается, что приводит к приостанову процессора 1. Формирование синхроимпульсов возобновляется после сброса триггера 11 сигналом готовности ГОТ1, стробировавным импульсами СИО, поступающими на вход элемента И 13. Первым формируется синхроимпульс СИ2 который проходит через элемент И 36 обеспечивает прием Считанного кода в регистр 35. Далее начальный адрес ми кропрограммы, реализующий данную инс трукциго, передается в адресный регистр 39 и процессор 1 переходит к выполнению первой микрокоманды -инструкции.

Приостанов происходит также в случае, если к моменту выполнения микрокоманды, инициирующей выборку инструкции, блок 7 не выработал сигнал готовности ГОТ1в ответ на предыдуадий запрос. Такая ситуация возникает, если при выполнении разветвляющейся микропрограммы произведен упреждающий запрос инструкции, переход к которой не последовал, а время ее выборки превысило время движения по микропрограмме до момента обращения за инструкцией, требуемой для выхода по данной ветви микропрограммы.

Загрузка блока 7 производится специальной инструкцией, работающей сле дующим образом. В буферный регистр 51 из второй магистрали 10 принимается код, который необходимо загрузить в блок 7, и посредством внутренней магистрали 20 передается в узел 43. Затем выполняется микрокоманда, в которой указаны микрооперации ОБМ1, ФАЙ и ОП1, причем микрооперации ФАЙ задают функцию присвоения выходам сумматора 22 величины,поступающей на его входы В. Как и при выборке инструкции, по синхроимпульсу СИ1 производится контроль готовности блока 7, и, предьщущий запрос выполнен, по синхроимпульсу СИ2 в регистр 24 с внутренней магистрали 20 из сумматора 22 переписывается адрес записываемой инструкции, а в регистре 24 устанавливается код 1, соответствующий операции загрузки, тем самым адрес и код операции выставляются на адресные шины и шины операции первой магистрали 9. Одновременно с помощью микроопераций ВО2 код записываемой инструкции поступает на выходные шины данных регистров узла 43 и под

управлением регистра 25 посредством коммутатора 33 передается на информационные вход буферного регистра 31, по сигналу ОБМ1, передаваемому по синхроимпульсу СИ2 через элемент И 26 |и переключающий элемент 34,инструкция записывается в этот регистр и с помощью шинных формирователей узла 32 выставляется на двунаправленные шины данных первой магистрали 9. Затем по синхроимпульсу СИЗ на выходе элемента И 30 вырабатывается сигнал запроса ЗПР1, который устанавливает в единицу триггер 11, обеспечивающий передачу с сигнала запроса ЗАПРОС 1 в блок 7. После этого выполнение инструкции загрузки продолжается - проверяется, нужно ли продолжать загрузку, и при необходимости продолжения в буферном регистре 51 подготавливается следующий загружаемый код.Одновременно блок 7 йыполняет инициированную операцию загрузки.

Если к моменту обращения блок 7 еще не ответил сигналом готовности ГОТ1 на предыдущий запрос, то выработка синхроимпульсов СИ1, СИ2, СИЗ приоста11авливается до тех пор, пока на выходе блока 6 не выработается уровень логического нуля. После завершения передачи всей последовательности инструкций в блок 7 работа инструкции загрузки заканчивается выборкой очередной инструкции и подготовкой процессора 1 к ее выполнению.

Запрос обращения к блоку 8, а также к внешним устройствам, подключенным к второй магистрали 10, задается микрооперацией ОБМ2, при этом способ определения исполнительного адреса указывается управляющим кодом ТА (тип адресации), а регистр узла 43, используемый при определении исполнительного адреса, указывается микрооперациями внутрипроцессорного обмена В02.

При операции загрузки микрооперации ВО2 указывает также регистр, содержащий передаваемые процессором 1 данные. Микрооперация ОП2, определяющая направление передачи данных, при загрузке имеет значение логической единицы. Предварительно в регистры узла 43 записывается базовый адрес, в результате чего на входах А сумматоца 44 в течение времени выполнения значительного участка программы поддерживается его значение.

Выборка слова из блока 8, а также из другого устройства, подключенного к второй магистрали 10, происходит следующим Образом.

в процессе выполнения инструкции из памяти 37 считывается микрокоманда, задающая микрооперации ТА, В02, которые совместно с базовым адресом, установленным в регистрах узла 43, обеспечивают формирование исполнительного адреса на выходах сумма- . тора 44 к моменту окончания синхроимпульса СИ1. Микрокоманда задает также микрооперацию обмена ОБМ2, обеспечивающую уровень логической единицы на выходе элемента ИЛИ 52, что приводит к прохождению синхроимпульса СИ1 через элемент И 55 и установке триггера 54, уровень логической единицы с выхода которого поступает на второй контролирующий вход элемента И 16. Если Триггер 12 в этот момент находится в единичном состоянии, что свидетельствует о незавершенности предыдущего обращения, то на вход фс ялирователя 3 через элементы И 16 и ИЛИ 17 поступает сигнал логической единицы, который приводит к приостанову формировдния синхроимпульсов формирователем 3.

По истечении времени, необходимого для завершения предыдущего обращения, ведомое устройство вырабатывает сигнал готовности ГОТ2, который по синхроимпульсу, вырабатываемому задающим генератором 2, сбрасывается триггер 12, что приводит к установлению уровня логического нуля на выход блока 6 и продолжению формирования синхроимпульсов СИ1, СИ2, СИЗ, причем первым вырабатывается синхроимпульс СИ2. По этому синхроимпульсу происходит сброс триггера 54 и Формирование сигнала на выходе элемента И 46г обеспечивающего прием исполнительного адреса с выходом сумматора 44 в регистр 45 и кода операции выборки, равного нулю, в регистр 47. Код с выходов регистров 45 и 47 поступает соответственно на адресные шины и шину операции второй магистрали 10. По синхроимпульсу СИЗ на выходе элемента И 53 вырабатывается импульс запроса обмена (ЗПР2), устанавливающий триггер 12, что обеспечивает передачу сигнала запроса ЗАПРОС 2 по шине запросов второй магистрали 10. Далее процессор 1 переходит к выполнению следующей микрокоманды, а ведомое устройство выполняет запрос .

Если к моменту обращения предыдущее обращение завершено, то триггер 12 c6potaeH и при установке триггера 54 сигнал приостанова не вырабатывается.

После завершения выборки ведомое устройство выставляет запрошенное слово на двунаправленные шины данных второй магистрали 10, по которым оно поступает на шинные формирователи узла 48. Под управлением регистра 47 считанный код поступает через шин ные формирователи узла 48 и коммутатор 49 на информационный вход буферного регистра 51.

При выполнении микрокоманды, использующей запрошенное слово, выраЬатывается микрооперация ВМ: D, обеспечивающая передачу содержимого буферного регистра 51 на внутреннюю магистраль 20. Этот сигнал поступает также на вход элемента ИЛИ 62 и приводит к установке в единичное состояние триггера 54 по синхроимпульсу СИ В том случае, если ведомое устройство не выполнило запрос, происходит выработка сигнала приостанова, и процессор 1 прекращает работу до завершения обработки запроса. К моменту возобновления работы процессора 1 запрошенное слово принято в буферный регистр 51 и поступает на внутреннюю магистраль 20, а по синхроимпульсу СИ2 и микрооперации внутреннего обмена (ВО1 или ВО2} передается в арифметико-логический узел 42 либо в регистр узла 43.

Если к моменту выполнения микрокоманды, использу1мчей запрошенное слово, запрос завершен, то триггер 12. сбрсяиен и приостанов не происходи

Загрузка слова в блок 8, а также во внешние устройства, подключенные к второй магистрали 10, выполняется следующим образом. Микрокоманда, инициирующая загрузку, помимо источника адреса и типа адресации указывает микрооперацию загрузки ОП2 и источник данных - регистр узла 43. При выполнении этой микрокоманды по синхроимпульсу СИ1 на внутренннно магистраль 20 из регистров узла 43 передается код, который совместно с базовым ещресом, поступаквдим на вход А сумматора 44, и управляющим кодом ТА (тип адресации) определяет исполнитель ный адрес, поступающий на регистр 45 Одновременно записываемое слово выставляется на выходные шины данных входа-выхода узла 43 и устанавливается триггер 54, что обеспечивает контроль выполнения предьвдущего запроса и приводит к приостанову формирования синхроимпульсов СИ1, СИ2, СИЗ, если Запрос не завершен. Затем по синхроимпульсу СИ2 в регистр 45 принимается адрес, в регисар 47 операции записи, равный единице, которые поступают соответственно на адресные шины и шины операции второй магистрали 10. Уровень логической единицы с выхода регистра 47 посту-, пает на управляющий вход коммутатора 49, обеспечив гиощего прохождение данных с внутренней магистра-, ли 20 на входы буферного регистра 51 По сигналуОЕМ2, передаваемому по синхроимпульсу СИ2 с выхода элемента И 46 и переключающего элемента 50 под управлением регистра 47, записываемое слово принимается в буферный регистр 51, с выходов которого посредством шинных формирователей узла 48, также управляемых регистром 47, выставляется на шины данных второй магистрали 10. Далее по синхроимпульсу СИЗ на выходе элемента И 53 вырабатывается сигнал запроса (ЗПР2), устанавливающий в единичное состояние триггер 12, с выхода которого на шину запроса второй магистрали 10 передается сигнал Запроса ЗАПРОС 2, инициирующий операцию загрузки в блоке 8 или во внешнем устройстве, подключенном к второй магистрали 10 и распознавшем свой адрес, Рассмотрим работу предлагаемого устройства при выполнении процессоро 1 инструкции перемещения слова из одного участка блока 8 в другой. Выполнение этой инструкции, являющейся типичной для программного окру жения, в котором работает устройство обмена информацией, иллюстрирует совмещение времени выполнения инструкции с обработкой запросов ведомыми устройствами. Исходное состояние устройства перед началом выполнения инструкции характеризуется следующим состоянием блоков: адрес выполняемой (текущей) инструкции, полученный в результате выполнения предыдущей инструкции, хранится в регистрах 21 и 24, адрес первой микрокоманды текущей инструкции установлен в адресном регистре 39 путем передачи содержимого соответствующего поля буферного регистра 31 в процессе завершения выполнения предыдущей инструкции; управляющие и информационные поля текущей инструкции записаны в регистр 35 путем передачи содержимого соответствующих полей буферного регистра 31 в процессе завершения выполнения пре дьщущей инструкции; на входы А сумматора 44 поступает код базового адреса формирователь 3 находится в со стоянии, предигествующем выработке синхроимпульса СИ1. Каждая нершина блок-схемы микропрограммы, реализующей рассматриваемую инструкцию (фиг. 8 ), соответствует микрокоманде микропрограммы. Ни же приведен алгоритм, в соответствии с которьзм выполняется инструкция, с указанием позиций микрокоманд, соот ветствующих номерам на блок-схеме, действий, производимых микрокомандами, а также микроопераций, требуемых для реали-зации алгоритма. 61.Выборка слова из блока 8 по адресу, определяемому с помощью первого регистра узла 43 {ВО2, ТА:ОБМ2, ). 62.Пересылка сравниваемого кода из поля инструкции в арифметико-логи ческий узел 42 {В01, ВО2): под управ лением микроопераций внутреннего обмена содержимое требуемого поля регистра 35 посредством внутренней магистрали 20 передается арифметикологический узел 42 для последующего сравнения. 63.Выдача слова, прочитанного из блока 8, на внутреннюю магистраль 10 (), сравнение с кодом в арифметико-логическом узле 42 (АЛ). 64.Переход к 65 в случае несравнения, иначе переход к 8 (посредством сигналов изменения адреса микрооперации, передаваемых на входы адресного регистра 39 с выходов дешифратора 23 ). 65.Запись слова в блок 8 по адресу, определяемому с помощью второго регистра узла 43 (В02, ТА, ОБМ2, ); формирование адреса инструкции, к которой следует переходить в случае несравнения (ФАЙ), выборка инструкции по сформированному адресу (ОБМ1, ); 66.Первая модификация адреса в первом регистре узла 43: под управлением микроопераций внутреннего обмена содержимое требуемого регистра посредством внутренней магистрали 20 передается в арифметико-логический узел 42, где модифицируется в соответствии с кодом микроопераций АЛ, затем возвращается в тот же регистр. 67.Первая модификация адреса во втором регистре узла 43 (аналогично 66); конец инструкции (КОНИ): путем переписи из буферного регистра 31 устанавливаются коды в адресном регистре 39 и регистре 35, необходимые для выполнения очередной инструкции. 68.Формирование адреса инструкции, к которой следует цереходить в случае сравнения (ВО2, ФАЙ), выборка инструкции по полученному адресу (ОБМ1, ). 69.Вторая модификация адреса в первом регистре блока регистров 43 (ВО2, ВО1, АЛ) - аналогично 66. 70.Вторая модификация адреса во втором регистре узла 43 (ВО2, ВО1, АЛ), конец инструкции (КОНИ) - ана- , логично 67. На Фиг.9 представлена временная диаграмма работы устройства при выполнении инструкции перемещения слова в блоке 8. На эпюре А прямоугольниками обозначены периоды активности блока 7 памяти программ. Эпюра В определяет время активности процессора 1 в ходе выполнения двух инструкций данного типа, причем при выполнении первой инструкции работает ветвь 654 67, при выполнении, второй инструкции ветвь 68-70 (фиг.8). На,, этой эпюре цифры указывают номера выполняемых микрокоманд. На эпюре С прямоугольниками обозначен периоды активности блока 8. Заштрихованная часть каждого прямоугольника эпюр А и С соответствует времени обработки запроса от момента обращения

к устройству до момента выработки cVfrHafla готовности. Стрелки, направленные в сторону эпюры А, отмечают моменты выработки сигнала на первом контролирующем выходе процессора 1 (КТ1), моменты выработки сигнала на втором контролирующем выходе процессора 1 (КТ2) отмечены стрелками, направленными в сторону эпюры С. Возле каждой стрелки указана микрооперация инициирующая данный сигнал (КТ1 или КТ2). В рассмотренном примере время цикла обращения к ведомым устройствам составляет не более трех тактов, время доступа при операции выборки не более двух тактов. Как показано на фиг.9, при таком соотношении быстродействий ведомых устройств и процессора 1 в ходе выполнения рассмотренной инструкции приостанови процессора 1 отсутствуют, т.е. достигается полное совмещение времени доступа к ведомым устройствам с временем,необходимым процессору 1 для выполнения микропрограммы. Практически приостановы все .же происходят, в частности, при использовании в качестве блока 7 и блока 8 динамических запоЛ Л

W

3

7

минающих устройств, требующих периодическую регенерацию хранящейся в них информации.

Таким образом, устройство реализует асинхронный обмен информацией меящу процессором и ведомыми устройствами, подключенными к процессору посредством двух магистралей, и оберпечивают совмещение во вЕ емени

0 операций, выполняемых процессором и ведомыми устройствами. Оно позволяет, процессору инициировать обмен одновременно по обеим подключенным к нему магистралям, после чего, не дожидаясь завершения инициированных об5менов, некоторое время продолжать выполнение микропрограммы, пользуясь информацией, содержащейся во внутренних регистрах процессора. Функции контроля готовности ведомого устрой0ства осуществляются процессором без потери времени, одновременно с выполнением микроопераций, указанных в микрокоманде, при этом не тре1буется введение дополнительных микрокоманд

5 либо микроопераций в микропрограммы, реализующие набор инструкций.

J

с

ЗПР1

и

11

/J

ЗПР2

.я

П

Г072

Руг.2

И /5

Чили

/7

И /

f

v

Jan рос 1

Запрос

J7

20

.5

такт процессора 1

Микроогкраччи

0SM1,OSM2,TA.AH,

рп1,оп2,кт,вм

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1980 |

|

SU907537A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для обмена | 1978 |

|

SU798775A1 |

Авторы

Даты

1984-01-30—Публикация

1982-03-09—Подача