3

задержки. После того, как первые четыре суммы поступили на выход первой ступени преобразования, переключатели устанавливаются в предыдущее состояние и разности, записанные в основной блок, через вспомогательный блок задермси пост пают на выход канала преобразования. Далее работа первого канала повторяется. Второй и третий канал работают так же, как и первый, только переключатели коммутируются соответственно вдвое и вчетверо чаще. На выходе третьего канала преобразования последовательно получаются коэффициенты преобразования по Уолщу от последовательности, составленной из первых восьми значений входного сигнала, затем от сле.пующнх восьми и т.д. Это устройство отличается сложностью конструкции.

Наиболее близким но технической сущности к изобретению является устройство, содержащее блок управления и в каждом канале два блока задержки и арифметический блок, управляющий вход которого подключен к соответствующему выходу блока управления, вход устройства подключен к входу первого блока задержки и к первому входу арифметического блока первого канала 2. Канал единичного преобразования на первом этапе преобразования содержит первый блок задержки, в котором производится задержка дискретного CHrfia/ra иа время, равное такту следования даскретного сигна.ча. Арифметический блок предназначен для получения сумлты и вхо.шюго я выходного сигналов с первого блока задержки. Второй блок задержки осуществляег задержку разносгно10 сигнала с выхода арифметического блока на время, равное времени задержки в первом блоке задержки, и задержку чисел вдвое больших, чем в первом блоке задержки. Вычодные сиг. it yCTp.n iciBe выдаются таким образом, что суммарный сигнал от арифметического блока и разностный сигнал от второго блока задержки чере/с/гатся с временным интервалом, равным времени задержки н блоках задержки. На каждом последующем этапе преобразования канал единичного преобразования содержит блоки задержки на время в.;ц)ое большее, чем на предыдущем этапе, и дан хранения чисел вдвое больишх, чем на предыдун1ем этапе. Число этапов преобразования зависит от длины, обрабатываемого дискретного сигнала или от порядка преобразова1 ия.

. Блоки задержки выпол)1яются на регистрах сдвига. Для задержки многоразряднь х вдсел необходимо соединять параллельно несколько регистров сдвига. В каждо.м канале единичного преобразования второй блок задержки, служащий /шя задержки разностного сигнала, должен иметь число регастров соединенных параллельно ia ошп( больще, чем первый блок, так как ои должен задерживать числа вл.пос больпню,iCM мерный блок за; ержкл. Яелостап;о. xciro )йспи1 является его сложность и апппрату|-:1 ;.я громоздкое.

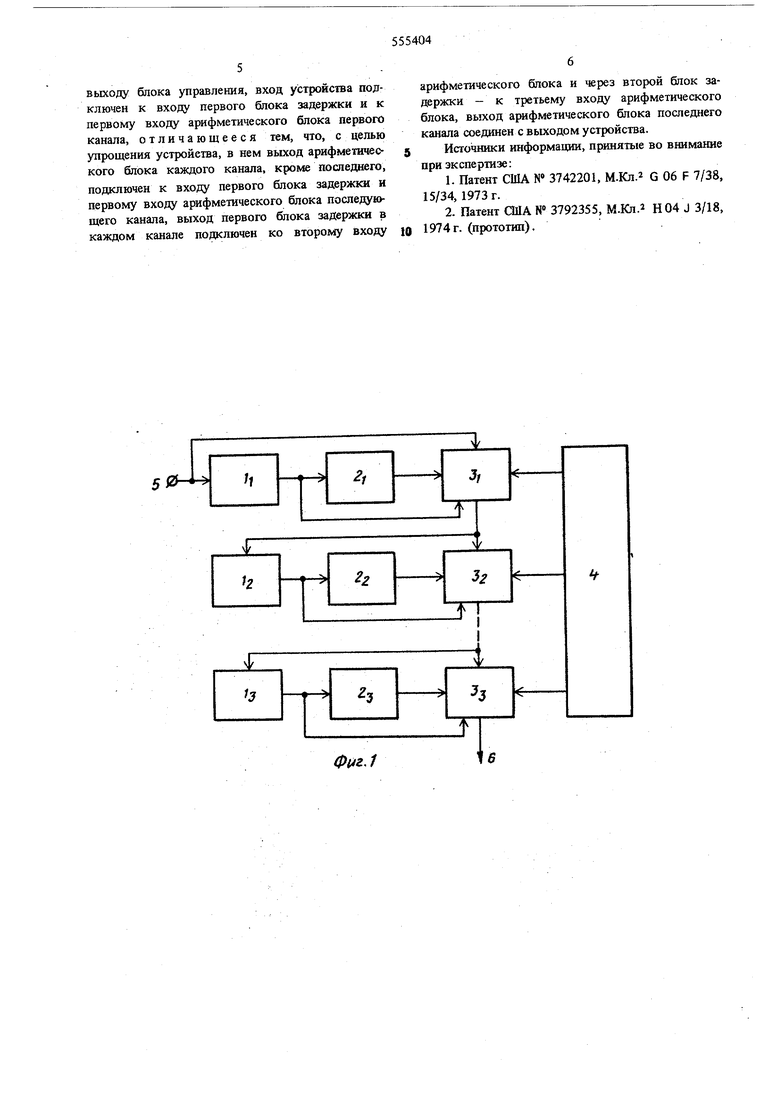

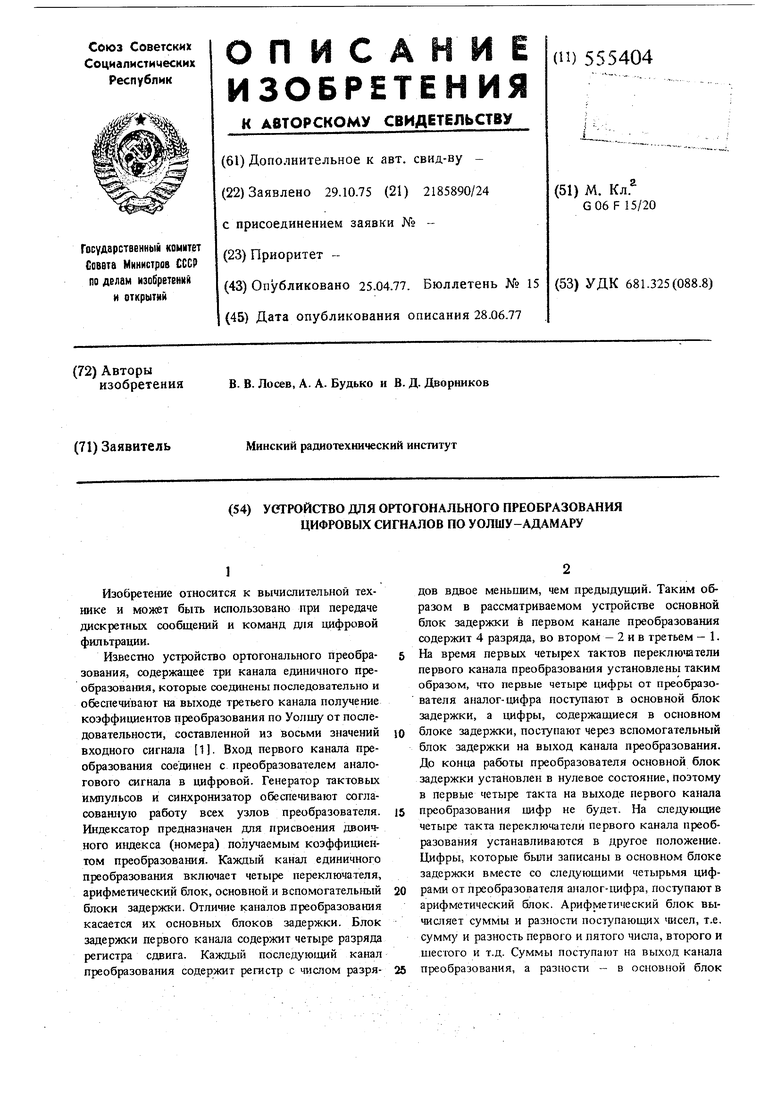

Цель изобретения - упрощение устройства. Это достигается тем, что в устройстве выход арифметического блока каждого канала, кроме последнего, подключен к входу первого блока задержки и первому входу арифметического блока последующего канала, выход первого блока задержки в каждом канале подключен к второму входу арифметического блока и через второй блок задержки - к третьему входу арифметического блока. Выход арифметического блока последнего канала соединен с выходом устройства.

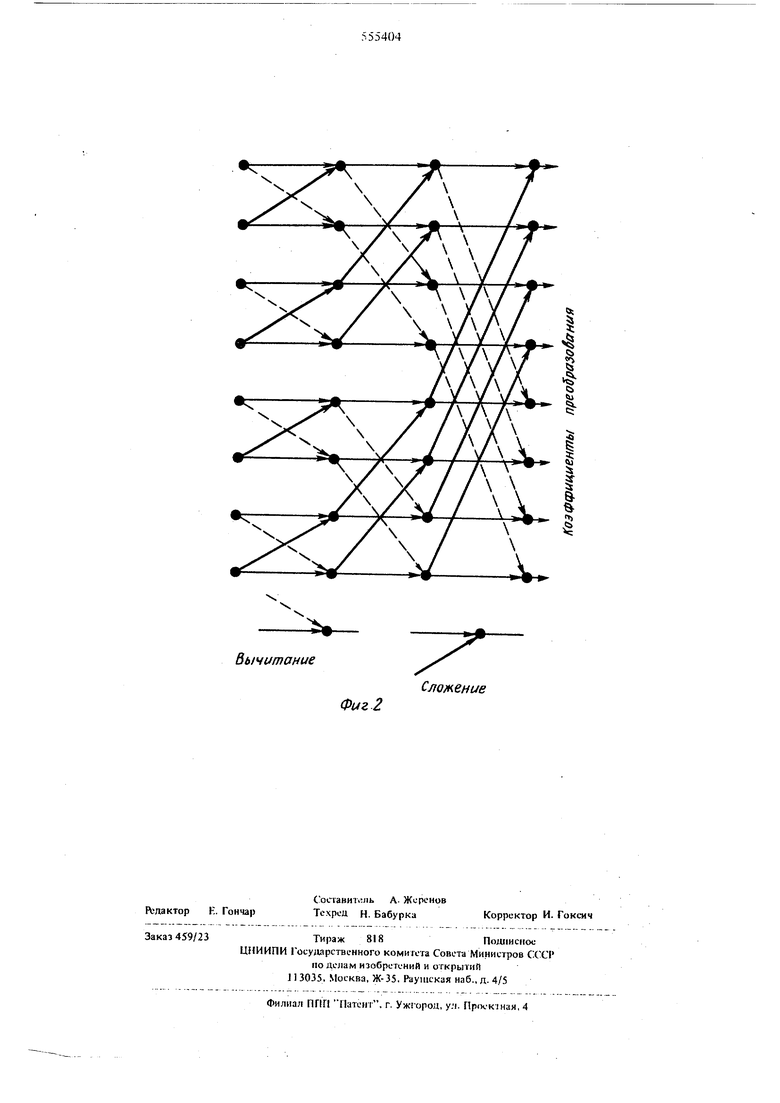

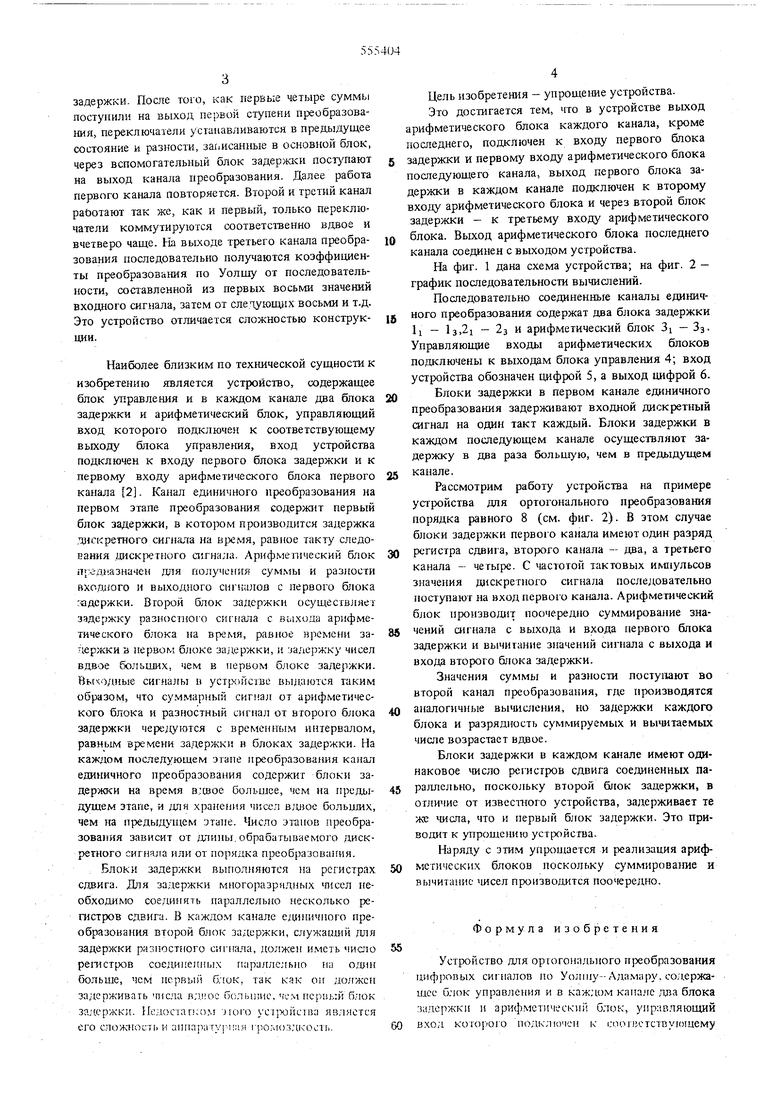

На фиг. 1 дана схема устройства; на фиг. 2 - график последовательности вычислений.

Последовательно соединенные каналы единичного преобразования содержат два блока задержки li - l3,2i - 2з и арифметический блок 3i - ЗзУправляющие входы арифметических блоков подключены к выходам блока управления 4; вход устройства обозначен цифрой 5, а выход цифрой 6. Блоки задержки в первом канале единичного

преобразования задерживают входной дискретный сигнал на один такт каждый. Блоки задержки в каждом последующем канале осуществляют задержку в два раза болыную, чем в предыдущем канале.

Рассмотрим работу устройства на примере устройства для ортогонального преобразования порядка равного 8 (см. фиг. 2). В этом случае блоки задержки первого канала имеют один разряд регистра сдвига, второго канала - два, а третьего канала - четыре. С частотой тактовых им1ульсов значения дискретного сигнала последовательно ностувают на вход первого канала. Арифметический блок нроизводат поочередно суммирование зиачений сигнала с выхода и входа первого блока задержки и вычитание значений сигнала с выхода и входа второго блока задержки.

Значения суммы и разности поступают во

второй канал преобразования, где производятся

аналогичные вычисле)шя, но задержки каждого

блока и разрядность суммируемых и вычигаемых

числе возрастает вдвое.

Блоки задержки в каждом канале имеют одинаковое число регистров сдвига соединенных параш1ельио, поскольку второй блок задержки, в отличие от известаого устройства, задерживает те же шсла, что и первьп блок задержки. Это приводит к упрощешпо устройства.

Наряду с этим упрощается и {реализация арифметичсских блоков поскольку суммировазше и вычитание чисел производится поочеред ю.

Формула изобретения

Устройство для оргогонального преобразования цмф зовых сигналов по Уошиу- Лдамару, содержащее б;юк управления и в каждом капало два блока задержки и арифметический О.юк, уир: вляющий вход кок)К)го подключеп к 1:оои;стс1пу(ощему

выходу блока управления, вход устройства подключен к входу первого блока задержки и к первому входу арифметического блока первого канала, отличающееся тем, что, с целью упрощения устройства, в нем выход арифметического блока каждого канала, кроме последнего, подключен к входу первого блока задержки и первому входу арифметического блока последующего канала, выход первого блока задержки в каждом канале подключен ко второму входу

арифметического блока и через второй блок задержки - к третьему входу арифметического блока, выход арифметического блока последнего канала соединен с выходом устройства.

Источники информации, принятые во внимание при экспертизе:

1.Патент США N 3742201, М.Кл. G 06 F 7/38, 15/34, 1973г.

2.Патент США № 3792355, М.Кл.2 Н04 J 3/18, 1974г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1987 |

|

SU1509930A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Хаару | 1982 |

|

SU1061150A1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Способ сдвига частоты @ сигнала | 1987 |

|

SU1383459A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| СПОСОБ ИЗМЕРЕНИЯ ВРЕМЕНИ ПРИХОДА СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2011 |

|

RU2483319C2 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Устройство для моделирования систем связи | 1976 |

|

SU559240A1 |

| Устройство для контроля работы транспортного средства | 1986 |

|

SU1345222A1 |

Ф14г.1

вычитание

Сло кение

Фиг 2

Авторы

Даты

1977-04-25—Публикация

1975-10-29—Подача