«I

&

(Л

содержащих по два канала 2.1 и 2.2 преобразования, каждый из которых имеет сигнальные 2-1 - 2-2 и 2-3, управляющие 2-4 и 2-5, запрещающий 2-6 и кодов,ый 2-7 входы, сумматор 3, соединенный своими входами с выходами каналов, а выходом - через фильтр 4 с выходом устройства, и умножите-- ли 5 и 6 частоты. Способ предусматривает выполнение операций, обеспе83459

чивающих практически неискаженную передачу формь исходного сигнала, возможность сдвига частоты до f/2 как вверх, так и вниз по отношению к частоте f исходного сигнала, и может найти применение в радиоэлектронике, связи,радиолокации и измерительной тех; нике. Работа устройства поясняется по временным диаграммам, приведенным в описании изобретения. 6 шт.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигнала сдвинутой частоты | 1986 |

|

SU1394426A1 |

| Устройство для программного управления | 1981 |

|

SU960740A2 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1993 |

|

RU2038634C1 |

| Цифровой интегрирующий фазометр | 1983 |

|

SU1173339A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ СИГНАЛОВ | 2002 |

|

RU2228576C2 |

| СТАНЦИЯ ПРИЦЕЛЬНЫХ ПОМЕХ РАДИОЛИНИЯМ УПРАВЛЕНИЯ ВЗРЫВНЫМИ УСТРОЙСТВАМИ | 2005 |

|

RU2292059C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| Цифровой фазовращатель | 1986 |

|

SU1372593A1 |

1

Изобретение относится к радиоэлектронике и может быть использован в устройствах связи, измерительной технике и других областях, где необходимо однополосное преобразование частоты сигнала.

Цель изобретения - сохранение исходной формы сигнала с частотой f.

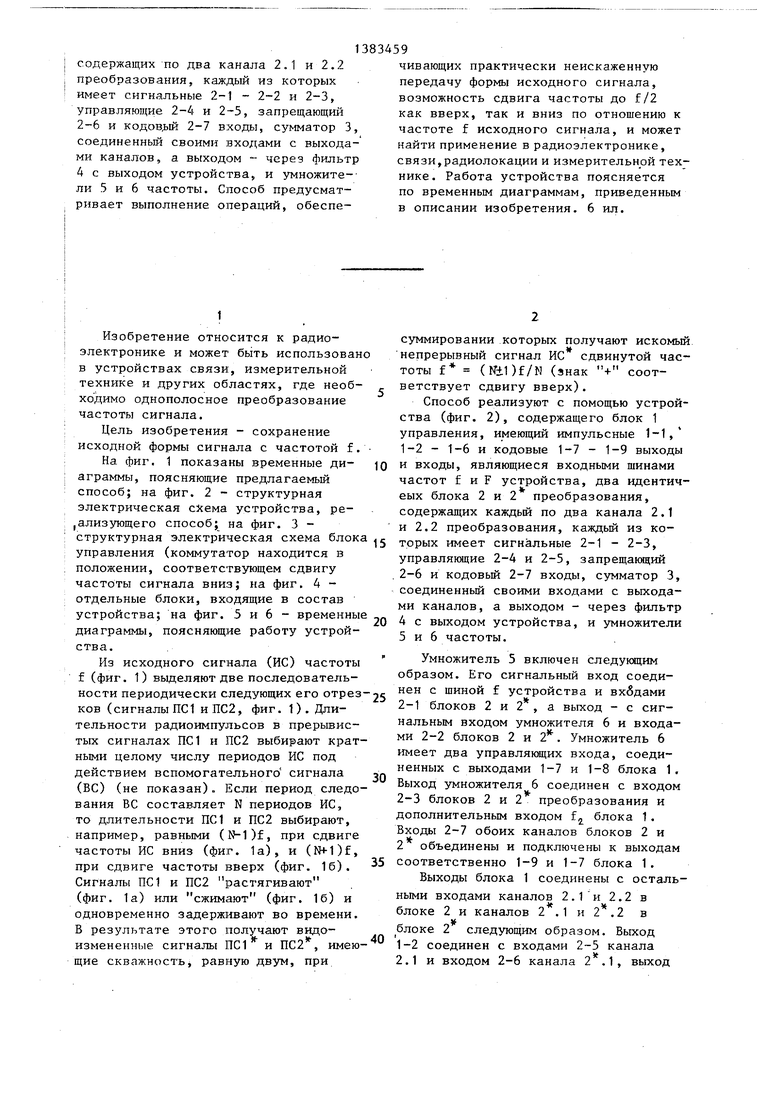

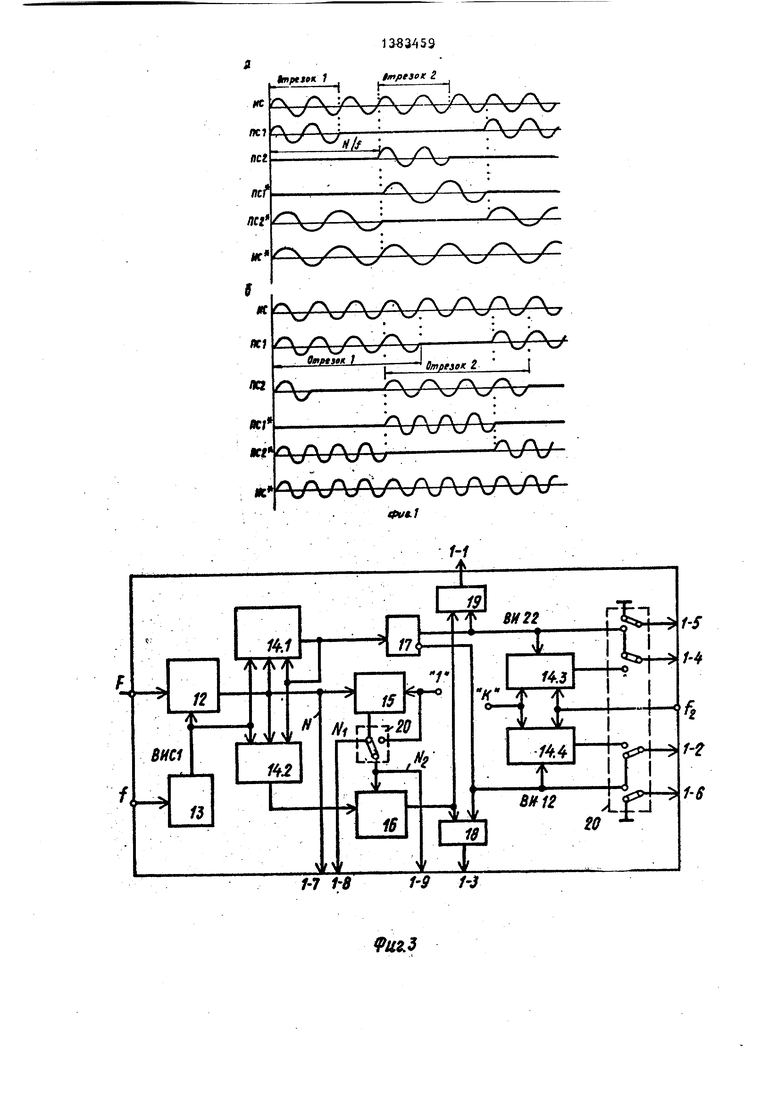

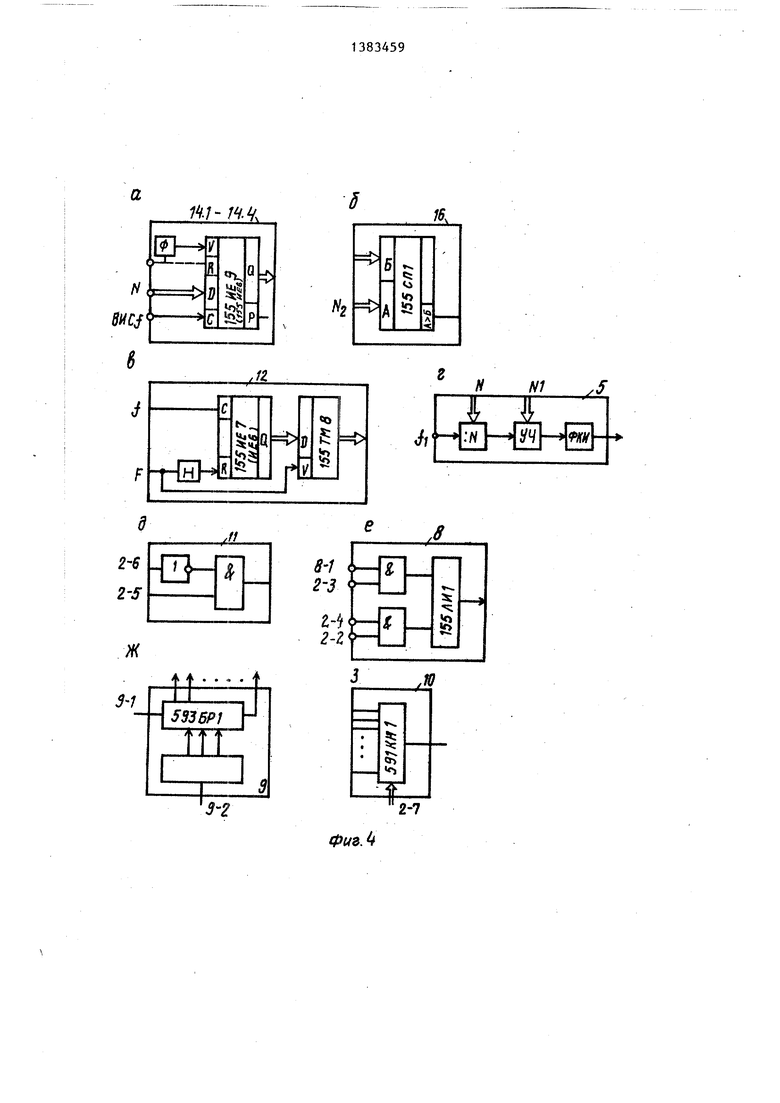

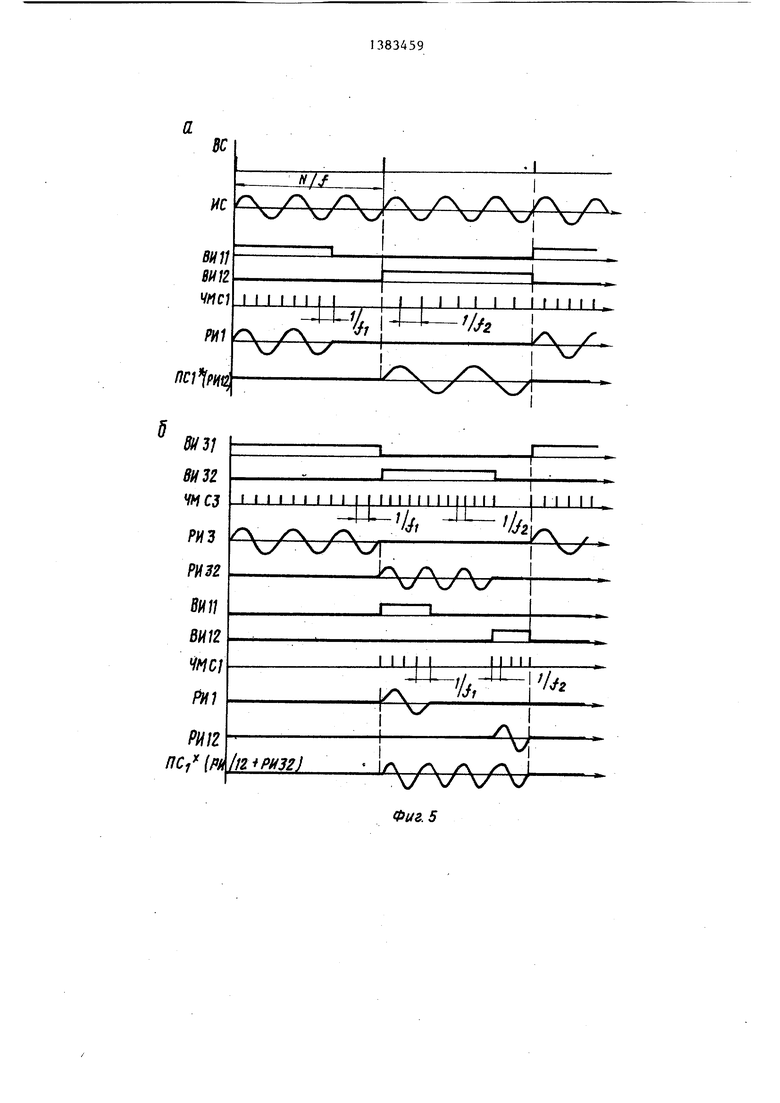

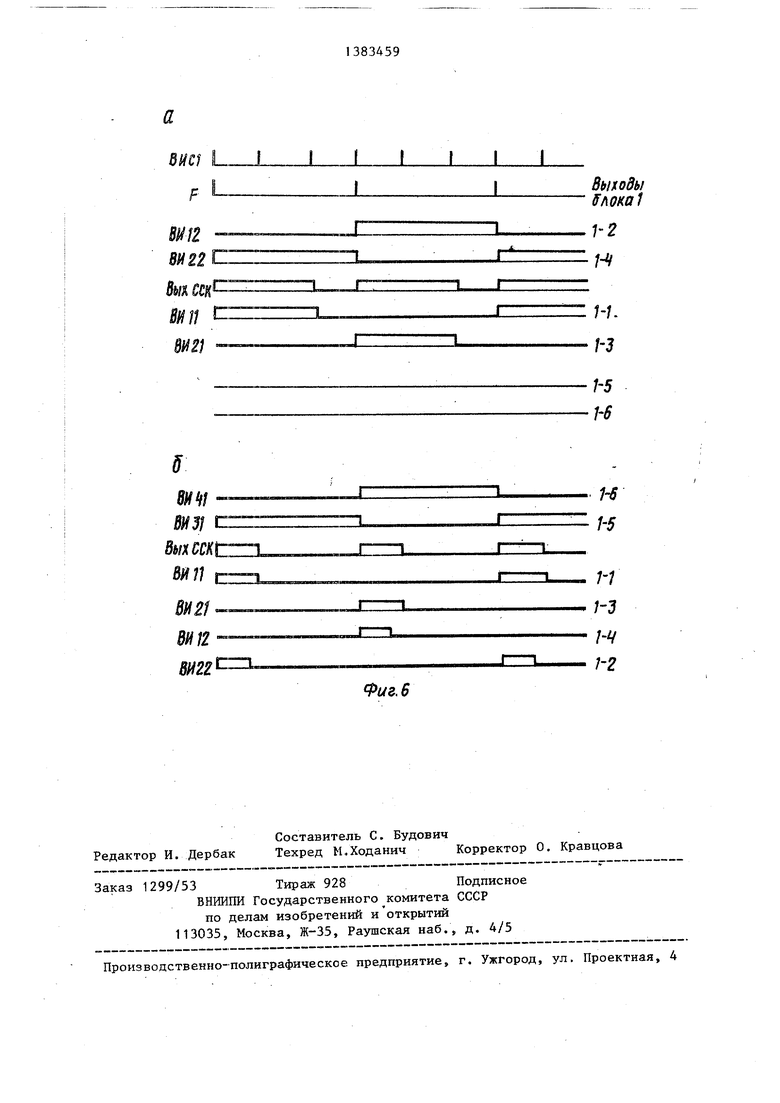

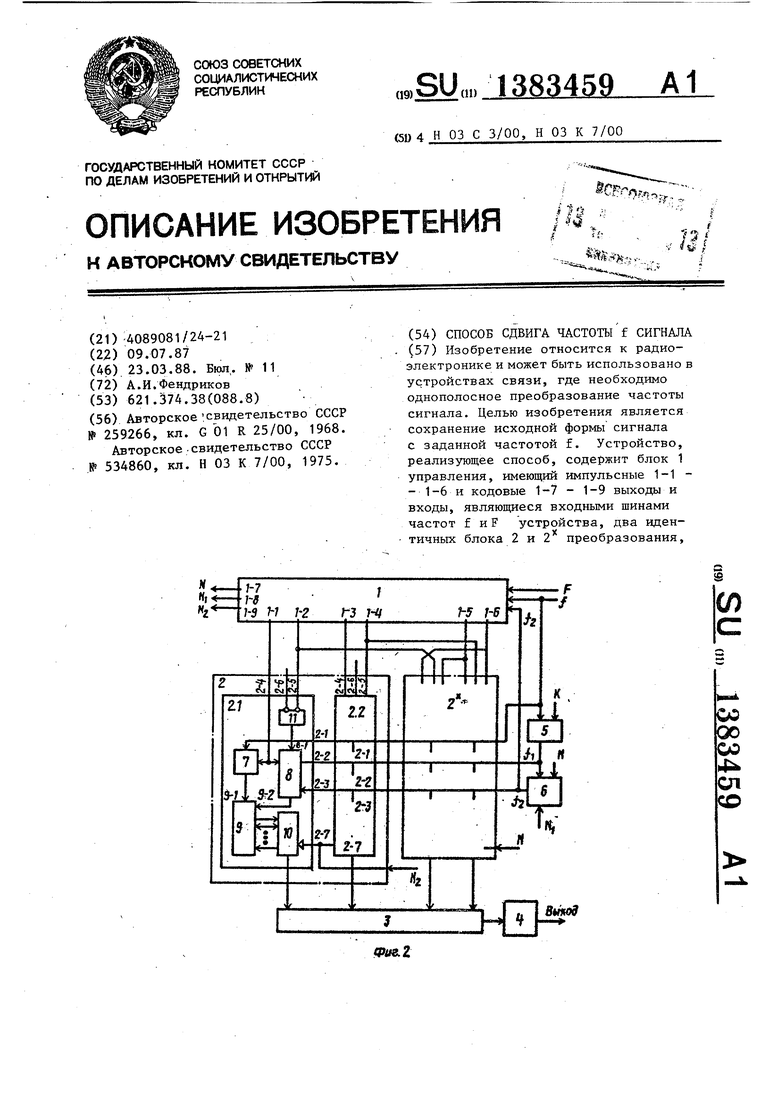

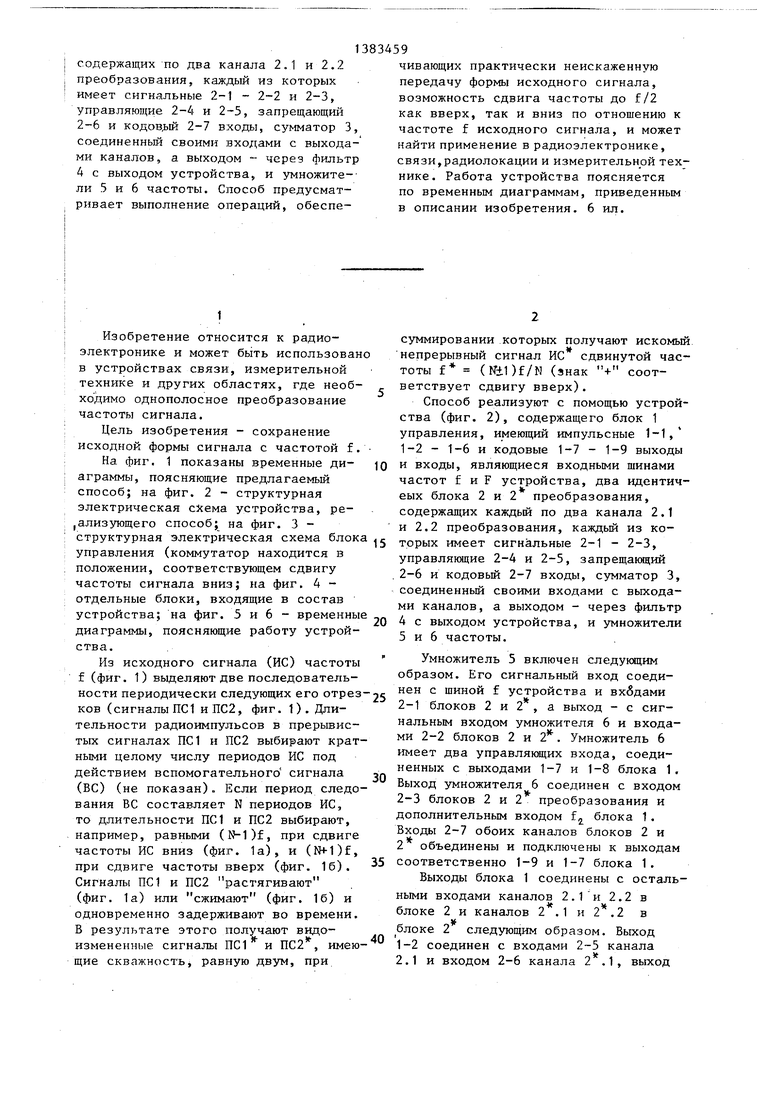

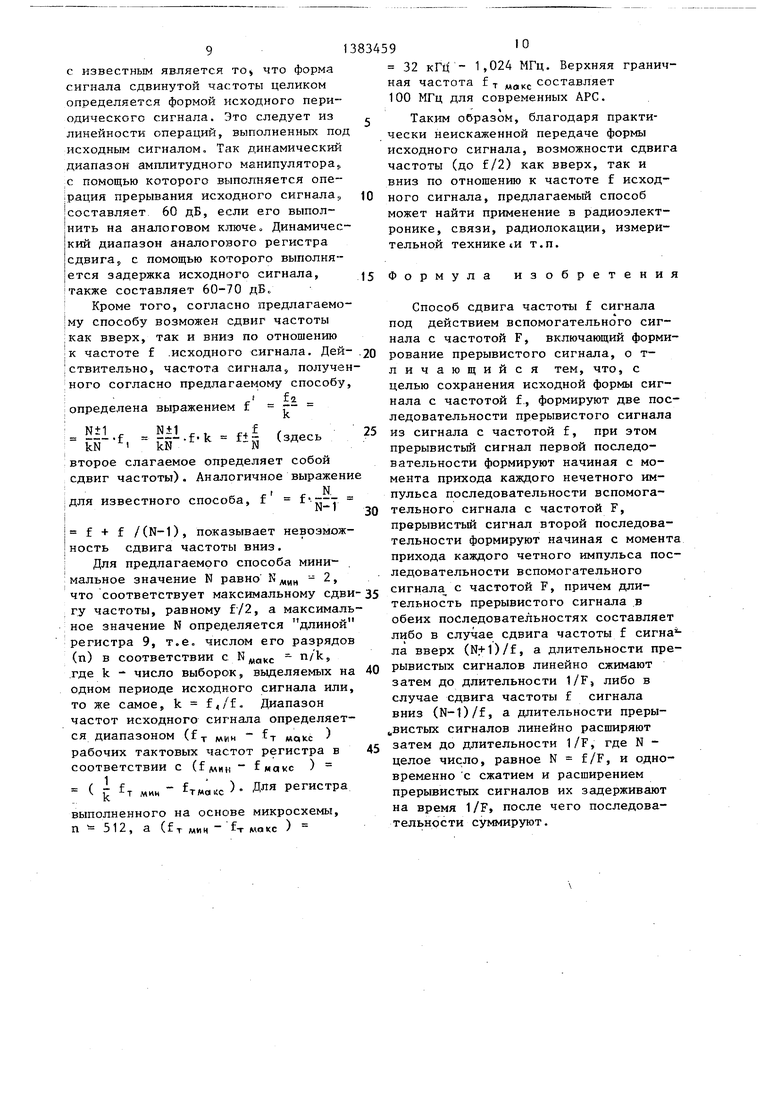

На фиг. 1 показаны временные ди- аграммы, поясняющие предлагаемый способ; на фиг. 2 - структурная электрическая схема устройства, ре- ,ализующего способ; на фиг. 3 - структурная электрическая схема блок управления (коммутатор находится в положении, соответствующем сдвигу частоты сигнала вниз; на фиг. 4 - отдельные блоки, входящие в состав устройства; на фиг. 3 и 6 - временны диаграммы, поясняющие работу устройства.

Из исходного сигнала (ИС) частоты f (фиг. 1) выделяют две последовательности периодически следующих его отрез ков (сигналы nci иПС2, фиг. 1). Длительности радиоимпульсов в прерьшис- тых сигналах ПС1 и ПС2 выбирают кратными целому числу периодов ИС под действием вспомогательного сигнала (ВС) (не показан) ., Если период следования ВС составляет N периодов ИС, то длительности ПС1 и ПС2 выбирают, например, равными (N-1)f, при сдвиге частоты ИС вниз (фиг. 1а), и (№-1)f, при сдвиге частоты вверх (фиг. 16). Сигналы ПС1 и ПС2 растягивают (фиг. 1а) или сжимают (фиг. 16) и одновременно задерживают во времени. В результате этого получают видоизмененные сигналы ПС1 и IIC2, имеющие скважность равную двум, при

суммировании которых получают искомы непрерывный сигнал ИС сдвинутой частоты f (K±1)f/N (знак + соответствует сдвигу вверх).

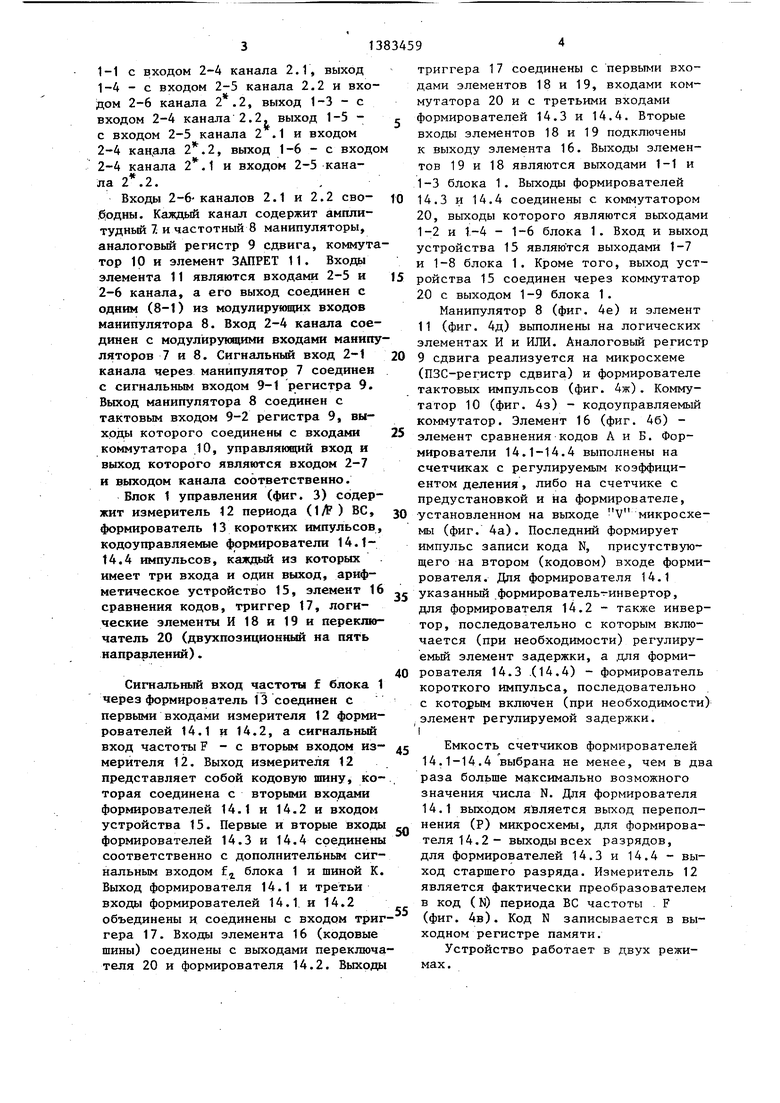

Способ реализуют с помощью устройства (фиг. 2), содержащего блок 1 управления, имеющий импульсные , 1-2 - 1-6 и кодовые 1-7 - 1-9 выходы и входы, являющиеся входными шинами частот f и F устройства, два идентич еых блока 2 и 2 преобразования, содержащих каждый по два канала 2.1 и 2.2 преобразования, каждый из которых имеет сигнальные 2-1 - 2-3, управлякяцие 2-4 и 2-5, запрещающий 2-6 и кодовьй 2-7 входы, сумматор 3, соединенньш своими входами с выходами каналов, а выходом - через фильтр

4с выходом устройства, и умножители

5и 6 частоты.

Умножитель 5 включен следующим образом. Его сигнальный вход соединен с щиной f устройства и вхбдами 2-1 блоков 2 и 2 , а выход - с сигнальным входом умножителя 6 и входами 2-2 блоков 2 и 2. Умножитель 6 имеет два управлякмцих входа, соединенных с выходами 1-7 и 1-8 блока 1, Выход умножителя 6 соединен с входом 2-3 блоков 2 и 2 преобразования и дополнительным входом f блока 1. Входы 2-7 обоих каналов блоков 2 и 2 объединены и подключены к выходам соответственно 1-9 и 1-7 блока 1.

Выходы блока 1 соединены с остальными входами каналов 2.1 и 2.2 в

U

блоке 2 и каналов 2 .1 и 2 .2 в

блоке 2 следующим образом. Выход 1-2 соединен с входами 2-5 канала

1

1-1 с входом 2-4 канала 2.1, выход 1-4 - с входом 2-5 канала 2,2 и входом 2-6 канала 2.2, выход 1-3 - с входом 2-4 канала 2.2. выход 1-5 - с входом 2-5 канала 2 .1 и входом 2-4 канала 2.2, выход 1-6 - с входом 2-4 канала 2.1 и входом 2-5 канала 2.2.,

Входы 2-6-каналов 2.1 и 2.2 свободны. Каждый канал содержит амплитудный 7. и частотный 8 манипуляторы, аналоговый регистр 9 сдвига, коммутатор 10 и элемент ЗАПРЕТ 11. Входы элемента 11 являются входами 2-5 и 2-6 канала, а его выход соединен с одним (8-1) из модулирующих входов манипулятора 8. Вход 2-4 канала соединен с модулирующими входами манипуляторов 7 и 8. Сигнальный вход 2-1 канала через манипулятор 7 соединен с сигнальным входом 9-1 регистра 9. Выход манипулятора 8 соединен с тактовым входом 9-2 регистра 9, выходы которого соединены с входами коммутатора 10, управляющий вход и выход которого являются входом 2-7 и выходом канала соответственно.

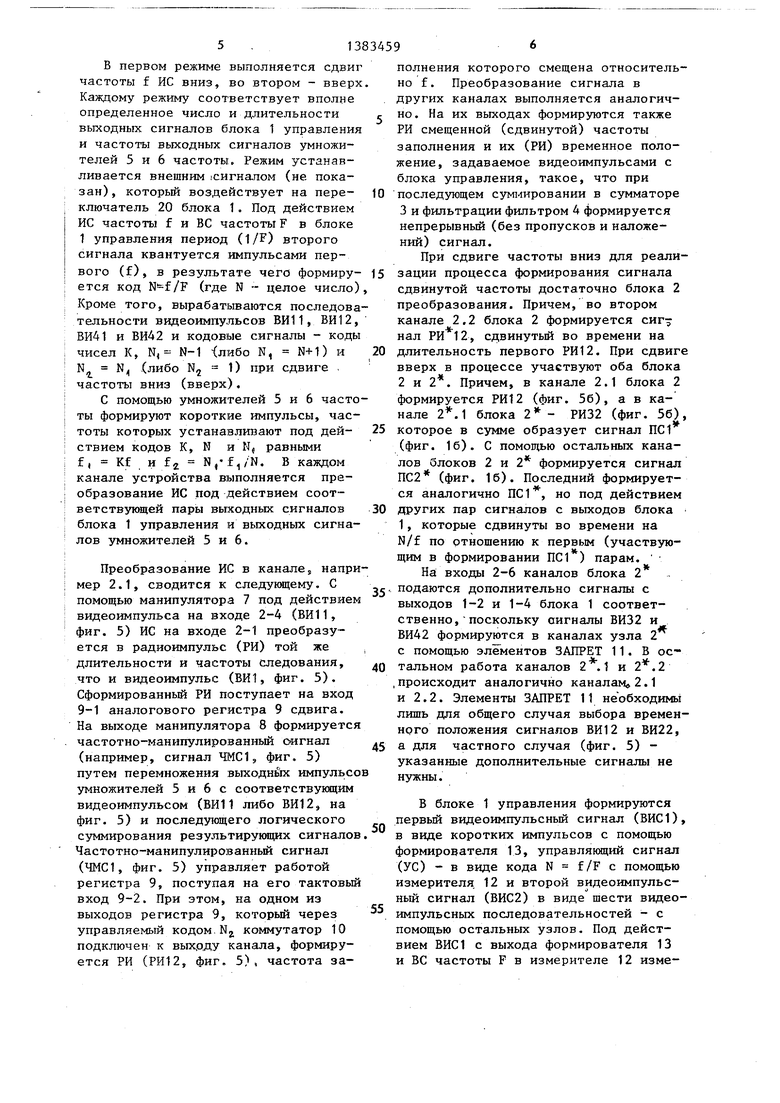

Блок 1 управления (фиг. 3) содержит измеритель 12 периода (1 / ) ВС, формирователь 13 коротких импульсов, кодоуправляемые формирователи 14.1- 14.4 импульсов, каждый из которых имеет три входа и один выход, арифметическое устройство 15, элемент 16 сравнения кодов, триггер 17, логические элементы И 18 и 19 и переключатель 20 (двухпозиционный на пять направлений)..

Сигнальный вход частоты f блока 1 через формирователь О соединен с первыми входами измерителя 12 формирователей 14.1 и 14.2, а сигнальный вход частоты F - с вторым входом измерителя 12. Выход измерителя 12 представляет собой кодовую шину, которая соединена с вторыми входами формирователей 14.1 и 14.2 и входом устройства 15. Первые и вторые входы формирователей 14.3 и 14.4 соединены соответственно с дополнительньм сигнальным входом f блока 1 и шиной К. Выход формирователя 14.1 и третьи входы формирователей 14.1, и 14.2 объединены и соединены с входом триг гера 17. Входы элемента 16 (кодовые шины) соединены с выходами переключателя 20 и формирователя 14.2. Выхода

0

5

0

5

0

5

0

5

триггера 17 соединены с первыми входами элементов 18 и 19, входами коммутатора 20 и с третьими входами формирователей 14.3 и 14.4. Вторые входы элементов 18 и 19 подключены к выходу элемента 16. Выходы элементов 19 и 18 являются выходами 1-1 и 1-3 блока 1. Выходы формирователей 14.3 и 14.4 соединены с коммутатором 20, выходы которого являются выходами 1-2 и 1.-4 - 1-6 блока 1. Вход и выход устройства 15 являются выходами 1-7 и 1-8 блока 1. Кроме того, выход устройства 15 соединен через коммутатор 20 с выходом 1-9 блока 1.

Манипулятор 8 (фиг. 4е) и элемент 11 (фиг. 4д) выполнены на логических элементах И и ИЛИ. Аналоговый регистр 9 сдвига реализуется на микросхеме (ПЗС-регистр сдвига) и формирователе тактовых импульсов (фиг. 4ж). Коммутатор 10 (фиг. 4з) - кодоуправляемый коммутатор. Элемент 16 (фиг. 4б) - элемент сравнения кодов А и Б. Формирователи 14.1-14.4 выполнены на счетчиках с регулируемым коэффициентом деления, либо на счетчике с предустановкой и на формирователе, установленном на выходе V микросхемы (фиг. 4а). Последний формирует импульс записи кода N, присутствующего на втором (кодовом) входе формирователя. Для формирователя 14.1 указанный формирователь-инвертор, для формирователя 14.2 - также инвертор, последовательно с которым включается (при необходимости) регулируемый элемент задержки, а ,цля формирователя 14.3 .(14.4) - формирователь короткого импульса, последовательно с которым включен (при необходимости)

элемент регулируемой задержки.

|

Емкость счетчиков формирователей 14.1-14.4 выбрана не менее, чем в два раза больше максимально возможного значения числа N. Для формирователя 14.1 выходом яЬляется выход переполнения (Р) микросхемы, для формирователя 14. 2- выходы всех разрядов, для формирователей 14.3 и 14.4 - выход старшего разряда. Измеритель 12 является фактически преобразователем в код (N) периода ВС частоты . F (фиг. 4в). Код N записывается в выходном регистре памяти.

Устройство работает в двух режимах.

В первом режиме выполняется сдвиг частоты f ИС вниз, во втором - вверх Каждому режиму соответствует вполне определенное число и длительности выходных сигналов блока 1 управления и частоты выходных сигналов умножителей 5 и 6 частоты. Режим устанавливается внешним 1сигнапом (не показан), которьй воздействует на пере- ключатель 20 блока 1. Под действием ИС частоты f и ВС частоты F в блоке 1 управления период (1/F) второго сигнала квантуется :импульсами первого (f), в результате чего формиру- ется код N-f/F (где N - целое число) Кроме того, вырабатываются последовательности видеоимпульсов ВИ11, ВИ12, ВИ41 и БИА2 и кодовые сигналы - коды чисел К, N, N-1 либо N, N+1) и

N .

частоты вниз (вверх),

С помощью умножителей 5 и 6 частоты формируют короткие импульсы, частоты которых устанавливают под дей- ствием кодов К, N и N, равными f, Kf и f2 N,-f,/N. В каждом канале устройства выполняется преобразование ИС под действием соответствующей пары вьгкодных сигналов блока 1 управления и выходных сигналов з ножителей 5 и 6.

, N .(либо N, 1) при сдвиге

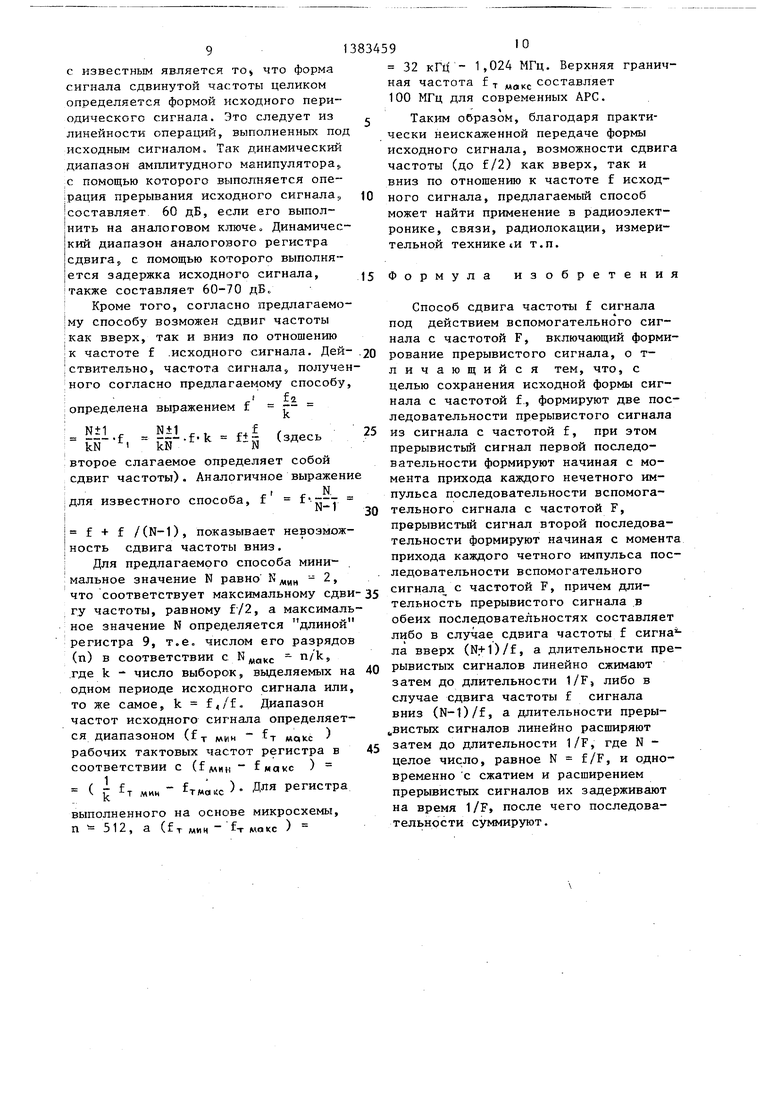

Преобразование ИС в канале;, например 2.1, сводится к следующему. С помощью манипулятора 7 под действием видеоимпульса на входе 2-4 (ВИ11, фиг. 5) ИС на входе 2-1 преобразуется в радиоимпульс (РИ) той же длительности и частоты следования, что и видеоимпульс (ВИ1, фиг. 5). Сформированный РИ поступает на вход 9-1 аналогового регистра 9 сдвига. На выходе манипулятора 8 формируется частотно-манипулированный сигнал (например, сигнал , фиг. 5) путем перемножения выходийх импульсо умножителей 5 и 6 с соответствукщ:им видеоимпульсом (ВИ1t либо ВИ12, на фиг. 5) и последующего логического суммирования результирующих сигналов Частотно-манипулированньй сигнал (ЧМС1, фиг. 5) управляет работой регистра 9, поступая на его тактовый вход 9-2. При этом, на одном из выходов регистра 9, который через управляемый кодом. Nj, коммутатор 10 подключен к вьгх,о,ду канала, формируется РИ (РИ12, фиг. 5), частота за

г 5 0

5 0

5

Q с

0

полнения которого смещена относительно f. Преобразование сигнала в других каналах выполняется аналогично. На их выходах формируются также РИ смещенной (сдвинутой) частоты заполнения и их (РИ) временное положение, задаваемое видеоимпульсами с блока управления, такое, что при последующем суммировании в сумматоре 3 и фильтрации фильтром 4 формируется непрерывный (без пропусков и наложений) сигнал.

При сдвиге частоты вниз для реализации процесса формирования сигнала сдвинутой частоты достаточно блока 2 преобразования. Причем, во втором канале 2,2 блока 2 формируется сиг нал РИ 12, сдвинутый во времени на длительность первого РИ12. При сдвиге вверх в процессе участвуют оба блока 2 и 2. Причем, в канале 2.1 блока 2 формируется РИ12 (фиг. 56), а в канале 2. блока РИ32 (фиг. 56), которое в сумме образует сигнал ПС1 (фиг. 16). С помощью остальных каналов блоков 2 и 2 формируется сигнал ПС2 (фиг. 16). Последний формируется аналогично ПС 1 , но под действием других пар сигналов с выходов блока 1, которые сдвинуты во времени на N/f по отношению к первым (участвующим в формировании ПС1) парам.

На входы 2-6 каналов блока 2 подаются дополнительно сигналы с выходов 1-2 и 1-4 блока 1 соответственно, поскольку сигналы ВИ32 и ВИ42 формируются в каналах узла 2 с помощью элементов ЗАПРЕТ 11. В остальном работа каналов 2 .1 и 2.2 ,происходит аналогично каналам 2.1 и 2.2. Элементы ЗАПРЕТ 11 необходимь лишь для общего случая выбора временного положения сигналов ВИ12 и ВИ22, а для частного случая (фиг. 5) - указанные дополнительные сигналы не .

В блоке 1 управления формируются первый видеоимпульсный сигнал (ВИС1), в виде коротких импульсов с помощью формирователя 13, управляняций сигнал (УС) - в виде кода N f/F с помощью измерителя. 12 и второй видеоимпульсный сигнал (ВИС2) в виде шести видеоимпульсных последовательностей - с помощью остальных узлов. Под действием ВИС1 с выхода формирователя 13 и ВС частоты F в измерителе 12 измеряется период 1/F ВС путем подсчета числа импульсов ВИС1 на одном периоде ВС. Работа остальных узлов блока 1 осуществляется под действием ВИС1 и кода N. На выходах 1-1 - 1-6 формируются соответственно сигналы ВИ11, ВИ12, ВИ21, ВИ22, ВИ31 и ВИ41 (сигналы ВИ32 и ВИ42 формируются в каналах блока 2 из сигналов ВИ31 и ВИ41). С помощью формирователя 14.1 и триггера 17 формируются два сигнала типа меандр (ВИ12 и ВИ22, фиг. 6а или-ТО же самое, ВИ41 и ВИ31, фиг. 6б), которые коммутируются с помощью переключателя 20 либо на выходы 1-2 и 1-4 (при сдвиге f вниз), либо на выходы 1-5 и 1-6 блока 1. Сигналы ВИ11 и ВИ21 формируются с помощью формирователя 14.2, элемента 16 и арифметического устройства 15.

В устройстве 15 число N преобразуется в число N, NT1 .(знак - при сдвиге f вниз). На один вход элемента 16 (вход А) поступает код N(Nj N, при сдвиге f вниз и N 1 при сдвиге f вверх) с выхода коммутатора 20. На второй вход элемента 16 (вход Б) поступает выходной код формирователя 14.2. Значение последнего изменяется во времени от О до N ( под действием импульсов ВИС1. В элементе 16 выполняется сравнение кодов входных чисел, при этом на его выходе (выход Б А микросхемы, фиг. 56) формируется ВИ, длительность которого равна N, периодам ВИС1 (т.е. ВИ длительностью N,/f либо 1/f), а частота следования - N/fi В элементах 18 и 19 выполняется перемножение выходных сигналов элемента 16 и триггера 17, в результате чего частота следования ВИ с выхода элемента 16 уменьшается вдвое, а на выходах элементов 18 и 19 (выходах 1-1 и 1-3 блока 1) формируются сигналы ВИ21 и ВИ11 (фиг. 6).

Сигналы ВИ12 и ВИ22 (фиг. 6б) в режиме Сдвиг f вверх формируются с помощью формирователей14.3 и 14.4 соответственно, которые работают в режиме вычитания. Каждый формирователь управляется сигналом с соответствующего выхода триггера и кодом К. По окончании сигнала с выхода триггера 1 7 в формирователь записьшается число k . Под действием импульсов, поступающих на счетный вход, число N уменьшается до О., При этом в момент установки счетчика формиро5

вателя в О формируется срез выходного счетчика сигнала счетчика. Сформированные таким образом ВИ12 и ВИ22 через переключатель 20 поступают (в режиме сдвига частоты вверх) на выходы 1-4 и 1-2 блока 1 соответственно.

Процесс сдвига частоты заполнения

0 РИ выполняется в регистре 9 в два такта.

В течение первого такта (интервал времени между первым и вторым импульсами сигнала ВС, фиг. 5) на входы 9-1 и 9-2 регистра 9 синхронно поступают РИ1 и ЧМС1 (фиг. 5а). При этом, под действием каждого импульса ЧМС1 в первьй разряд регистра 9 записывается в виде зарядового пакета мгно0 венное значение РИ1, соответствующее этому импульсу, а ранее записанные мгновенные значения смещаются на один разряд в направлении к концу АРС. Таким образом, к приходу последнего

5 импульса ЧМС1, действующего в 1-м

такте в разрядах АРС, оказывается записанным весь РИ1, точнее предоставляется в виде дискретной копии, т.е. отдельными значениями, соответствующими моментам действия импульсов ЧМС1. Кроме того, РИ1 оказывается записанным в первые п - k(N-1) разрядов регистра (здесь k f,/f).

В течение второго такта (фиг. 5, интервал времени между вторым и третьим импульсами сигнала ВС) импульсы ЧМС1 вновь, поступая на регистр 9, вызывают продвижение всех выборок (записанных в первом такте) к концу, т.е. с приходом каждого импульса на тактовом входе выборки РИ1 смещаются на один разряд в сторону конца ре- гистра 9. С помощью коммутатора 10 на выход канала включается п -и разряд либо, что то же самое, выход регистра 9. На этом выходе в течение второго такта поочередно возникают выборки (мгновенные значения) РИ1, начиная с 1-й и кончая последней, в результате чего формируется РИ (РИ12, фиг. 5а). Последний имеет большую (при сдвиге частоты вниз) длительность, равную продолжительности второго такта, вследствие различия частот f, и f (f при

5 сдвиге частоты вниз), что равносильно сдвигу частоты.

Одним из основных преимуществ предлагаемого способа по сравнению

0

5

0

5

0

с известным является то что форма сигнала сдвинутой частоты целиком определяется формой исходного периодического сигнала. Это следует из линейности операций, выполненных под исходным сигналом. Так динамический диапазон амплитудного манипулятора., с помощью которого выполняется опе- :рация прерывания исходного сигнала,, Iсоставляет 60 дБ, если его выпол- |нить на аналоговом ключе Динамичес- |кий диапазон аналогового регистра сдвига 5 с помощью которого выполня- |ется задержка исходного сигнала, I также составляет 60-70 дБ. Кроме того, согласно предлагаемо- 1му способу возможен сдвиг частоты ;как вверх, так и вниз по отношению :К частоте f .исходного сигнала. Дей- :ствительно, частота сигнала, полученного согласно предлагаемому способу,

-

k

определена выражением f

Nil N±1 , ,,. ., kN--f -N « второе слагаемое определяет собой сдвиг частоты). Аналогичное выражение

;для известного способа,

f- f.-N N-1

1 f + f /(N-1), показывает невоэмож ность сдвига частоты вниз.

Для предлагаемого способа минимальное значение N равно К д,,, - 2, что соответствует максимальному сдви гу частоты, равному f/2, а максимальное значение N определяется длиной регистра 9, т.е. числом его разрядов (п) в соответствии с n/k, где k - число выборок, выделяемых на одном периоде исходного сигнала или, то же самое, k f,/fa Диапазон частот исходного сигнала определяется диапазоном (f т макс рабочих тактовых частот регистра в соответствии с (f/wmi - fnavc )

( J ft миц - frwa.c ) регистра

выполненного на основе микросхемы, п - 512, а (f т мич f-T макс )

. 383459 О

32 кП - 1,024 МГц. Верхняя гранич

5

ная частота f (дд,. составляет 100 МГц для современных АРС.

5 Таким образом, благодаря практически неискаженной передаче формы исходного сигнала, возможности сдвига частоты (до f/2) как вверх, так и вниз по отношению к частоте f исход0 ного сигнала, предлагаемьш способ может найти применение в радиоэлектронике, связи, радиолокации, измерительной технике и т.п.

5 Формула изобретения

Способ сдвига частоты f сигнала под действием вспомогательного сигнала с частотой F, включающий форми- 0 рование прерывистого сигнала, о т- личающийся тем, что, с целью сохранения исходной формы сигнала с частотой f., формируют две последовательности прерывистого сигнала 5 из сигнала с частотой f, при этом прерывистый сигнал первой последовательности формируют начиная с момента прихода каждого нечетного импульса последовательности вспомога- 0 тельного сигнала с частотой F,

прврывистьй сигнал второй последовательности формируют начиная с момента прихода каждого четного импульса пос- . ледовательности вспомогательного сигнала с частотой F, причем длительность прерывистого сигнала .в обеих последовательностях составляет либо в случае сдвига частоты f сигна ла вверх (N+1)/f, а длительности прео рывистых сигналов линейно сжимают затем до длительности 1/F, либо в случае сдвига частоты f сигнала вниз (N-1)/f, а длительности преры- вистых сигналов линейно расширяют 5 затем до длительности 1/F, где N - целое ЧИС.ЛО, равное N f/F, и одновременно с сжатием и расширением прерывистых сигналов их задерживают на время 1/F, после чего последовательности суммируют.

1-7 1-8

tmpeseK 2

1-9 f 3

9UZ.S

а

./г

л

2-5 2-5

-вЖ

«/8. 4

А.

Фиг. 5

| СПОСОБ ФОРМИРОВАНИЯ ОДНОПОЛОСНОГО СИГНАЛА ДЛЯ ФАЗОВЫХ ИЗМЕРЕНИЙ В ДИАПАЗОНЕ ИНФРАНИЗКИХ | 0 |

|

SU259266A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Формирователь сигналов с однополосной модуляцией | 1975 |

|

SU534860A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-23—Публикация

1987-07-09—Подача