1

Изобретение относится к вычислительной технике и может применяться для обработки данных, хранящихся в оперативной намяти, но программе, запоминаемой также в оперативной памяти.

Известны процессоры, которые содержат арифметическо-логическое устройство, устройство управления и внутренние регистры. Однако в таких процессорах представление ирограммы в машинных командах не соответствует представлению этой программы на алгоритмическом языке. Последовательность Онераций в машинных командах не совпадает с последовательностью операций во входном языке.

Это объясняется тем, что, с одной стороны, любое ариф.метическое выражение должно вычисляться с учетом приоритетов арифметических действий, а, с другой - тем, что команды программ в перечисленных выше машинах исполняются последовательно по мере того, как они записаны в теле программы. Поэтому последовательность команд для арифметического выражения составляется так, как это выражение должно вычисляться, а не так, как оно записано иа входном алгоритмическом языке.

Другая проблема, которая стоит перед современной вычислительной техникой, связана с трансляцией. Широко известны способы

программного контроля синтаксической правильности программ, записанных иа языке высокого уровня, и их преобразования в последовательность машинных команд, которые

способны воспринимать ЭВМ. Указанные функции контроля и преобразования являются основными нри ностроенин транслнруюш,их программ. Эти программы занимают большие объемы памяти, а при их работе требуется много машинного времени. Кроме того, программы, написанные на языке высокого уровня, после их трансляции в машинные программы становятся слишком громоздкими, совершенно ненохожнми иа их представление иа входном языке и, следовательно, необозрнмы для пользователя.

Все это приводит к тому, что отладка иа машине этих нрограмм вызывает серьезные затруднения, а основным методом отладки

является метод нроб и ошибок. Для повышеиня эффективиости отладки программ необходимо, чтобы рабочие нрограммы в намяти машины но форме прямо соответствовали исходным программам, написанным иа языКС высокого уровня.

Известен процессор, обеспечивающий функцию языков программирования высокого уроЕ5ня. Этот процессор содержит буферные устройства, ассоциативную память, арнфметическо-логическое устройство, устройство

управления. В нем осзществляется динамическая подготовка структур данных, начинающихся с любого разряда памяти н имеющих произвольную длииу; команды выиолияются ие в порядке их следования, а в соответстВИИ с присвоенными приоритетами.

Однако нельзя присвонть приоритеты всем элементам языков программирования. Например, приоритет знака «+, стоящего перед « (, должен быть ниже приоритета (, а приоритет знака «+, стоящего после « ( , должен быть выще приоритета « ( .

Эти трудности преодолевают либо при помощи спецнальных схем, либо при помощи анализирующей микропрограммы, что усложняет аппаратуру и замедляет работу вычислительного устройства.

Кроме того, в указанном процессоре аппаратно реализован только один стек. Это приводит к тому, что в одном стеке приходится хранить команды, операнды в различных форматах, а также адреса нереходов и операндов, что существенно затрудняет организацию стека и усложняет алгоритмы работы с ним, или приводит к необходимости организации в памяти дополнительных стеков, работа с которыми осуществляется с помощью программ или микропрограмм, что замедляет работу процессора.

Например, рассмотрИ1 1 оператор обращения к процедуре Абсмакс (А, N, М, Yy, I, К). Идентификатор Абсмакс указывает адрес процедуры. Фактические неременные А, N, М, Yy, I, К в общем случае могут быть выражениями, идентификаторами массивов, идентификаторами переключателей и идентификаторами процедур. При их вычислении в стеке должны оставаться либо вычисленные значения фактических параметров (в случае передачи их в процедуру по зиачению), либо вычисленные адреса (в случае передачи их по наименованию). После вычисления всех фактических параметров управление должно быть передано по адресу, соответствующему идентификатору Абсмакс. Если хранить адрее процедуры в том же стеке, где хранятся вычисленные фактические параметры, то возникает трудность его нахождения, так как количество фактических параметров в процедуре может быть различным.

Из известных нроцессоров наиболее близким по технической сущности к изобретению является процессор, содержащий устройство управления, соединенное двустороппими связями с блоком регистров и арифметическо-логическим устройством, первые информационные входы которых нодключены к информационному входу процессора, адресные и первые информационные выходы - соответственно к адресному и информационному выходам процессора, вторые информационные вход и выход арифметическо-логического устройства соединены соответственно с вторым информационным выходом и вторым информационным входом блока регистров.

Кро.ме того, ироцессор включает стековую память для вре.менного запоминания данных и команд, устройство определения относительного приоритета между двумя соседними командами програм.мы и дополнительное устройство управления скобка.ми.

Однако в этом процессоре усложнен алгоритм работы со стеком, что существенно понижает быстродействие, устройство определения относительного приоритета команд не является универсальным, так как невозможно присвоить приоритеты всем элементам языка программирования. Из-за этого, в частности, процессор не имеет возможности аппаратно реализовать многие операторы алгоритмического языка (например, операторы процедур). Кроме того, не предусмотрено устройство для синтаксического контроля исходных программ.

Цель изобретения - новышение быстродействия и улучщение эксплуатационных характеристик при отладке и синтаксическом контроле программ.

Это достигается тем, что в предлагаемый процессор введены блок анализа приоритетных отнощений, блок синтаксического контроля и перекодировки, стек команд и стек данных, соединенные двусторонними связями с устройством управления, первые и вторые входы стеков команд и данных подключены соответственно к информационному входу процессора и второму информационному выходу арифметическо-логического устройства, адресный, цервые и вторые выходы - соответственно к адресному, информационному выходу процессора и к второму информационному входу ариф.метическо-логического устройства, входы блока анализа нриоритетных отнощений соединены с соответствующими выходами блока регистров н стека команд.

Наличие аппаратных стеков данных и команд позволяет упростить алгоритмы работы со стеками и тем самым повысить быстродействие.

Наличие блока анализа приоритетных отнощений позволяет аппаратно онределять нриоритетные отношения между всеми элементами языка программирования и тем самым сэкономить оборудование (например, исключить устройство управления скобками) и в совокупности со стеками добиться прямого соответствия между исходными программами на алгоритмическом языке и программами в мащинных командах, что непосредственно приводит к повыщению эффективности отладки программ.

Включение в состав процессора блока синтаксического контроля и перекодировки и использоваиие при его построении формальных методов синтаксического контроля позволяет существенно ускорить синтаксический контроль и совместить его с вводом программы.

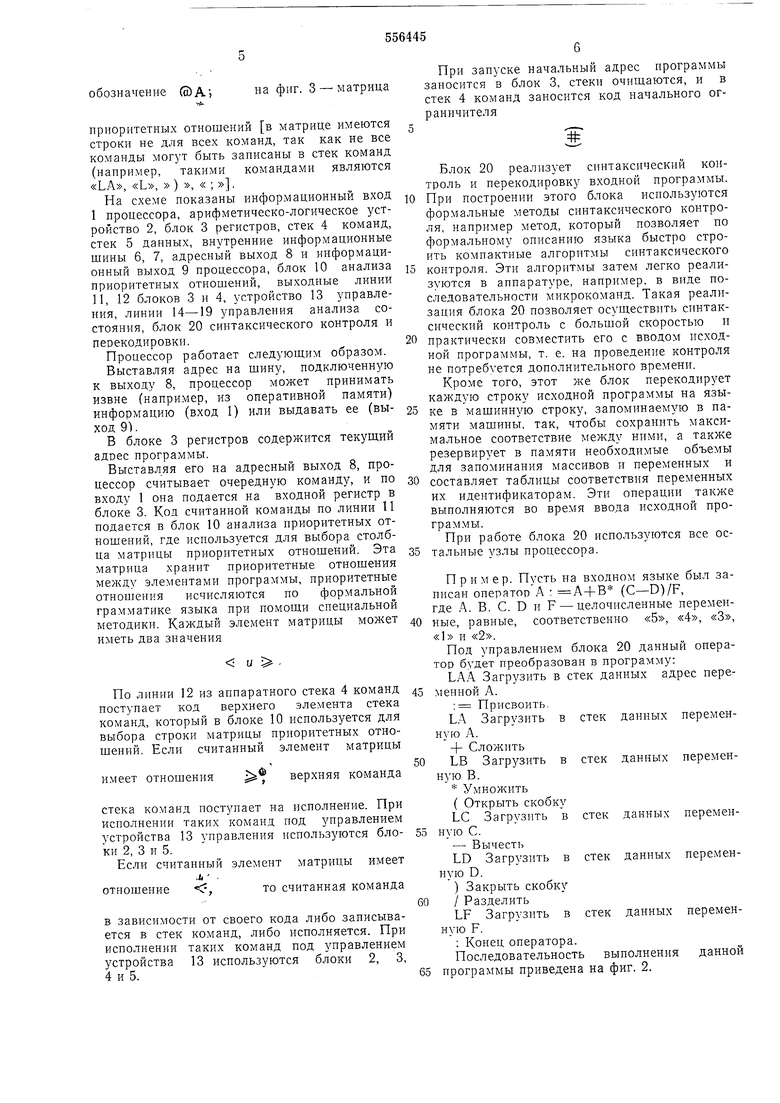

На фиг. 1 показана схема предлагаемого процессора; на фиг. 2 - пример выполнения программы, где адрес переменной А имеет

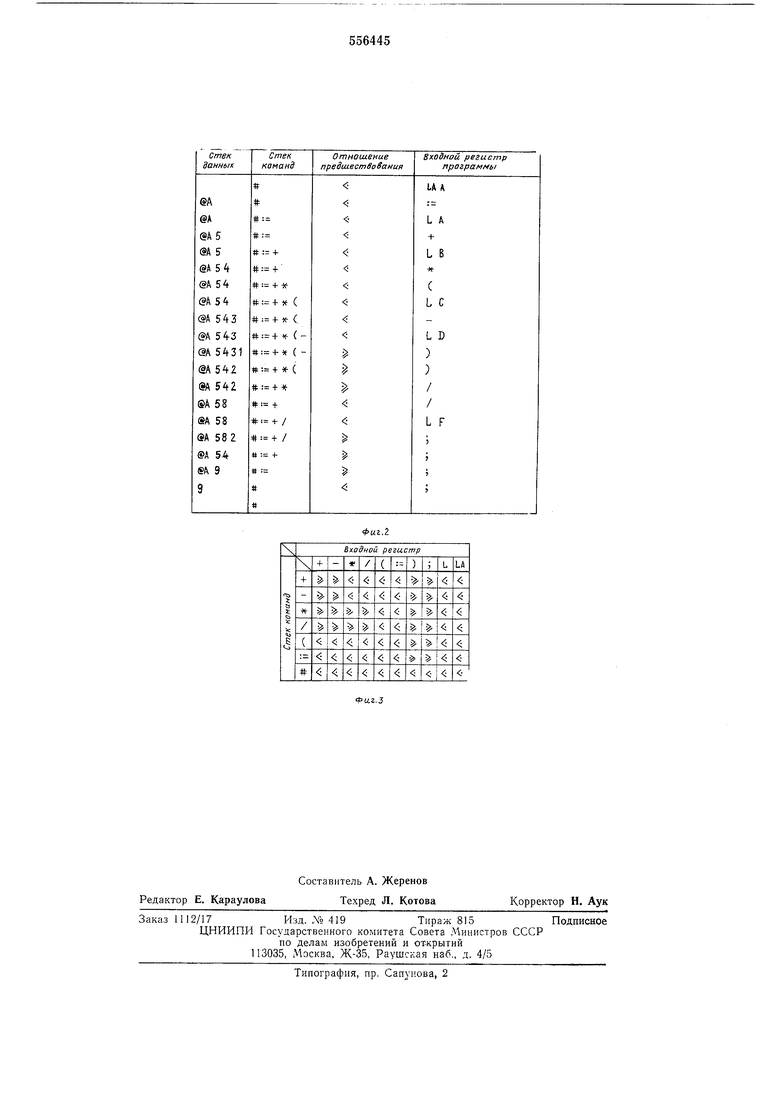

на фиг. 3 - матрица

обозначение (5)А ,

приоритетных отношений в матрице имеются строки не для всех команд, так как не все команды могут быть занисаны в стек команд (наиример, такими командами являются «LA, «L, ) , « ; .

На схеме показаны информационный вход 1 процессора, арифметическо-логическое устройство 2, блок 3 регистров, стек 4 команд, стек 5 данных, внутренние информационные шины 6, 7, адресный выход 8 и информационный выход 9 процессора, блок 10 анализа приоритетных отношений, выходные линии 11, 12 блоков 3 и 4, устройство 13 управления, линии 14-19 управления анализа состояния, блок 20 синтаксического контроля и перекодировки.

Процессор работает следующим образом.

Выставляя адрес на шину, подключенную к выходу 8, процессор может принимать извне (например, из оперативной памяти) информацию (вход 1) или выдавать ее (выход 9).

В блоке 3 регистров содержится текущий адрес программы.

Выставляя его на адресный выход 8, процессор считывает очередную команду, и по входу 1 она подается на входной регистр в блоке 3. Код считанной команды по линии 11 подается в блок 10 анализа приоритетных отношений, где используется для выбора столбца матрицы приоритетных отнощений. Эта матрица хранит приоритетные отношения между элементами программы, приоритетные отношения исчисляются по формальной грамматике языка при помощи специальной методики. Каждый элемент матрицы может иметь два значения

U .

По линии 12 из аннаратного стека 4 команд поступает код верхнего элемента стека команд, который в блоке 10 используется для выбора строки матрицы приоритетных отношений. Если считанный элемент матрицы

и.меет отношения верхняя команда

стека команд поступает на исполнение. При исполнении таких команд иод унравлением устройства 13 управления используются блоки 2, 3 и 5.

Если считанный элемент матрицы имеет

м отношение ,то считанная команда

в зависимости от своего кода либо записывается в стек команд, либо иснолняется. При исполнении таких команд нод управлением устройства 13 используются блоки 2, 3, 4 и 5.

При запуске начальный адрес программы заносится в блок 3, стеки очищаются, и в стек 4 команд заносится код начального ограничителя

,-.

Блок 20 реализует синтаксический контроль и перекодировку входной программы.

При построении этого блока используются формальные методы синтаксического контроля, например метод, который позволяет но формальному описанию языка быстро строить компактные алгорнтмы синтаксического

контроля. Эти алгоритмы затем легко реализуются в аппаратуре, например, в виде последовательности микрокоманд. Такая реализация блока 20 нозволяет осуществить синтаксический контроль с большой скоростью и

практически совместить его с вводом исходной программы, т. е. на проведение контроля не потребуется дополнительного времени.

Кроме того, этот же блок перекодирует каждую строку исходной программы на языке в машинную строку, запомннаемую в памяти машины, так, чтобы сохранить максимальное соответствие между ними, а также резервирует в памяти необходимые объемы для запоминания массивов и переменных и

составляет таблицы соответствия переменных их идентификаторам. Эти операции также выполняются во время ввода исходной программы. При работе блока 20 используются все остальные узлы процессора.

Пример. Пусть на входном языке был записан операторА : А+В (С-D)/F, где А. В. С. D и F - целочнсленные переменные, равные, соответственно «5, «4, «3, «1 и «2.

Под управлением блока 20 данный оператор будет преобразован в программу:

LAA Загрузить в стек данных адрес неременной А.

: Присвоить.

L.4 Загрузить в стек данных переменную А.

+ Сложить

LB Загрузить в стек данных переменную В.

Умножить ( Открыть скобку

LC Загрузить в стек данных переменную С.

- Вычесть

LD Загрузить в стек данных переменную D.

) Закрыть скобку / Разделить

LF Загрузить в стек данных переменную Р.

: Конец оператора.

Последовательность выполнения данной программы приведена на фиг. 2.

Таким образом, в процессоре представление программы в машинных командах прямо соответствуют представлению программы на алгоритмическом языке.

Процессор имеет следующие преимущества.

При сохранении такого же быстродействия исполнения программ, как и в существующих машинах, сокращается время, необходимое на перевод программ с алгоритмического языка в команды машины, а также на компоновку рабочей программы с библиотечными подпоограммами. В результате сокращается и общее время прохождения программы (т. е. от начала ввода до получения результатов).

Отпадает необходимость хранения программ в объективной форме, так как перевод программ из символьий формы в команды машины и компоновку рабочей программы можно совместить с работой устройств ввода - вывода.

Представляется возможность проведения отладки программ непосредственно на алгоритмическом языке.

Обеспечивается доступность электронных вычислительных машин (ЭВМ) на уровне интерпретирующих систем с алгоритмических языков, но с быстродействием, свойственным программам, оттранслированным в команды машины.

Перечисленные преимущества позволят повысить эффективность использования ЭВМ, сделать их более ДОСТУПНЫМИ для щирокого круга пользователей. Для написания эффективных программ от программиста не потребуется знания спецпальных машинных языков, достаточно знания стандартного алгоритмического языка. Более того, ЭВМ может быть использована как учебпое пособие при обучении этому языку, особенно при реализа8

ции режима «прокрутки, т. е. при синхронной ра-спечатке исполняемой программы на алгоритмическом языке и результатов ее работы.

Формула изобретения

Процессор, структурно ориентированный на алгоритмический язык, содержащий устройство уиравлеиия, соедииепиое двусторопними связями с блоком регистров и арифметичecкo-лoгичecк rм устройством, первые информационные входы которых подключены к информационному входу процессора, адресные и первые инфор.мационные выходы - соответственио к адресному ц информационному выходам ироцессора, вторые информационные вход и выход арифметическо-логического устройства соедииены соответствеино с вторым информационным выходом и вторым информапионньтм входом блока регистров, отличающийся тем, что, с целью повыщения быстродействия и улучшеипя эксплуатационных характеристик при отладке и синтаксическом контроле программ, в него введены

блок анализа приоритетных отношений, блок синтаксического контроля и перекодировки, стек команд и стек данных, соединенные двухсторонними связями с устройством управления, первые и вторые входы стеков

ко.манд и даиных иодключены соответственно к информационному входу процессора и втоpOiMy ииформациоииому выходу арифметическо-логического устройства, адресный, первые и вторые выходы - соответственно к адресному, ииформационному выходу ироцессора и к второму информационному входу арифметическо-логического устройства, входы блока зиализа приоритетных отношений соединены с соответствующими выходами блока регистров и стека команд.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С КОМАНДОПОДОБНЫМИ ЛОГИЧЕСКИМИ УПРАВЛЯЮЩИМИ ЭЛЕМЕНТАМИ | 1997 |

|

RU2143726C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Устройство управления цифровой вычислительной машины | 1971 |

|

SU437074A1 |

| Процессор мультиобработки данных | 1975 |

|

SU590745A1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С РАСШИРЕННЫМ СЛОВОМ СОСТОЯНИЯ | 1999 |

|

RU2149444C1 |

| Устройство для синтаксического анализа программ | 1980 |

|

SU918950A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

Авторы

Даты

1977-04-30—Публикация

1975-11-14—Подача