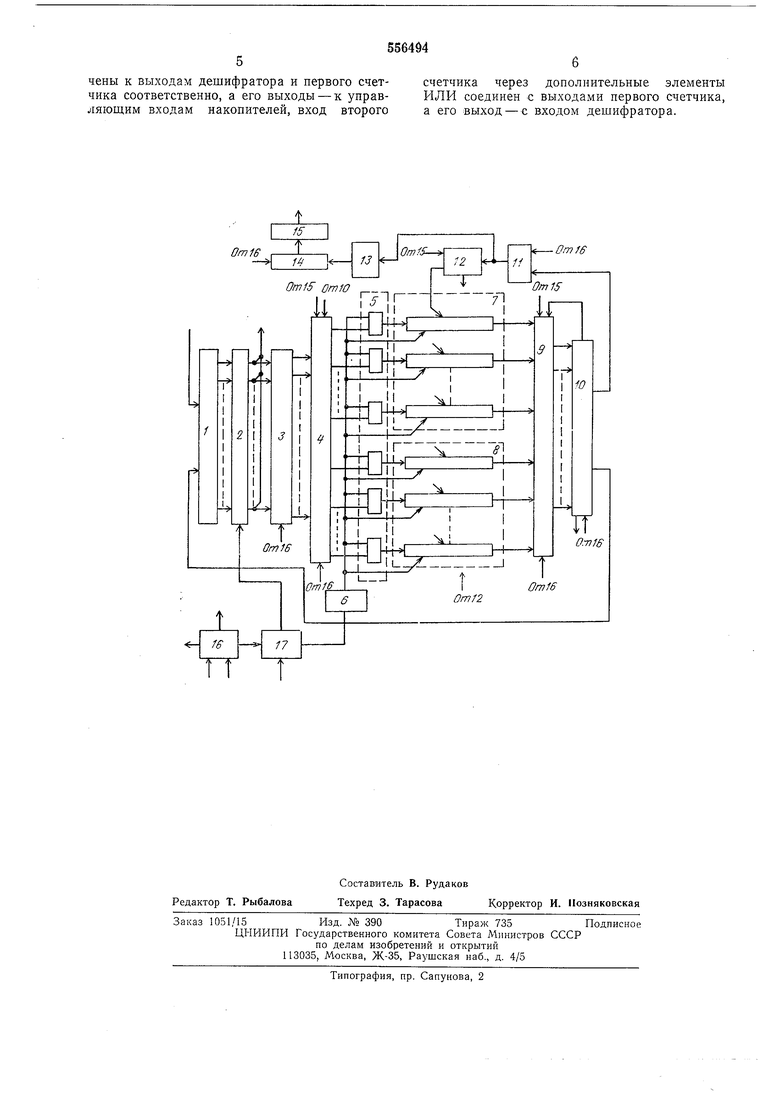

Устройство содержит элементы ИЛИ 1, выходы которых подключены к ииформациоНным входам регистра 2 слова, а выходы пос-теднего к информационным входам блока коди;равания 3, первый коммутатор 4, элементы И 5, генератор синхроимпульсов 6, основной накопитель 7, содержащий т регистров сдвига, дополаительный накопитель 8, содержащий п-т регистров сдвига, где - т.

Устройство также содержит второй коммутатор 9, блок декодирования 10, первый счетчик 11, служащий для подсчета количества отказов, блок 12 ле1реключе1Ния питания, дополнительные элементы ИЛИ 13, второй счетчик 14, служащий для подсчета номеров заменяющих регистров сдвига, дещифратор 15, блок управления 16 и адресный блок 17.

Входы первого коммутатора 4 подключены соответственно к выходам блока кодирования 3, блока управления 16, блока декодирования 10 и дещифратара 15, а его выходы к одним входам элементов И 5, другие входы которых соединены с выходом генератора синхроимпульсов 6. Входы второго коммутатора 9 подключены соответственно к выходам накопителей 7 и 8, блока управления 16, блока декодирования 10 и дешифратора 15, а его выходы - к входам блока декодирования 10, выходы которого соединены с входами первого счетчика 11. Входы блока 12 переключения питания подключены к выходам дешифратора 15 и первого счетчика И соответственно, а его выходы к управляющи.м входам накопителей 7 и 8. Вход второго счетчика 14 через дополнительные элеме-нты ИЛИ 13 соединен с выходами первого счетчика 11, а его выход - с входом дешифратора 16.

Устройство работает следующим образом.

Информационное слово через элементы ИЛИ 1 поступает на регистр 2 слова, а с его выходов - в блок кодирования 3, где в соответствии с информационными разрядами формируются контрольные разряды. С выходов блока кодирования слово подается на входы первого коммутатора 4. С его выходов через элементы И 5 слово поступает на регистры основного накопителя 7 и дополнительного накопителя 8. По другим входам элементов И 5 подаются синхроимпульсы с генератора синхроимпульсов 6, и все разряды слова поступают синхронно в регистры накопителей 7 и 8. Импульсы, поступающие с выхода генератора синхроимпульсов 6 на сдвигающие цепи регистров, обеспечивают синфазный сдвиг информации. Каждый сдвиговый регистр соответствует одному разряду слова, т. е. происходят параллельная запись, сдвиг и считывание слов. С выходов регистров сдвига слово поступает на входы второго коммутатоpa 9.

С выходов коммутатора 9 слово поступает на блок декодирования 10, который выдает сигналы об отсутствии или наличии ошибки. С выходов блока декодирования 10 откорректированное слово подается на входы элементов ИЛИ 1. Сигналы о наличии ошибки поступают также на входы первого счетчика И, где фиксируется количество ошибок каждого регистра основного накопителя 7. По достижении определенного, наперед заданного кода, последний выдает сигнал на блок переключения питания 12 для отключения питания соответствующего регистра (сигнал отключения питания), а сигнал, поступающий в блок 12 из блока 15, управляет включением питания на соответствующий дополнительный регистр.

Сигналы с выходов счетчика 11 поступают также через элементы ИЛИ 13 на счетчик 14. При отказе одного регистра основного накопителя 7 его информация пересылается в первый регистр дополнительного накопителя 8, при отказе другого регистра основного накопителя 7, его информация пересылается во второй регистр дополнительного накопителя 8 и т. д.

Дешифратор 15 дешифрирует состояние второго счетчика и выдает управляющие сигналы на коммутаторы 4 и 9. Последние подключают блок кодирования 3 и блок декодирования 10 к исправно работающим регистрам сдвига.

В зависимости от поступивших синхроимпульсов с генератора синхроимпульсов 6 и кода адреса на входы адресного блока 17 последний выдает управляющие сигналы на регистр 2 слова. Под действием этих сигналов слово с выходов регистра слова поступает также и на выходные информационные шины запоминающего блока.

Формула изобретения

Запоминающее устройство, содержащее адресный блок, вход которого подключен к выходу генератора синхроимпульсов, а выход - к входу регистра слова, подключенному к блоку кодирования, блок декодирования, соединенный через элементы ИЛИ с регистром слова, основной и дополнительный накопители, информационные входы которых подключены к выходам элементов И, блок управления и дешифратор, отличающееся тем, что, с -целью повышения надежности устройства, оно содержит коммутаторы, счетчики, блок переключения питания и дополнительные элементы ИЛИ, входы первого коммутатора подключены соответственно к выходам блока кодирования, блока управления, блока декодирования и дешифратора, а его выходы - к одним входам элементов И, другие входы которых соединены с выходом генератора синхроимпульсов, входы второго коммутатора подключены соответственно к выходам накопителей, блока управления, блока декодирования и дешифратора, а его выходы - к входам блока декодирования, выходы которого соединены с входами первого счетчика, входы блока переключения питания подключены к выходам дешифратора и первого счетчика соответственно, а его выходы - к управляющим входам накопителей, вход второго

счетчика через дополиительиые элементы ИЛИ соединен с выходами первого счетчика, а его выход -с входом дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1975 |

|

SU546933A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Устройство кодирования и декодирования информации | 1990 |

|

SU1783628A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Постоянное запоминающее устройство с самоконтролем | 1985 |

|

SU1285538A1 |

Omie

Авторы

Даты

1977-04-30—Публикация

1975-04-03—Подача