во при отсутствии ошибки поступает через коммутатор 14 на выход 16. При наличии ошибки блок 8 вырабатывает сигнал, по которому в регистре 13 сохраняется считанное слово, а в регистре 12 - адрес блока накопителя 2 (старшие разряды адреса). Одновременно по сигналам с выхода генератора 6 счетчик 4 начинает последовательно изменять свое состояние, обеспечивая обращение ко всем бло1

Изобретение относится к цифровой ычислительной технике, в частности запоминающим устройствам.

Цель изобретения - повышение надежности устройства.с

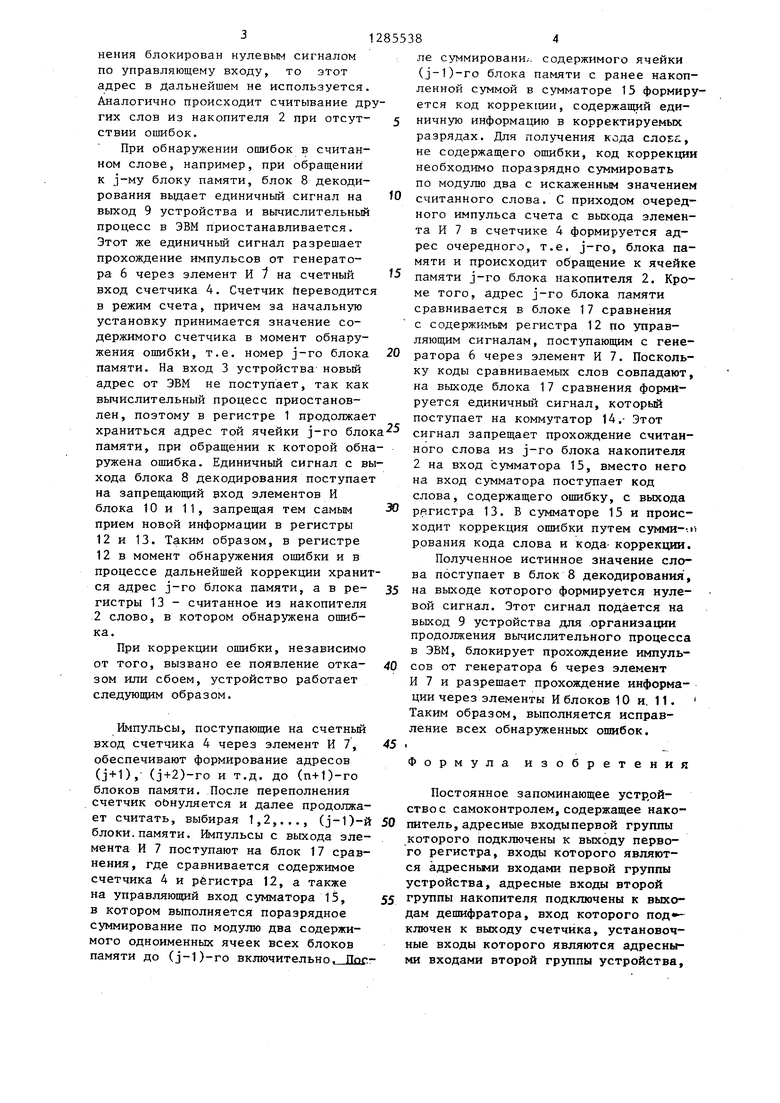

На чертеже представлена структурная схема запоминающего устройства с самоконтролем.

Устройство содержит регистр 1 адреса, накопитель 2, разделенный на JQ (п+1) блоков памяти, п из которых предназначено для хранения рабочей информации совместно с контрольными разрядами, необходимыми для обнаружения ошибки, а (п+1)-и блок памяти j5 предназначен для хранения информации, представляющей собой поразрядную сумму по модулю два слов, хранящихся по совпадающим адресам в различных блоках памяти. Устройство также 20 содержит адресный вход 3, счетчик 4, используемый при отсутствии ошибок в качестве регистра старших разрядов адреса, определяющих номер конкретного блока памяти в накопителе 2 с 25 помощью дешифратора 5, генератор 6 импульсов, элемент И 7, блок .8 декодирования, выход 9, блоки 10 и 11 элементов И, регистры 12 и 13, коммутатор 14, сумматор 15 по модулю ЗО два, выход 16 и блок 17 сравнения.

Устройство работает следующим образ ом.

На вход 3 устройства от ЭВМ поступает адрес выбираемого слова, при- 35 чем старшие разряды адреса подд1ются на входы счетчика А, который при отсутствии ошибок работает как регистр старших разрядов адреса. С помощью

85538

кам накопителя 2 по адресу, хранящемуся в регистре 1. Считываемая информация суммируется в сумматоре.

(Считывание происходит до тех пор, пока состояние счетчика 4 не сравняется с кодом, хранящимся в регистре

12, о чем свидетельствует сигнал на выходе блока 17. При этом слово из регистра 13 поступает в сумматор 15 и осуществляется коррекция ошибки. ,1 ил.

дешифратора 5 выбирается конкретный блок памяти в накопителе 2, Младшие :разряды адреса поступают в регистр 1 и определяют выбор конкретной ячейки внутри блока памяти. Считанное слово с информационных: выходов накопителя 2 поступает на коммутатор 14 и блок 11 элементов И.

Нулевой сигнал с вькода блока 8 декодирования блокирует прохождение импульсов через элемент И 7 на счетный вход счетчика 4, на сумматор 15 и на управляющий вход блока 17 сравнения. Этот же сигнал разрешает прохождение считываемого слова через элементы И блока 11 на регистр 13. Однако через коммутатор 14 информация с выхода регистра 13 на сумматор 15 не проходит, так как на управляющий вход коммутатора 14 с выхода блока 17 сравнения поступает нулевой сигнал. Формирование этого сигнала обеспечивается отсутствием управляющих сигналов на входе блока 17 с выхода элемента И 7, закрытого ну- левьм сигналом с выхода блока 8 декодирования. Через коммутатор 14 на вход сумматора 15 поступает считанное из накопителя 2 слово, которое просто передается на выход 16 устройства и на блок 8 декодирования. При отсутствии ошибок в считанном слове единичный сигнал прерывания на выходе 9 отсутствует. Нулевой сигнал с выхода блока 8 декодирования, кроме того, обеспечивает прохождение адреса блока памяти с выхода счетчика 4 через элементы И блока 10 на регистр 12, но так как блок 17 срав31285538

нения блокирован нулевым сигналом по управляющему входу, то этот адрес в Дальнейшем не используется. Аналогично происходит считывание других слов из накопителя 2 при отсут- 5 ствии ошибок.

При обнаружении ошибок в считанном слове, например, при обращении к j-му блоку памяти, блок 8 декодирования выдает единичный сигнал на tO выход 9 устройства и вычислительный процесс в ЭВМ приостанавливается. Этот же единичный сигнал разрешает прохождение импульсов от генератора 6 через элемент И / на счетный 5 вход счетчика 4. Счетчик Переводится в режим счета, причем за начальную установку принимается значение содержимого счетчика в момент обнаружения ошибки, т.е. номер j-ro блока 20 памяти. На вход 3 устройства новый адрес от ЭВМ не поступает, так как вычислительный процесс приостановлен, поэтому в регистре 1 продолжает

ле суммирование, содержимого ячейки (j-1)-ro блока памяти с ранее накопленной суммой в сумматоре 15 формиру ется код коррекции, содержащий единичную информацию в корректируемых разрядах. Для получения кода слоЕ, не содержащего ошибки, код коррекции необходимо поразрядно суммировать по модулю два с искаженным значением считанного слова. С приходом очередного импульса счета с выхода элемента И 7 в счетчике 4 формируется адрес очередного, т.е. j-ro, блока памяти и происходит обращение к ячейке памяти j-ro блока накопителя 2. Кроме того, адрес j-ro блока памяти сравнивается в блоке 17 сравнения с содержимым регистра 12 по управляющим сигналам, поступающим с генератора 6 через элемент И 7. Поскольку коды сравниваемых слов совпадают, на выходе блока 17 сравнения формируется единичный сигнал, который поступает на коммутатор 14,- Этот

храниться адрес той ячейки j-ro блока- сигнал запрещает прохождение считанпамяти, при обращении к которой обнаружена ошибка. Единичный сигнал с выхода блока 8 декодирования поступает на запрещающий рход элементов И блока 10 и 11, запрещая тем самым прием новой информации в регистры 12 и 13. Таким образом, в регистре 12 в момент обнаружения ошибки и в процессе дальнейшей коррекции хранится адрес j-ro блока памяти, а в ре- гистры 13 - считанное из накопителя 2 слово, в котором обнаружена ошибка.

При коррекции ошибки, независимо от того, вызвано ее появление отка- зом или сбоем, устройство работает следующим образом.

Импульсы, поступающие на счетньй вход счетчика 4 через элемент И 7, обеспечивают формирование адресов (J+1), (j+2)-ro и т.д. до (п+1)-го блоков памяти. После переполнения счетчик обнуляется и далее продолжает считать, выбирая 1,2,..., (j-l)-u блоки,памяти, импульсы с выхода элемента И 7 поступают на блок 17 сравнения, где сравнивается содержимое счетчика 4 и регистра 12, а также на управляющий вход сумматора 15, в котором выполняется поразрядное суммирование по модулю два содержимого одноименных ячеек всех блоков памяти до (j-l)-ro включительно 1 11огле суммирование, содержимого ячейки (j-1)-ro блока памяти с ранее накопленной суммой в сумматоре 15 формируется код коррекции, содержащий единичную информацию в корректируемых разрядах. Для получения кода слоЕ, не содержащего ошибки, код коррекции необходимо поразрядно суммировать по модулю два с искаженным значением считанного слова. С приходом очередного импульса счета с выхода элемента И 7 в счетчике 4 формируется адрес очередного, т.е. j-ro, блока памяти и происходит обращение к ячейке памяти j-ro блока накопителя 2. Кроме того, адрес j-ro блока памяти сравнивается в блоке 17 сравнения с содержимым регистра 12 по управляющим сигналам, поступающим с генератора 6 через элемент И 7. Поскольку коды сравниваемых слов совпадают, на выходе блока 17 сравнения формируется единичный сигнал, который поступает на коммутатор 14,- Этот

сигнал запрещает прохождение считанного слова из j-ro блока накопителя 2 на вход сумматора 15, вместо него на вход сумматора поступает код слова, содержащего ошибку, с выхода регистра 13. В сумматоре 15 и происходит коррекция ошибки путем сумми-. рования кода слова и кода коррекции. Полученное истинное значение слова поступает в блок 8 декодирования, на выходе которого формируется нулевой сигнал. Этот сигнал подается на выход 9 устройства для .организации продолжения вычислительного процесса в ЭВМ, блокирует прохождение импульсов от генератора 6 через элемент И 7 и разрешает прохождение информации через элементы И блоков 10 и. 11, Таким образом, выполняется исправление всех обнаруженных ошибок.

Формула изобретения

Постоянное запоминающее устройство с самоконтролем,содержащее накопитель, адресные входыпервой группы которого подключены к выходу первого регистра, входы которого являются адресными входами первой группы устройства, адресные входы второй группы накопителя подключены к выходам дешифратора, вход которого ключен к выходу счетчика, установочные входы которого являются адресными входами второй группы устройства.

тактовый .вход счетчика подключен к первому входу сумматора по модулю два и к выходу элемента И, первый и второй входы которого подключены соответственно к выходу генератора импульсов и к выходу блока декодирования, вход которого подключен к вь:- ходу сумматора по модулю два и является информационным выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит второй и третий регистры, первый и второй блоки элементов И, блок сравнения и коммутатор , первый информационный вход которого подключен к выходу накопителя и к первому входу второго блока элементов И, второй вход и выход которого подключены соответственно

Редактор А.Шишкина Заказ 7532/54

Составитель С.Шустенко Техред Л.Олейник

Корректор

Тираж 589Подписное

ВНЮШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

855386

к выходу блока декодирования и входу третьего регистра, выход которого подключен к второму информационному входу коммутатора, выход и третий вход которого подключены соответственно к второму входу сумматора по модулю два и выходу блока сравнения, первый вход которого подключен к выходу второго регистра, вход которого подключен к выходу первого блока элементов И, первый вход которого подключен к выходу блока декодирования, второй вход первого блока элементов И подключен к выходу счетчика и второму входу блока сравнения, третий вход которого подключен к выходу элемента И, выход блока декодирования является управляющим выходом .устройства.

10

t5

Корректор М. Демчик,

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении постоянных запоминающих устройств. Цель изобретения - повьппение надежности постоянного запоминающего устройства с самоконтролем. Устройство содержит регистр 1 адреса, накопитель 2, адресньй вход 3, счетчик 4, дешифратор 5, генератор 6 импульсов, элемент И 7, блок 8 декодирования, выход 9, блоки 10 и 11 элементов И, регистры 12 и 13, коммутаторы 14, сумматор 15 по модулю два, выход 16 и блок 17 сравнения. Накопитель содержит несколько блоков, хранящих информацию, и один блок, хранящий суммы по модулю два всех одноименных ячеек информационных блоков. С входа 3 адресный код поступает на регистр 1 (младшая часть) и на счетчик 4 (старшая часть). Дешифратор 5 выбирает блок накопителя 2, к которому происходит обращение. Считанное слос $ (Л 00 ел ел 00 00

| Запоминающее устройство с самоконтролем | 1978 |

|

SU746744A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-01-23—Публикация

1985-09-11—Подача